**RCSL No:**

52-AA1058

**Edition:**

August, 1981

Author:

Villy Hansen

Title:

IML501

Technical Description

### **Keywords:**

RC850, RC855, IML501 Image Load Module, Technical Description.

#### **Abstract:**

This publication is a technical description of an Image Load Module designed for the RC850 display unit.

(46 printed pages).

Copyright © 1981, A/S Regnecentralen af 1979 RC Computer A/S

Printed by A/S Regnecentralen af 1979, Copenhagen

Users of this manual are cautioned that the specifications contained herein are subject to change by RC at any time without prior notice. RC is not responsible for typographical or arithmetic errors which may appear in this manual and shall not be responsible for any damages caused by reliance on any of the materials presented.

| COV. | VIENIS |                              | PAGE |

|------|--------|------------------------------|------|

| 1.   | DESC   | RIPTION                      | 1    |

| 2.   | SPEC   | IFICATIONS                   | 2    |

|      | 2.1    | Performance specifications   | 2    |

|      | 2.2    | Electrical Specifications    | 3    |

|      | 2.3    | Environmental Specifications | 3    |

| 3.   | INSI   | 'ALLATION                    | 4    |

|      | 3.1    | Installation of the Module   | 4    |

|      | 3.2    | Installation of the EPROM's  | 4    |

|      | 3.3    | Strapping Possibilities      | 4    |

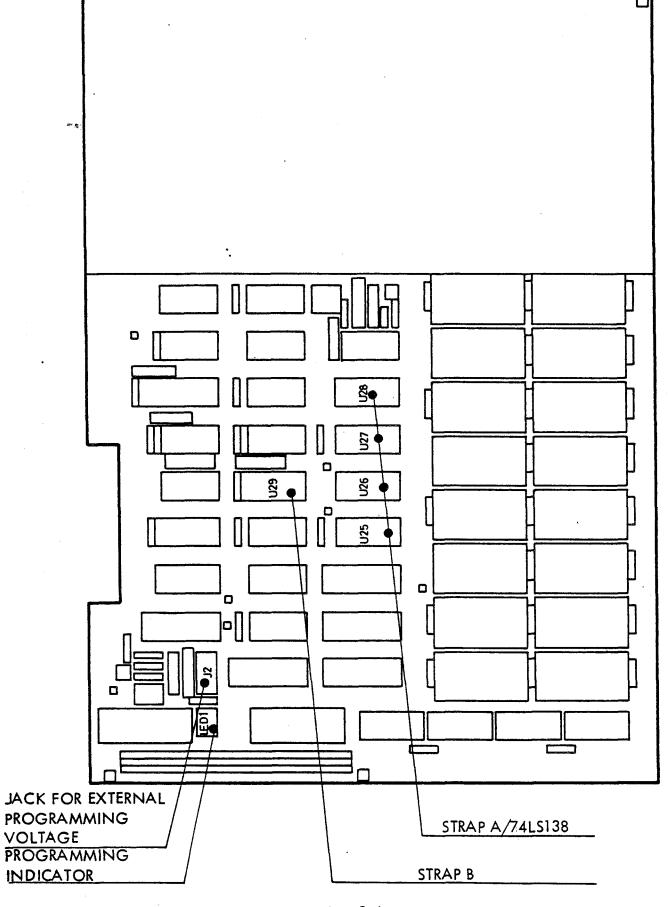

|      |        | Fig. 3.1 IML501 layout       | 6    |

|      |        | Fig. 3.2 IML501 Straps       | 7    |

| 4.   | BLOC   | KDIAGRAM                     | 8    |

|      | Bloc   | kdiagram 1                   |      |

| 5.   | TIMI   | NG DIAGRAMS                  | 9    |

|      | Timi   | ng Diagram 1                 |      |

|      | Timi   | ng Diagram 2                 |      |

|      | Timi   | ng Diagram 3                 | ٠    |

| 6.   | FUNC   | TIONAL DESCRIPTION           | 10   |

|      | 6.1    | EPROM Module Operation       | 10   |

|      |        | 6.1.1 Initialization         | 10   |

|      |        | 6.1.2 Read from EPROM Memory | 11   |

|      |        | 6.1.3 Program EPROM Memory   | 12   |

|      | 6.2    | Timing Generators            | 13   |

|      |        | 6.2.1 Read Timing            | 13   |

|      |        | 6.2.2 Programming Timer      | 14   |

|      | 6.3    | Address Path                 | 14   |

|      | 6.4    | Data Path                    | 15   |

|      | 6.5    | Programming Mode Indicator   | 15   |

|      | 6.6    | FPROM Array                  | 16   |

<u>CONTENTS</u> PAGE

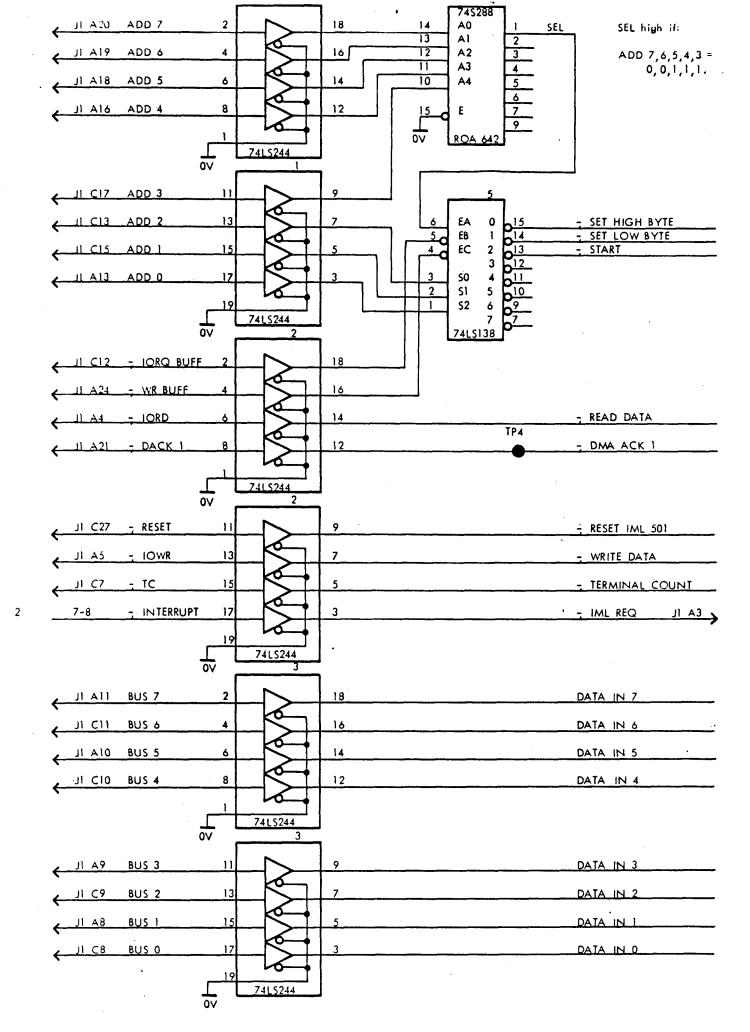

| 7.           | LOGIC DIAGRAMS AND SIGNAL LISTS: |                                         |     |

|--------------|----------------------------------|-----------------------------------------|-----|

|              | Signal List p. 1                 | Dwg. no. A25962                         |     |

|              | Logic Diagram p. 1               | Dwg. no. A14107                         |     |

|              | Signal List p. 2                 | Dwg. no. A14125                         |     |

|              | Logic Diagram p. 2               | Dwg. no. A14108                         |     |

|              | Signal List p. 3                 | Dwg. no. A25963                         |     |

|              | Logic Diagram p. 3               | Dwg. no. A14109                         |     |

|              | Signal List p. 4                 | Dwg. no. A25964                         |     |

|              | Logic Diagram p. 4               | Dwg. no. A14110                         |     |

|              | Signal List p. 5A                | Dwg. no. A25965                         |     |

|              | Logic Diagram p. 5A              | Dwg. no. A14111                         |     |

|              | Signal List p. 5B                | Dwg. no. A25966                         |     |

|              | Logic Diagram p. 5B              | Dwg. no. A14112                         |     |

|              | Signal List p. 6                 | Dwg. no. A25967                         |     |

|              | Logic Diagram p. 6               | Dwg. no. A14113                         |     |

|              | Signal List p. 7                 | Dwg. no. A25968                         |     |

|              | Logic Diagram p. 7               | Dwg. no. A14114                         |     |

|              |                                  |                                         |     |

| 8.           | JACK LIST J1                     | Dwg. no. A14126                         |     |

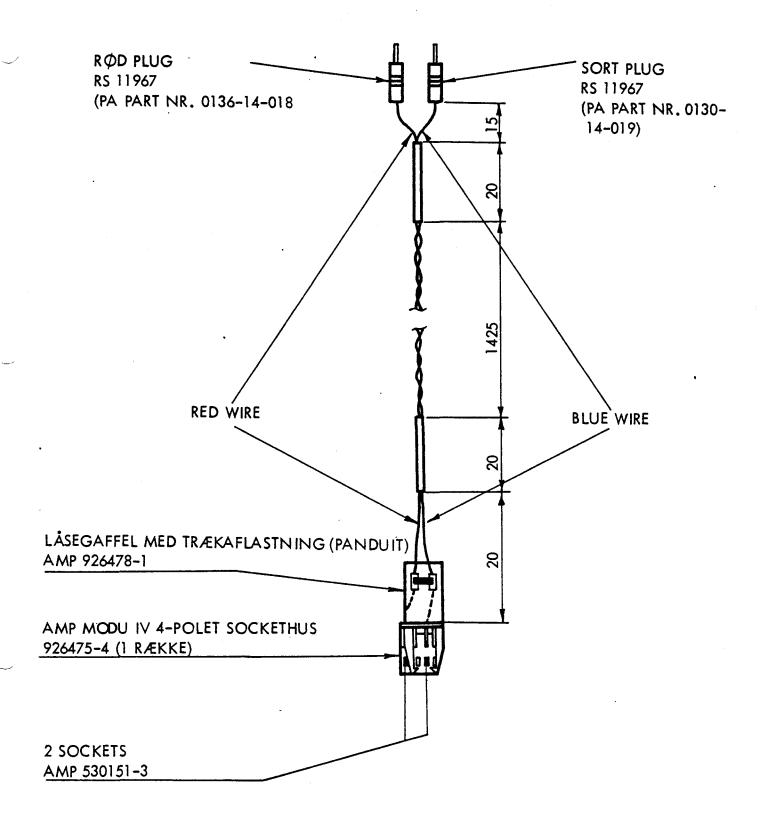

|              | CBL 700                          | • • • • • • • • • • • • • • • • • • • • | 18  |

| <b>3</b> 100 |                                  |                                         |     |

| APP          | ENDICES:                         |                                         | 4.0 |

|              | A. REFERENCES                    |                                         | 19  |

#### 1. DESCRIPTION

The <u>IMage Load</u> module is built around an EPROM array consisting of 16 UV erasable, electrical programmable read only memories, each consisting of 4096 bytes. The total capacity becomes 65536 bytes, each consisting of 8 bits.

The IML module is intended for use in the RC855 stand-alone Display Unit. In the stand-alone version there are no down-load possibilities from external sources (e.g. floppy-disc or transmission lines), instead the IML module is used. During power-up software in the IML module is moved to the ram-memory by means of a bootstrap loader located in MIC504.

The EPROM's located on the IML module may be programmed while located on the printed circuit board, if an external programming voltage is connected to JACK 2.

The EPROM module connects to MIC504 via JACK 1.

1.

#### 2. SPECIFICATIONS

#### 2.

#### 2.1 Performance Specifications

2.1

EPROM TYPE

: Ultraviolet light erasable, electrically programmable readonly memories, with a capacity of 4K x 8 bits. INTEL 2732/2732A or TEXAS 2532 are recommended.

BYTE LENGTH

: 8 bits.

CAPACITY

: 65536 bytes.

READ ACCESS TIME

: Read access time measured from leading edge of the -, IORD pulse to valid data on BUS 0:7, typ. 60 nS.

EPROM data addressed are latched in output register at the leading edge of -, IORD, and approx. 100-150 nS. later the address counter is incremented to next address.

WRITE TIME

: Write time measured from leading edge of -, IOWR pulse to next DMA request, approx. 53.5 mS.

Write data are stored in input register at the trailing edge of -, ICWR and the programming timer is started. Approx. 53.5 mS. later the address counter is incremented and a new DMA request issued.

TRANSFER MODE

: <u>Initialization and start</u> are executed by means of standard I/O instructions:

out 39<sub>H</sub> = set address counter low byte (LS byte)

out 38<sub>H</sub> = set address counter high byte (MS byte), and reset IML501

out 3A<sub>H</sub> = start DMA channel 1 transfer

Data transfer is executed by means of DMA transfers via the DMA controller. Single transfer mode is used.

OPERATIONAL MODES

: Read/verify/write.

PROGRAMMING TIME

: Programming time for the entire array is approx. 60 minutes.

#### 2.2 Electrical Specifications

2.2

SUPPLY VOLTAGE

: + 5V DC - 5%/1A

EXTERNAL

PROGRAMMING VOLTAGE

: 26V <sup>+</sup> 0V5/200mA for INTEL 2732 or TEXAS 2532

22V <sup>+</sup> 0V2/200mA for INTEL 2732A

#### 2.3 Environmental Specifications

2.3

AMBIENT TEMPERATURE

: 10-35°C

RELATIVE HUMIDITY

: 20-80% (non-condensing)

#### 3. INSTALLATION

3.

#### 3.1 Installation of the Module

3.1

The EPROM module is installed in the RC850 display unit in the interface position, which is the position nearest the picture-tube.

CAUTION: THE PCB BOARD MUST NEITHER BE REMOVED FROM NOR

INSERTED IN THE INTERFACE POSITION WHILE + 5V DC

VOLTAGE OR EXTERNAL PROGRAMMING VOLTAGE ARE PRESENT.

INSTALLATION OF THE MODULE OR PROGRAMMING OF THE EPROM'S MUST ONLY TAKE PLACE UNDER THE ASSISTANCE OF AUTHORIZED SERVICE PERSONNEL, SINCE REMOVAL OF DISPLAY UNIT COVER IS REQUIRED.

#### 3.2 Installation of the EPROM's

3.2

EPROM type TEXAS 2532, INTEL 2732/2732A or equivalent types may be mounted in 16 24-pins sockets (see fig. 3.1). Be careful not to bend EPROM pins while mounting the EPROM's. The EPROM types  $\frac{1}{16}$  x 2732A.

### 3.3 Strapping Possibilities

3.3

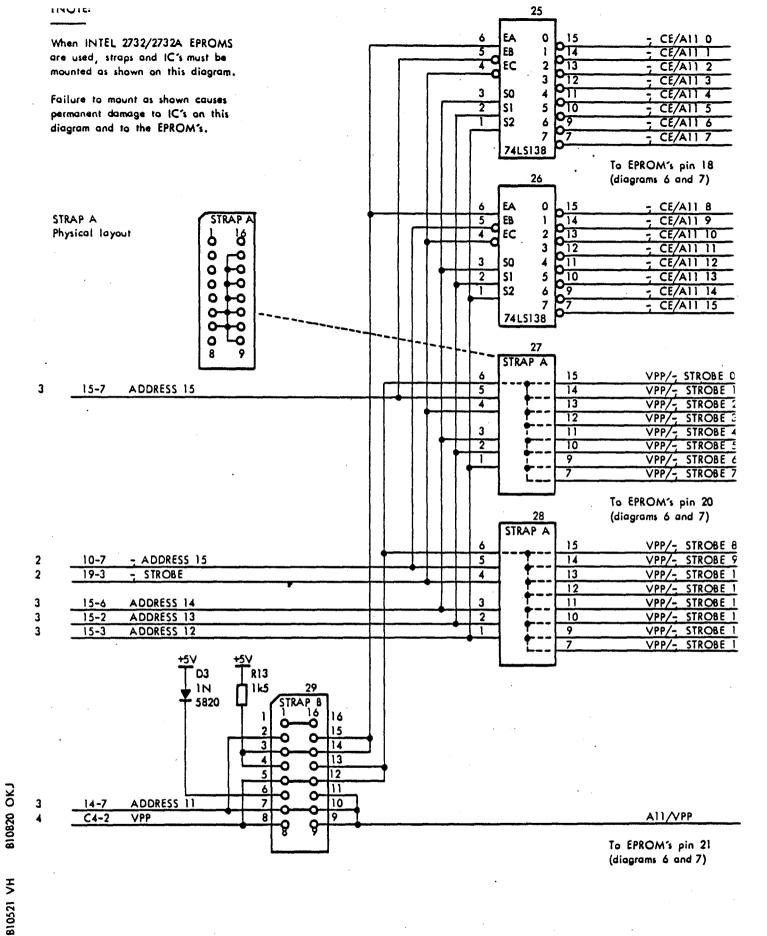

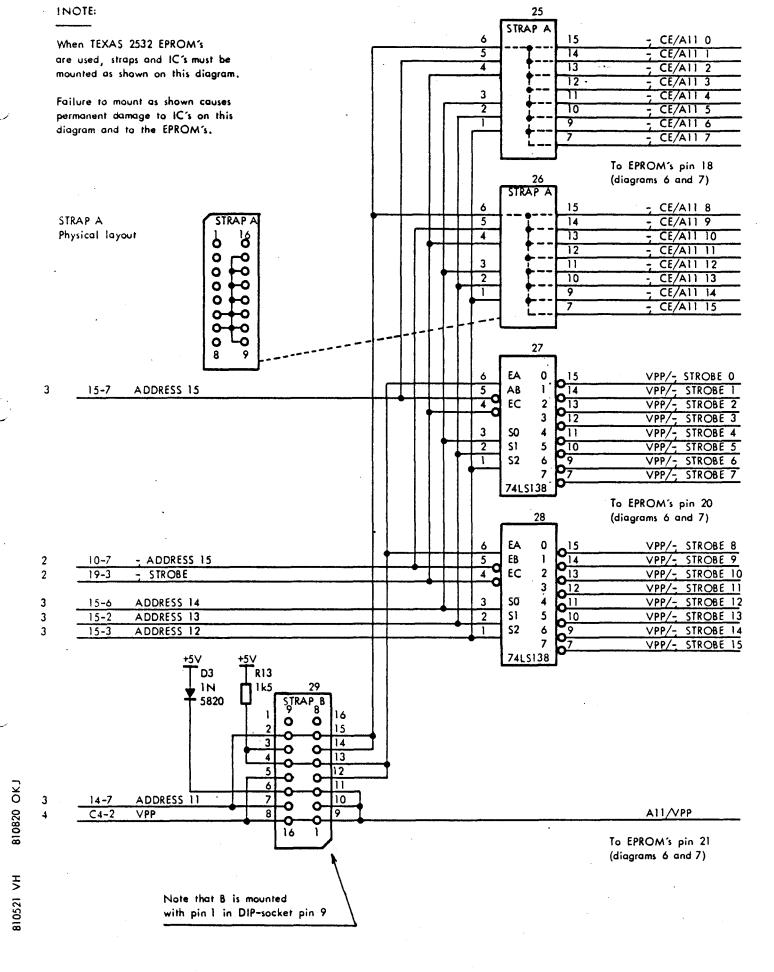

EPROM module is designed to use three types of EPROM's: INTEL 2732/2732A - TEXAS 2532 or equivalent. INTEL and TEXAS EPROM's are, however, not completely compatible, so 5 strap positions have been introduced, Pos. 25, Pos. 26, Pos. 27, Pos. 28, and Pos. 29.

Strapping is executed by means of three strapplatforms and two IC's (74LS138), which are mounted as indicated in fig. 3.2. Refer also to fig.3.1.

To change strapping from INTEL 2732/2732A to TEXAS 2532 or vice versa, do as follows:

- 1. Turn the 16-pins strapplatform B in position 29, 180 degrees.

- 2. Interchange strapplatforms A by IC's 74LS138.

CAUTION: IT IS EMPHASIZED THAT DAMAGE OCCURS TO THE EPROM'S AND THE IC'S 74LS138 IF THE STRAPPING DOES NOT CORRESPOND TO THE EPROM'S USED.

Fig. 3.1 IML501 LAYOUT

| STRAP<br>POSITION | PROGRAM, VERIFY AND<br>READ 2532             | PROGRAM, VERIFY AND<br>READ 2732/2732A |

|-------------------|----------------------------------------------|----------------------------------------|

| 28                | 74LS138                                      | STRAPA                                 |

|                   | POS. 28 PIN 1                                | POS. 28 PIN 1                          |

| 27                | 74LS138                                      | STRAP A                                |

|                   | POS 27 PIN 1                                 | POS. 27 PIN 1                          |

| 26                | STRAP A  O O O O O O  POS. 26 PIN 1          | 74LS138<br>0000000<br>POS. 26 PIN 1    |

| 25                | STRAP A  000000  POS. 25 PIN 1               | 74LS138<br>0000000<br>POS. 25 PIN 1    |

| 29                | STRAP B  O O O O O O O O O O O O O O O O O O | STRAP B  000000  POS. 29 PIN 1         |

Fig. 3.2 IML501 STRAPS

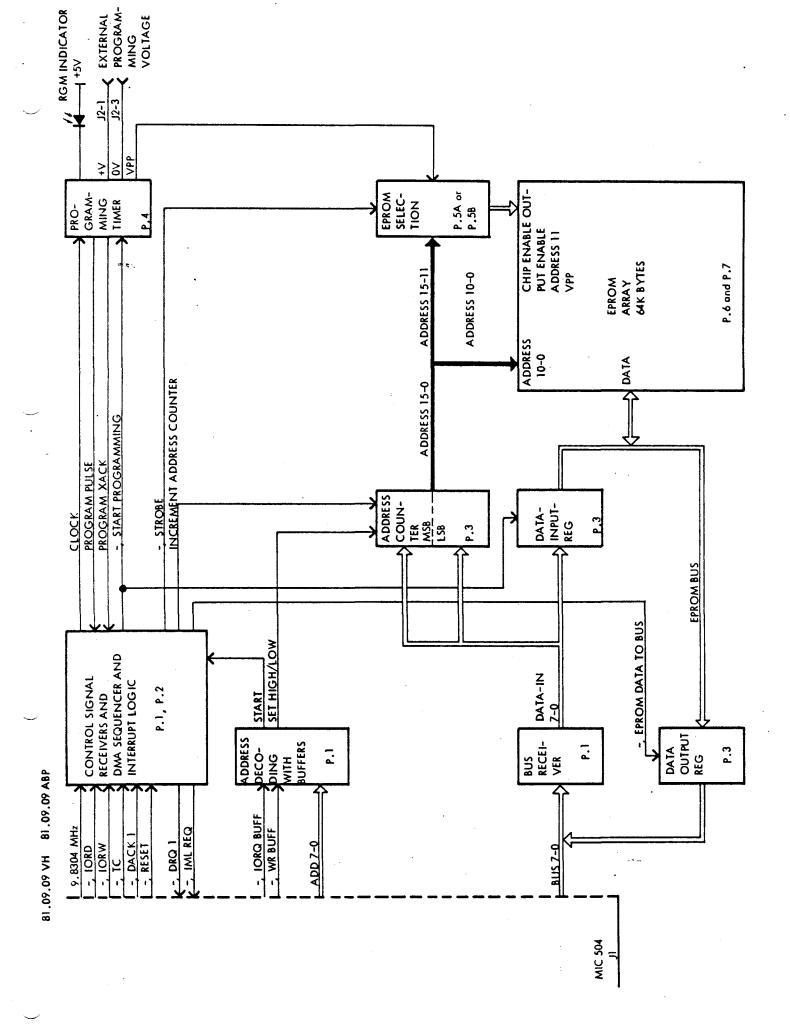

# 4. BLOCK DIAGRAM

3,

The major functional blocks of the EPROM module appear on the block diagram. The numbers in the blocks refer to logic diagram numbers.

# 5. TIMING DIAGRAMS

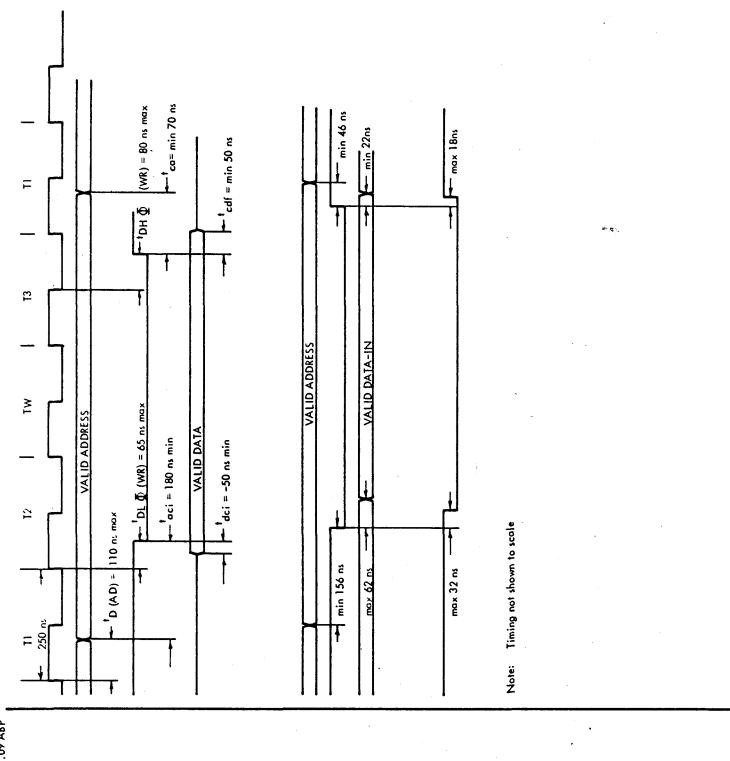

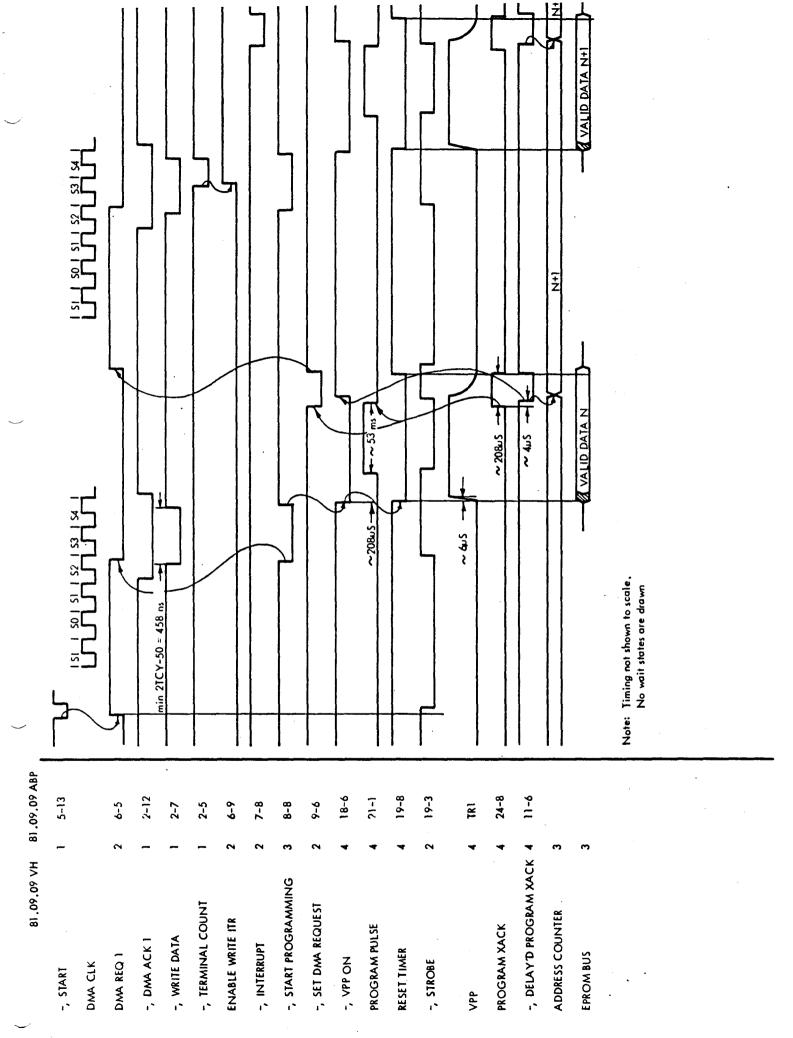

Timing diagram 1 shows standard I/O transfer timing. Timing diagram 2 shows DMA transfer from IML501 to ram-memory, and timing diagram 3 shows DMA transfer from ram-memory to IML501 (programming timing).

5.

81.09.09 VH 81.09.09 ABP

٠, ۱۳

D7:0

CPU ADD 15:0

CLK (Ø)

ADD 7:0

AFTER IML 501 RECEIVERS

AT CPU Z80A INPUTS/OUTPUTS

-, WRITE ADDRESS

DATA-IN 7:0

5-15

-, SET HIGH BYTE or -, SET LOW BYTE

5-14 5-13

or -, START

Note: Timing not shown to scale

All time values in ns

No wait states are drawn

READ TIMING DMA WRITE TRANSFERS

TRANSFER OF TWO BYTES SHOWN

-, READ ITR

-, TERMINAL COUNT

ADDRESS COUNTER

-, START

-, EPROM DATA TO BUS

-, STROBE

-, DMA ACK 1

DAMA REQ 1

DWA CLK

-, READ DATA

INCREMENT ADDRESS COUNTER

81.09.09 VH 81.09.09 ABP

VPP/-, STROBE 0-15

**EPROM BUS 7:0**

**BUS 7:0**

-, CE/All 0-15 or

#### 6. FUNCTIONAL DESCRIPTION

6.

The functional description will refer to block diagram, timing diagrams, and logic diagrams using the abbreviations BD, TD, and LD.

#### 6.1 EPROM Module Operation

6.1

Initialization Read EPROM's Program EPROM's

#### 6.1.1 Initialization (TD1)

6.1.1

Since IML501 uses DMA-transfers via channel 1 of the DMA controller and generates interrupts via the CTC controller channel 3, these two devices must be initialized. Refer to DMA use and CTU use in IML501 REFERENCE MANUAL [1].

IML is set up and started by means of three standard I/O output instructions:

- out  $<39_{

m H}>$  This instruction loads IML501 address counter least significant byte with information from BUS (7:0). Bit 7 is the most significant bit.

- out <38, This instruction terminates all IML501 activity and places IML501 in a well defined state. Besides this the IML501 address counter most significant byte is loaded with the information from BUS (7:0). Bit 7 is the most significant bit.

- out  $<3A_{

m H}>$  This instruction starts DMA-transfer via DMA controller channel 1.

When the software has initialized the DMA controller for write transfer and started IML501, the transfer of information to the ram-memory takes place without the engagement of the Z80-processor. The transfer continues until DMA byte count is zero; at this time the Z80 software is interrupted via CTC channel 3. The DMA is used in Single Transfer Mode, which will ensure one full machine cycle execution between DMA transfers.

The out  $<39_{\rm H}>$ , out  $<38_{\rm H}>$  instructions load IML501 address counter with the start address. The out  $<3A_{\rm H}>$  instruction sets the DMA request FF, which causes the addressed EPROM to be selected and the information to be supplied to the inputs of the data-out register. Upon the arrival of the -, DACK 1 and -, IORD signals from the DMA controller the following sequence of events takes place:

- EPROM data are latched in the data out register. Latching occur as long as the -, EPROM DATA TO BUS signal is at low level.

- Contents of data-out register are gated to BUS (7:0) while the -, EPROM DATA TO BUS signal is at low level.

- EPROM array is deselected while the -, EPROM DATA TO BUS signal is at low level.

- Address counter is incremented by 1 approx. 100 nS. after the leading edge of the -, EPROM DATA TO BUS signal, and at the trailing edge of the signal the addressed EPROM becomes selected.

The above mentioned sequence is repeated for every byte transferred to ram-memory. The DMA request FF remains set until reset by the TERMINAL COUNT pulse from the DMA controller. This pulse is generated when the current byte count register, associated with DMA channel 1, goes to zero. The TERMINAL COUNT pulse causes an interrupt signal to be generated.

#### 6.1.3 Program EPROM Memory (TD3)

6.1.3

During programming of EPROM's all DMA transfers to/from IML501 are usually one byte transfer, since a verification immediately follows the programming of one EPROM cell. The recommended programming procedure is described in the IML501 REFERENCE MANUAL [1].

When the software has initialized the DMA controller for read transfer and started IML501, the transfer of information and the programming of the addressed EPROM cell takes place without the engagement of the Z80 processor. Although it is not recommended, EPROM cells may be programmed without verification cycles in between. The transfer of information and the programming do always continue until DMA byte count is zero. An interrupt is sent to the software via CTC channel 3, when the last byte has been programmed.

The out  $<39_{\rm H}>$ , out  $<38_{\rm H}>$  instructions load IML501 address counter with the start address. The out  $<3A_{\rm H}>$  instruction sets the DMA request FF. Upon the arrival of the -, DACK 1 and -, IOWR signals from the DMA controller the following sequence of events takes place:

- DMA request FF is reset at the leading edge of

START PROGRAMMING signal, which is the "and" of

DACK 1 and -, IOWR.

- Data on BUS (7:0) is loaded into the input register by the trailing edge of the -, START PROGRAMMING signal.

- The programming voltage is switched on.

- The contents of the input register is gated to the inputs of the EPROM array, and the programming timer is started.

- After a delay of approx. 208 uS. a 53.1 mS. wide programming pulse is generated, and the information held in the input register is programmed into the addressed EPROM cell.

- Approx. 4 uS. after the trailing edge of programming pulse the programming voltage is switched off and the address counter is incremented by 1.

- Approx. 208 uS. after the trailing edge of the programming pulse a new DMA-request is issued.

The above mentioned sequence is repeated for every byte programmed, however, when DMA-byte count becomes zero the TERMINAL COUNT pulse will prevent further DMA requests. Instead of a new DMA-request an interrupt pulse is generated when the last byte has been programmed.

#### 6.2 Timing Generators

6.2

# 6.2.1 Read Timing (TD2, LD2, LD3)

6.2.1

Mo read access delay exists. The EPROM's are accessed between the DMA cycles. This gives sufficient time for the addressed EPROM data to settle before the data is latched in the output register.

The first byte to be read is gated to the inputs of the data out register when the START pulse sets the DMA-request FF.

The response to the DMA-request is the ¬, DACK 1 and ¬, IORD signals by means of which the ¬, EPROM DATA TO BUS signal is generated. This signal latches the addressed EPROM information in the output register, strobes this information to BUS (7:0) and disables the EPROM array while the address counter is incremented. When the ¬, EPROM DATA TO BUS signal changes from low to high the EPROM array becomes enabled again, allowing the contents of the addressed EPROM cell to appear at the input lines of the data out register.

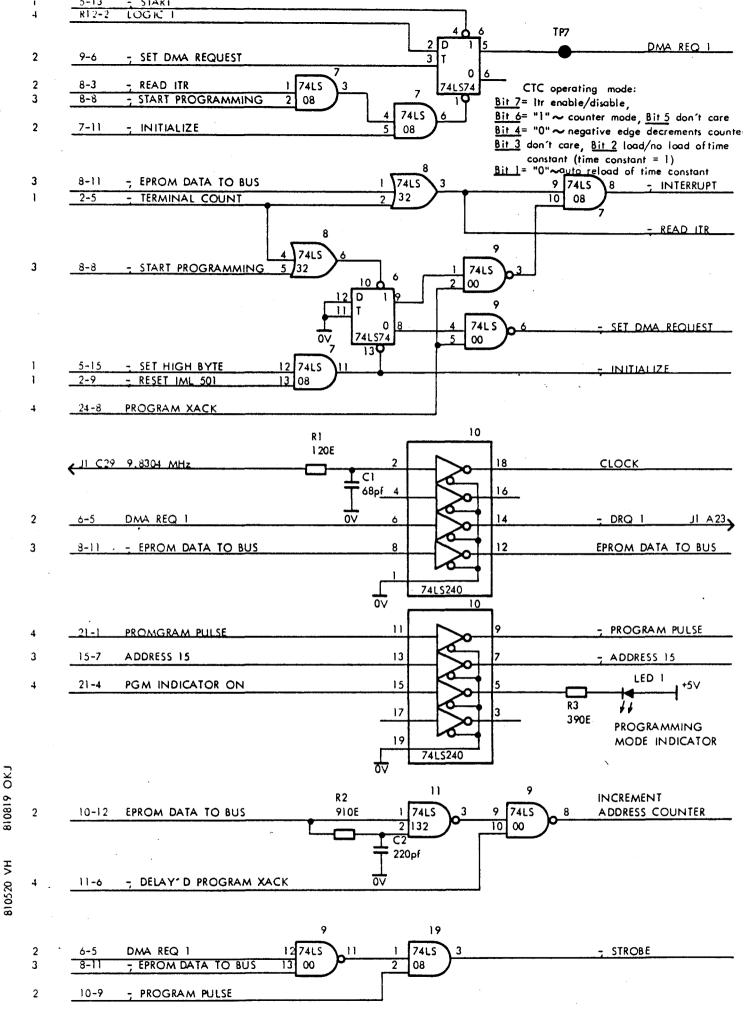

#### 6.2.2 Programming Timer (TD3, LD4)

The programming timer is used during programming of the EPROM's. The timing sequence is initiated when the , START PROGRAMMING signal changes from low to high level. At this time, the programming voltage (VPP) is applied to the EPROM array via the transistor switch, and simultaneously a 20-bits counter is allowed to count as the RESET TIMER signal changes to low level. The counter is incremented by one every 101.7 ns. Approx. 208 us. after the release of the counter a 53.1 ms. wide PROGRAM PULSE is generated. This pulse causes data present in the input register to be programmed into the addressed EPROM location. The programming voltage is switched off at the trailing edge of the PROGRAM pulse and simultaneously the EPROM array is disabled while the address counter is incremented. After further 208 us. of time the timing counter is reset, which terminates the write timing sequence.

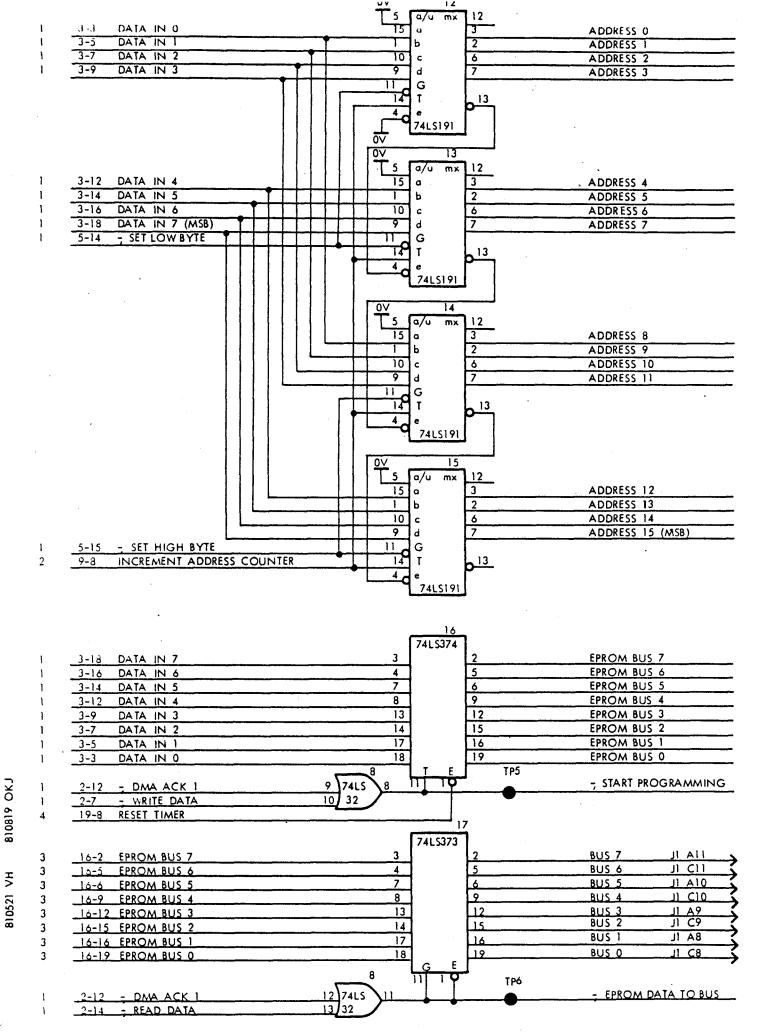

#### 6.3 Address Path (BD, LD3, LD5, LD6, LD7)

As mentioned in section 6.1.1 the address counter is loaded by means of the out  $<39_{\rm H}>$ , out  $<38_{\rm H}>$  instructions.

6. \_3

6.3

ADDRESS bits 15:12 from the address counter are connected to the EPROM selection circuits to select one EPROM out of 16.

ADDRESS bits 11:0 are connected to the address inputs of the EPROM's to select one EPROM location out of 4096 locations. Notice that ADDRESS bit 11 passes strap platforms, which takes into account the pin incompatibility of the 2532 and the 2732/2732A EPROM's.

#### 6.4 Data Path (BD, LD1, LD3, LD6, LD7)

6.4

The BUS (7:0) receiver is a 74LS244 octal line receiver. After the receiver the data lines are named DATA-IN (7:0), and these lines are connected to the input of the address counter and the data input register. The EPROM bus connects the bidirectional information lines from the EPROM array with the outputs of the data in register and the inputs of the data out register. Data stored in the addressed EPROM location are sent via the EPROM bus to the data out register during DMA write transfers. Data held in the input register are sent via the EPROM bus to the addressed EPROM location during DMA read transfers (programming of EPROM's).

#### 6.5 Programming Mode Indicator (LD2, LD4)

6.5

To be able to monitor the programming of the EPROM's, IML501 is equipped with a programming mode indicator, which turns on when the external programming voltage is connected to JACK 2.

The PGM indicator gleams synchronously with the PROGRAM PULSE when programming the EPROM's. By means of a toggle FF every second PROGRAM PULSE produces a flash.

## 6.6 EPROM Array (LD6, LD7)

6.6

The EPROM's in the array may be TEXAS 2532, INTEL 2732/2732A, or PROM's which are equivalent to these types.

<u>CAUTION:</u> THE EPROM TYPES ON THE PCB <u>MUST</u> NEVER BE MIXED.

MOUNT EITHER 16 x 2532 OR 16 x 2732 OR 16 x 2732A.

NOTICE THAT EXTERNAL PROGRAMMING VOLTAGE FOR 2732A IS ONLY 22V.

EXTERNAL PROGRAMMING VOLTAGE FOR 2532 and 2732 is 26V.

.

| •                 |              |                                                                                                                                                                                       |                                                |              |

|-------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|--------------|

| SIGNAL            | DESTINATION  | DESCRIPTION                                                                                                                                                                           |                                                |              |

| -, SET HIGH BYTE  | p. 2<br>p. 3 | Generated during the out <38,2 tion to terminate all IML501 and place the logic in a well state. Besides this the most state of the address counter is with information from BUS (7:0 | activity<br>defined<br>significant<br>s loaded | Designed by  |

| -, SET LOW BYTE   | p. 3         | Generated during the out <39 <sub>H</sub> , tion to load the least significant of the address counter with in from BUS (7:0).                                                         | icant byte                                     | Drawn by     |

| -, START          | p. 2         | Generated during the out <3A <sub>H</sub> ,<br>tion to start DMA transfers be<br>IML501 and display unit RAM me                                                                       | etween                                         | γ            |

| -, READ DATA      | p. 3         | Buffered -, IORD pulse used to IML501 EPROM data during a DM transfer.                                                                                                                |                                                | Dwg. Office  |

| -, DMA ACK 1      | p. 3         | Buffered -, DACK 1 pulse used 1<br>IML501 when it has been grante<br>cycle.                                                                                                           |                                                | Office Check |

| -, RESET IML 501  | p. 2         | Buffered -, RESET signal, which generated during power-up. The places the logic of IML501 in defined state.                                                                           | e signal                                       |              |

| -, WRITE DATA     | p. 3         | Buffered -, IOWR signal used to<br>into IML501 data-in register of<br>read transfer.                                                                                                  |                                                |              |

| -, TERMINAL COUNT | p. 2         | Buffered -, TC signal used to :<br>IML501 when DMA byte count has<br>zero.                                                                                                            |                                                |              |

| -, IML REQ        | J1-A3        | Buffered interrupt request from Refer to -, INTERRUPT signal or                                                                                                                       |                                                |              |

| DATA IN 7:0       | p. 3         | Data/start address received fivia bus receivers.                                                                                                                                      | rom BUS (7:0)                                  |              |

|                   |              |                                                                                                                                                                                       |                                                |              |

|                   |              |                                                                                                                                                                                       |                                                |              |

|                   |              |                                                                                                                                                                                       |                                                |              |

| Unit IML501       |              |                                                                                                                                                                                       |                                                |              |

| Dwg. No.          | Sian         | al List                                                                                                                                                                               | 1                                              |              |

| A25962            |              |                                                                                                                                                                                       |                                                | J            |

IML 501

810819 OKJ

B10519 VH

| SIGNAL                     | DESTINATION    | DESCRIPTION                                                                                                                                                                                                                                                                                                |

|----------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DMA REQ 1                  | p. 2           | DMA request FF. This FF is set when IML501 requires DMA service.                                                                                                                                                                                                                                           |

| -, interrupt               | p. 1           | During read from EPROM's an interrupt signal is generated when the last byte is transferred to the display unit RAM memory.                                                                                                                                                                                |

|                            |                | During programming of EPROM's an interrupt signal is generated when the last requested byte has been programmed into the addressed EPROM location. The interrupt signal is sent to the Z80 processor via CTC device channel 3. The trailing edge of the signal causes the interrupt of the Z80 processor.  |

| ¬ READ ITR                 | p. 2           | -, Read Interrupt.  Generated during read from EPROM's when DMA byte count becomes zero. The signal resets the DMA request FF.                                                                                                                                                                             |

| -, SET DMA REQUEST         | p. 2           | Generated during programming of EPROM's to set the DMA request FF, thus requesting the next byte to be programmed.                                                                                                                                                                                         |

| -, INITIALIZE              | p. 2<br>p. 4   | This signal terminates all IML502 activity and places the logic in a well defined state.                                                                                                                                                                                                                   |

| атоск                      | p. 4           | Buffered 9.8304MHz clock used by the programming timer.                                                                                                                                                                                                                                                    |

| ⇒, DRQ 1                   | J1-A23         | Buffered DMA request from IML501.                                                                                                                                                                                                                                                                          |

| EPROM DATA TO BUS          | p. 2           | Generates the INCREMENT ADDRESS COUNTER signal during read from EPROM's.                                                                                                                                                                                                                                   |

| -, program pulse           | p. 2<br>p. 4   | The program pulse is a 53.1 mS wide pulse used during programming of the EPROM's. Refer also to the description of the programming timer on p. 4.                                                                                                                                                          |

| -, ADDRESS 15              | p. 5A<br>p. 5B | Inverted Address Counter bit 15.                                                                                                                                                                                                                                                                           |

| PROGRAMMING MODE INDICATOR | p. 2           | To be able to monitor the programming of the EPROM's, IML501 is equipped with a programming mode indicator, which turns on when the external programming voltage is connected to JACK 2.  The PGM indicator gleams synchronously with the PROGRAM PULSE when programming the EPROM's. By means of a toggle |

| INCREMENT ADDRESS COUNTER  | p. 3           | FF every second PROGRAM PULSE produces a flash.  This signal increments the address counter by one for every byte transferred between EPROM's and display unit RAM memory.                                                                                                                                 |

| -, STROBE                  | 5A<br>5B       | This signal strobes data from the addressed EPROM location to the EPROM bus during read of EPROM's. During programming of the EPROM's data held in the input register are programmed into the addressed EPROM location by means of this signal.                                                            |

|                            |                |                                                                                                                                                                                                                                                                                                            |

|                            |                |                                                                                                                                                                                                                                                                                                            |

| Unit IML501                |                |                                                                                                                                                                                                                                                                                                            |

| Dwg. No.                   | Signal         | List p. 2                                                                                                                                                                                                                                                                                                  |

| A14125                     |                |                                                                                                                                                                                                                                                                                                            |

IML 501

| •                    | ·                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                         |

|----------------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| SIGNAL               | DESTINATION            | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                      |                         |

|                      |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -                       |

| ADDRESS 15           | p. 2<br>p. 5A<br>p. 5B | Address Counter bits 15:0. I/O output instructions out <38 <sub>H</sub> > and out <39 <sub>H</sub> > load the address counter with the start                                                                                                                                                                                                                                                                                                     | Desig                   |

| ADDRESS 14:11        | p. 5A<br>p. 5B         | address. During DMA write/read transfers the address counter is incremented by one for every byte transferred to/from display unit RAM memory.                                                                                                                                                                                                                                                                                                   | Designed by             |

| ADDRESS 10:0         | p. 6<br>p. 7           |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                         |

| EPROM BUS 7:0        | p. 3<br>p. 6<br>p. 7   | The EPROM bus connects the bidirectional information lines from the EPROM array with the outputs of the data in register and the inputs of the data out register. Data stored in the addressed EPROM location are sent via the EPROM bus to the data out register during DMA write transfers. Data held in the input register are sent via the EPROM bus to the addressed EPROM location during DMA read transfers (programming of the EPROM's). | Drawn by Dws dice Check |

| -, START PROGRAMMING | p. 2<br>p. 4           | This signal starts the programming timer and loads data from the bus into the data in register.                                                                                                                                                                                                                                                                                                                                                  |                         |

| BUS 7:0              | J1<br>p. 1             | Display unit bus 7:0.                                                                                                                                                                                                                                                                                                                                                                                                                            |                         |

| -, EPROM DATA TO BUS | p. 2                   | This signal latches addressed EPROM data in the data out register and gates the data to the diplay unit bus 7:0,                                                                                                                                                                                                                                                                                                                                 |                         |

| ·                    |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                         |

|                      |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                         |

|                      |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                         |

| ·                    |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                         |

| Unit                 |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ] ~                     |

| IML501 Dwg. No.      | Sign                   | al List p. 3                                                                                                                                                                                                                                                                                                                                                                                                                                     |                         |

| A25963               |                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                         |

| SIGNAL                  | DESTINATION    | DESCRIPTION                                                                                                                                                                                                                   |                                           |

|-------------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| -, VPP ON               | p. 4           | Diagram 4 shows the write timin                                                                                                                                                                                               | ig gene-                                  |

| -, DELAY'D PROGRAM XACK | p. 2           | rator, which is used during pro<br>of the EPROM's.                                                                                                                                                                            | gramming                                  |

| RESET TIMER             | p. 4<br>p. 3   | The timing sequence is initiate -, START PROGRAMMING signal chan                                                                                                                                                              | ges from                                  |

| PROGRAM PULSE           | p. 2           | low to high level. At this time gramming voltage is applied to                                                                                                                                                                | the EPROM                                 |

| 416.6 us                | p. 4           | array via the transistor switch simultaneously a 20-bits counter                                                                                                                                                              | r is                                      |

| PROGRAM XACK            | p. 4<br>p. 2   | allowed to count (RESET TIMER a level). Approx. 208 micro secon a 53.1 mS wide PROGRAM PULSE is The programming pulse causes da the input register to be prograthe addressed EPROM location.                                  | ds later<br>generated.<br>ta held in      |

|                         |                | The programming voltage is swit at the trailing edge of program pulse, and simultaneously a 208 second wide PROGRAM XACK pulse rated.                                                                                         | ming<br>micro                             |

|                         | ~ <b>*</b>     | The trailing edge of the program pulse sets the DMA request FF is are further bytes to be program not an interrupt is generated. Counter is also reset at the trailedge of the program xack pulse ending the timing sequence. | f there<br>med, if<br>The timer<br>ailing |

| VPP                     | p. 5A<br>p. 5B | Programming Voltage. For INTEL 1<br>TEXAS 2532 this voltage must be<br>INTEL 2732A this voltage must b                                                                                                                        | 25V. For                                  |

| PROGRAMMING VOLTAGE     | p. 4           | External Programming voltage via 1N 4005.                                                                                                                                                                                     | a diode                                   |

| PGM INDICATOR ON        | .p. 2          | This signal controls the programindicator.                                                                                                                                                                                    | mming mode                                |

| LOGIC 1                 | p. 4<br>p. 2   | LOGIC 1 generator.                                                                                                                                                                                                            |                                           |

|                         |                | •                                                                                                                                                                                                                             |                                           |

| Unit<br>IML501          |                |                                                                                                                                                                                                                               |                                           |

| Dwg. No. A25964         | Signa          | l List                                                                                                                                                                                                                        | p. 4                                      |

Designed by

Drawn by

Dwy. Office Check

IML 501

A14110

810819 OKJ

810521 VH

PROGRAMMING TIMER

p. 4

Circuit Diagram

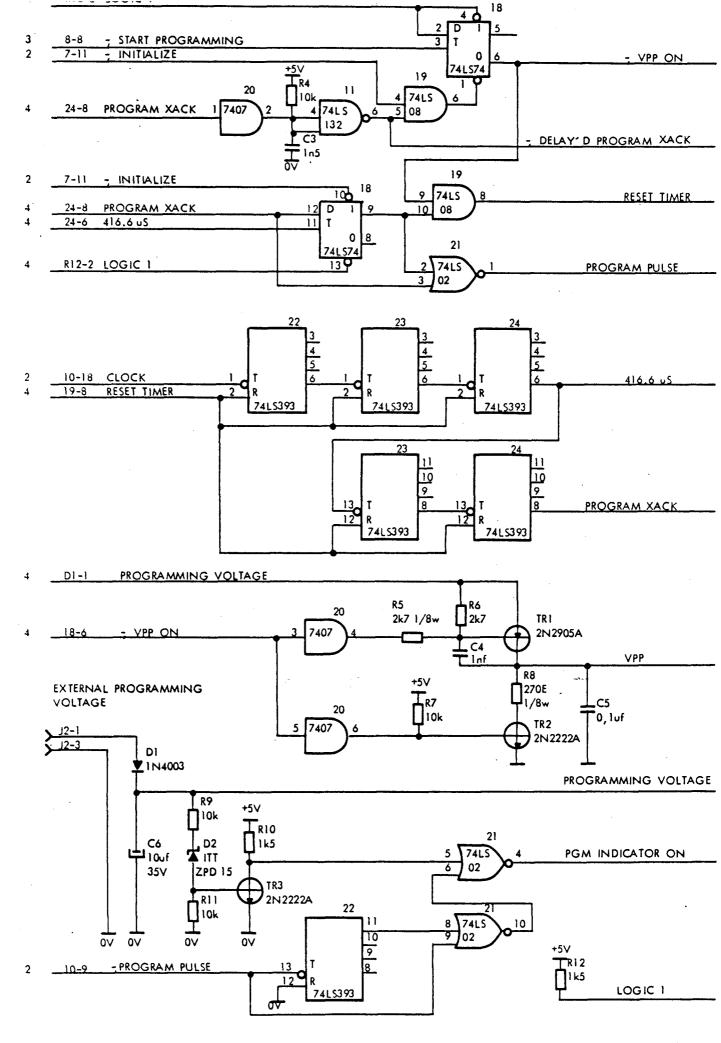

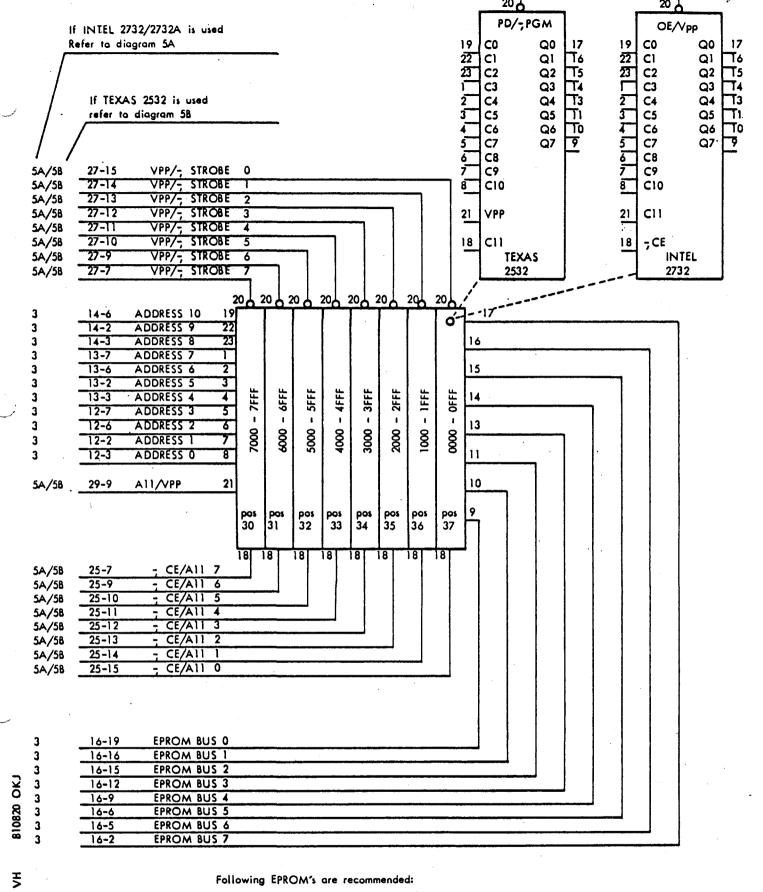

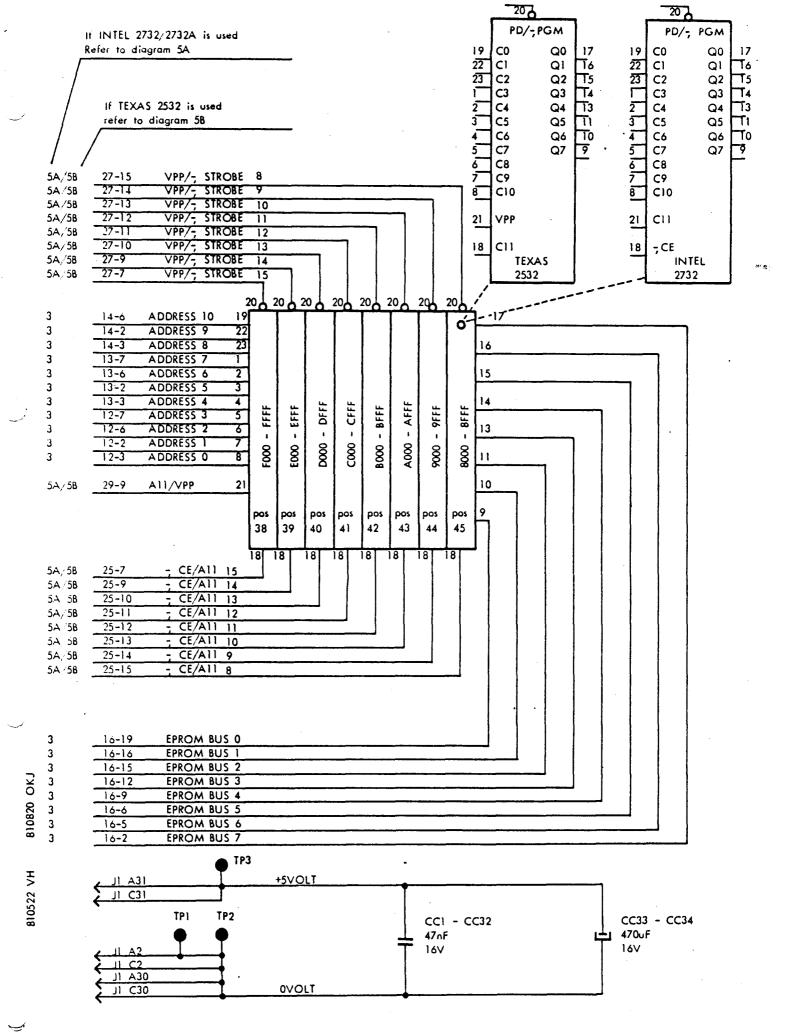

| SIGNAL                               | DESTINATION  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                          | -                    |

|--------------------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| -, CE/A11 0:7<br>-, CE/A11 8:15      | p. 6<br>p. 7 | Diagram 5A shows EPROM selection circuit valid if INTEL 2732/2732A EPROM's are used. , Chip Enable or Address Counter bit 11 to the EPROM array.  These signals are applied to pin 18 of the EPROM's in the array.  If the module is strapped for INTEL 2732/2732A EPROM's, chip enable signal is applied to pin 18 to enable one EPROM out of sixteen EPROM's, CE 0 enables EPROM group 0-4K, -, CE 1 enables EPROM | Designed by Drawn by |

| VPP/-, STROBE 0:7 VPP/-, STROBE 8:15 | p. 6<br>p. 7 | group 4-8K and so on.  If the module is strapped for TEXAS 2532 EPROM's, address counter bit 11 is applied to pin 18.  Programming Voltage or Output Enable signals to pin 20 of the EPROM array.                                                                                                                                                                                                                    | Dw_ lice Check       |

|                                      | ·            | If the module is strapped for INTEL 2732/2732A EPROM's, the programming voltage is applied to pin 20.  If the module is strapped for TEXAS 2532 EPROM's, output enable signal is applied to pin 20, STROBE 0 enables EPROM group 0-4K, -, STROBE 1 enables group 4-8K and so on.                                                                                                                                     |                      |

| A11/VPP                              | p. 6<br>p. 7 | Address Counter bit 11 or Programming Voltage to pin 21 of the EPROM array.  If the module is strapped for INTEL 2732/2732A EPROM's, address counter bit 11 is applied to pin 21.  If the module is strapped for TEXAS 2532 EPROM's, the programming voltage is applied to pin 21.                                                                                                                                   |                      |

|                                      |              |                                                                                                                                                                                                                                                                                                                                                                                                                      |                      |

| Unit IML501                          | Sign         | al List p. 5A                                                                                                                                                                                                                                                                                                                                                                                                        |                      |

|             |                                                                | Designed by                                                 | Drawn by   | Dw. )ffice Check | eck |  | <u> </u>    |

|-------------|----------------------------------------------------------------|-------------------------------------------------------------|------------|------------------|-----|--|-------------|

|             | ion circuit<br>re used.                                        | r signal                                                    |            | ·                |     |  | p. 5B       |

| DESCRIPTION | Diagram 5B shows EPROM select<br>valid if TEXAS 2532 EPROM's a | Refer to signal list p. 5A for destination and description. |            |                  |     |  | al List     |

| DESTINATION |                                                                |                                                             |            |                  |     |  | Sign        |

| SIGNAL      |                                                                |                                                             | म <b>्</b> |                  |     |  | Unit IML501 |

| •    | . •    | `  | •           | ·    |             |      |                   |

|------|--------|----|-------------|------|-------------|------|-------------------|

|      | SIGN   | AL | DESTINATION | •    | DESCRIPTION |      |                   |

|      |        |    |             |      |             |      | ,                 |

|      |        |    |             |      |             |      |                   |

|      | \<br>: | ·  |             | ·    |             | •,   | Designed by       |

|      |        |    |             |      |             |      | Ьу                |

|      |        |    |             |      |             |      | Dr. s.            |

|      |        |    |             |      |             |      | Drawn by          |

|      |        |    |             |      | ٠           |      |                   |

|      |        |    |             |      |             |      | Dw                |

|      |        |    | ·           |      |             | •    | Dwg. Jilice Check |

| •    |        |    |             |      |             | -    | Check             |

| !    |        | ļ  |             |      |             | 1    |                   |

|      |        |    |             |      |             |      |                   |

|      |        |    |             |      |             |      |                   |

| :    |        |    |             |      |             |      |                   |

|      |        |    |             |      |             |      |                   |

|      |        | •  |             |      | • •         |      |                   |

|      |        |    |             |      |             |      |                   |

| ţ    |        | •  | ·           |      |             |      |                   |

|      |        |    |             |      |             |      |                   |

|      |        |    |             | •    |             |      |                   |

|      |        |    |             |      |             |      |                   |

|      |        |    | 7           |      | • .         |      |                   |

| Unit |        | •  |             |      |             |      | Į                 |

| I    | ML501  |    |             |      |             |      |                   |

| Dwg  | , No.  |    | Signal I    | List |             | p. 6 |                   |

| L A  | 25967  |    |             |      |             | 1    | 1                 |

Following EPROM's are recommended:

INTEL 2732, TEXAS 2532 PROGRAMMING VOLTAGE = 25 VOLT.

**INTEL 2732A**

PROGRAMMING VOLTAGE = 21 VOLT.

| SIGNAL                      | • | DESTINATION |         | DESCRIPTION |      |                  |

|-----------------------------|---|-------------|---------|-------------|------|------------------|

|                             |   |             |         |             |      | _                |

| <b>)</b>                    |   | -           |         |             |      | Designed by      |

|                             | · |             |         |             |      |                  |

|                             |   |             |         |             |      | Drawn by         |

|                             | , |             |         |             |      | Dwg.             |

|                             |   | •           |         |             |      | Dwg. Alice Check |

|                             |   | ,           |         |             |      |                  |

|                             |   |             |         |             |      |                  |

| •                           |   |             |         |             |      |                  |

|                             |   |             |         |             | ·    | `                |

|                             |   |             |         |             |      |                  |

|                             |   |             |         |             |      |                  |

|                             |   |             |         |             |      | ۰                |

| Unit IML501 Dwg. No. A25968 |   | Sign        | al List |             | p. 7 | <u>`</u>         |

IML 501

|               | PIN GENERATOR SIGNAL NAME ADDRESS | - 12V • | C 2 0V                                  | C 3 . RESET IN . | C 4 . EXT AEN . | C 5 EXT AD 5TB * | C 6 . DRQ 3 . | C 7 - TC    | C 8 BUS 0 | C 9 BUS 2 | C10 BUS 4 | C11 8US 6 | C12 - IORQ BUF | C13 ADD 2 | C14 CHAIN 3 + | C15 ADD 1   | C16 - RD BUF • | C17 ADD 3 | C18 ADD 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | C19 ADD 14 | C20 ADD 13 | C21 ADD 12 | C22 ADD 11  | C23 ADD 10 | C24 ADD 9 | C25 ADD 8     | C26 - NMI •   |     | C28 - HALT BUF + |     | C30 0V |      |

|---------------|-----------------------------------|---------|-----------------------------------------|------------------|-----------------|------------------|---------------|-------------|-----------|-----------|-----------|-----------|----------------|-----------|---------------|-------------|----------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|------------|-------------|------------|-----------|---------------|---------------|-----|------------------|-----|--------|------|

| CONNECTOR: JI | OR SIGNAL NAME                    |         |                                         |                  |                 |                  |               |             |           |           |           |           |                |           |               |             |                |           | The state of the s |            |            |            |             |            |           |               |               |     | •                |     |        |      |

|               | PIIN GENERATOR                    | 8 1     | B 2                                     | В 3              | 8 4             | 58               | 98            | B 7         | 8 8       | 8 9       | 810       | 118       | 812            | 813       | 814           | 815         | 816            | B17       | 818                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 819        | 820        | 821        | B22         | 823        | B24       | 825           | B26           | 827 | 828              | 829 | 830    | 83}  |

|               | SIGNAL NAME                       | - 12V + | • \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | - IML REQ .      | - IORD          | - IOWR           | -, MEM RD •   | -, MEM WR * | BUS 1     | BUS 3     | 8US 5     | 8US 7     | 1N1 -          | ADD 0     | CHAIN 4 •     | -, MI BUF * | ADD 4          | - WAIT    | ADD 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ADD 6      | ADD 7      | - DACK 1   | -, DACK 3 . |            |           | -, MREQ BUF + | -, RFSH BUF * | CLK | -, HOLD ACK +    | _   |        | + 5V |

|               | PIN GENERATOR<br>ADDRESS          | A 1     | A 2                                     |                  | i               | A 5              | A 6           | A 7         | A 8       | A 9       | A10       | All       | Al2            | A13       | A14           | A15         | Al6            | A17       | A18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | A19        | A20        | A21        | A22         | A23        | A24       | A25           | A26           | A27 | A28              | A29 | A30    | A31  |

. = NOT USED BY IML 501

A. REFERENCES

Α.

[1] IML501 Reference Manual RCSL: 52-AA1057

# **RETURN LETTER**

| litte: IML501, Technical Des                                                                                                                                                                                              | scription              | RCSL No.: | 52-AA 1036 |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------|------------|--|

| A/S Regnecentralen af 1979/RC Computer A/S maintains a continual effort to improve the quality and usefulness of its publications. To do this effectively we need user feedback, your critical evaluation of this manual. |                        |           |            |  |

| Please comment on this manual's completeness, accuracy, organization, usability, and readability:                                                                                                                         |                        |           |            |  |

|                                                                                                                                                                                                                           |                        |           |            |  |

|                                                                                                                                                                                                                           |                        |           |            |  |

|                                                                                                                                                                                                                           |                        |           |            |  |

| Do you find errors in this manua                                                                                                                                                                                          | d? If so, specify by p | age.      |            |  |

|                                                                                                                                                                                                                           |                        |           |            |  |

|                                                                                                                                                                                                                           |                        |           |            |  |

|                                                                                                                                                                                                                           |                        |           |            |  |

| How can this manual be improve                                                                                                                                                                                            | ed?                    |           |            |  |

|                                                                                                                                                                                                                           |                        |           |            |  |

|                                                                                                                                                                                                                           |                        |           |            |  |

|                                                                                                                                                                                                                           |                        |           |            |  |

| Other comments?                                                                                                                                                                                                           |                        |           |            |  |

|                                                                                                                                                                                                                           |                        |           |            |  |

|                                                                                                                                                                                                                           |                        |           |            |  |

|                                                                                                                                                                                                                           |                        |           |            |  |

|                                                                                                                                                                                                                           |                        |           |            |  |

| Name:                                                                                                                                                                                                                     |                        |           |            |  |

| Company:                                                                                                                                                                                                                  |                        |           |            |  |

|                                                                                                                                                                                                                           |                        | Date      | e:         |  |

| • |  |   |

|---|--|---|

|   |  |   |

|   |  |   |

|   |  | • |

Do not tear - Fold here and staple

Fold here

Affix

postage here

Information Department Lautrupbjerg 1 DK-2750 Ballerup Denmark