TECHNICAL MANUAL

RCSL: 51-VB754

Author: Allan Giese

Edited: February 1970

RC 4005

TECHNICAL DESCRIPTION

VOLUME 1

A/S RECENCENTRALEN

Falkoneralle 1

2000 Copenhagen F

## CONTENTS:

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | RCSL NO: |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| RC 4000, HARDWARE ORGANIZATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 44-D6    |

| FECHNICAL CONTROL PANEL AND OPERATOR CONTROL PANEL FOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |

| THE RC 4000 COMPUTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 51-VB644 |

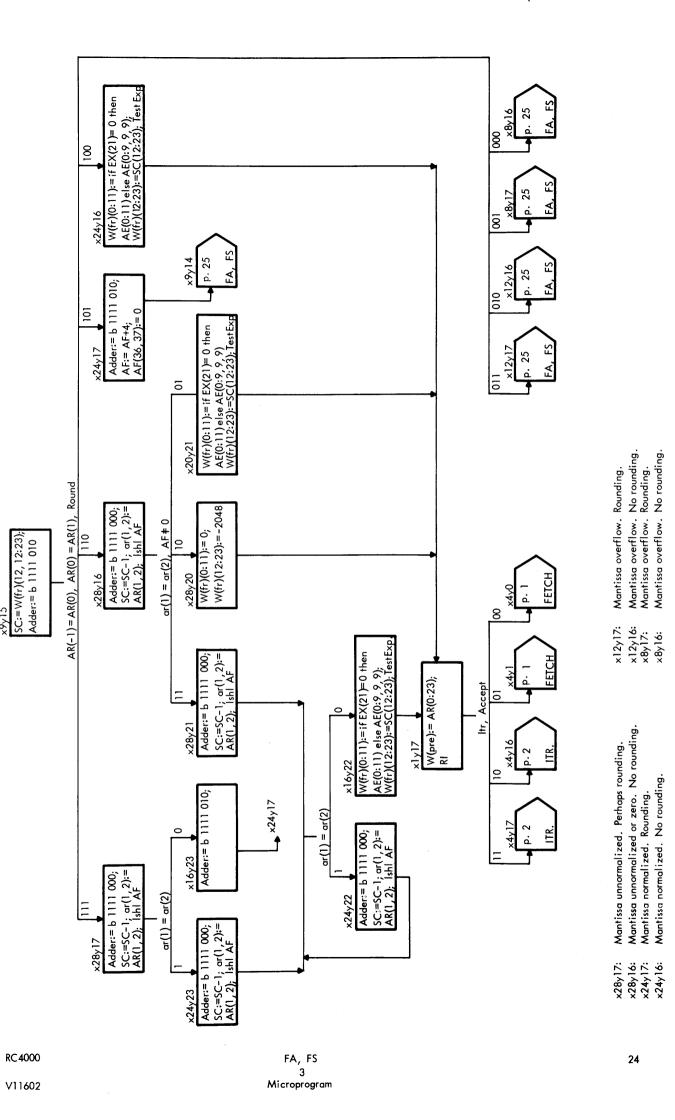

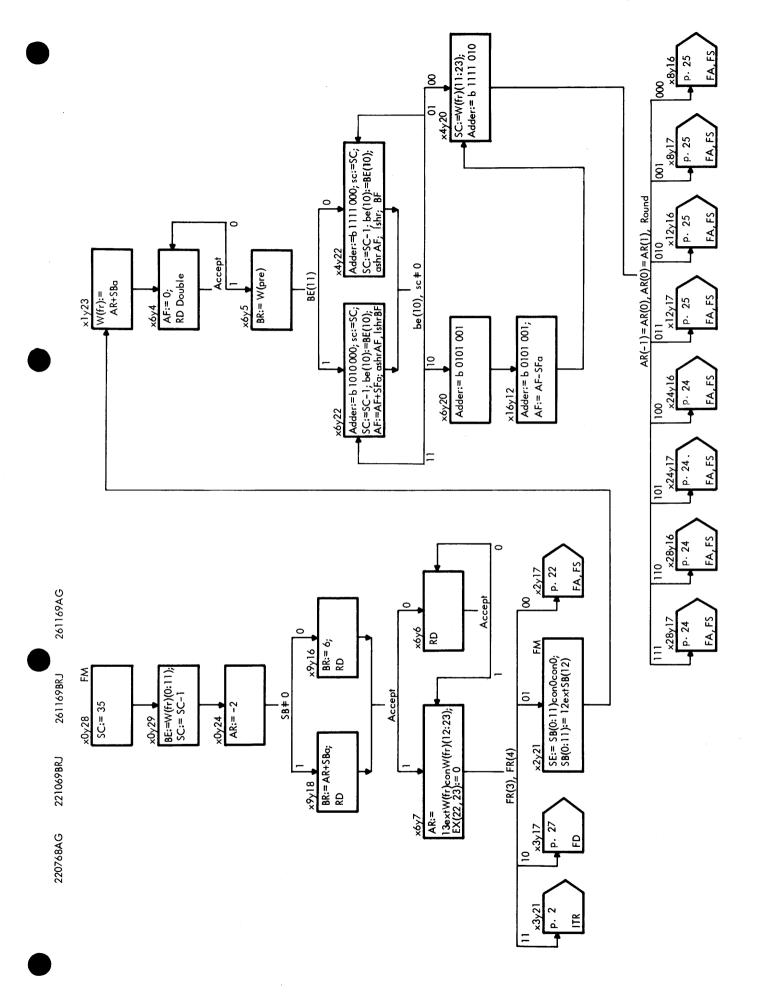

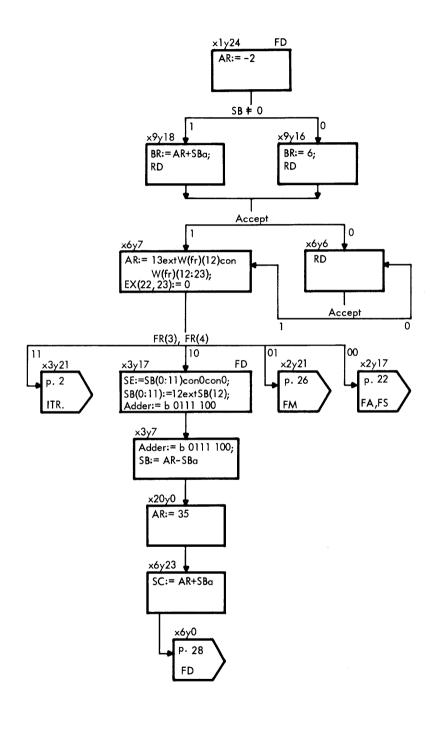

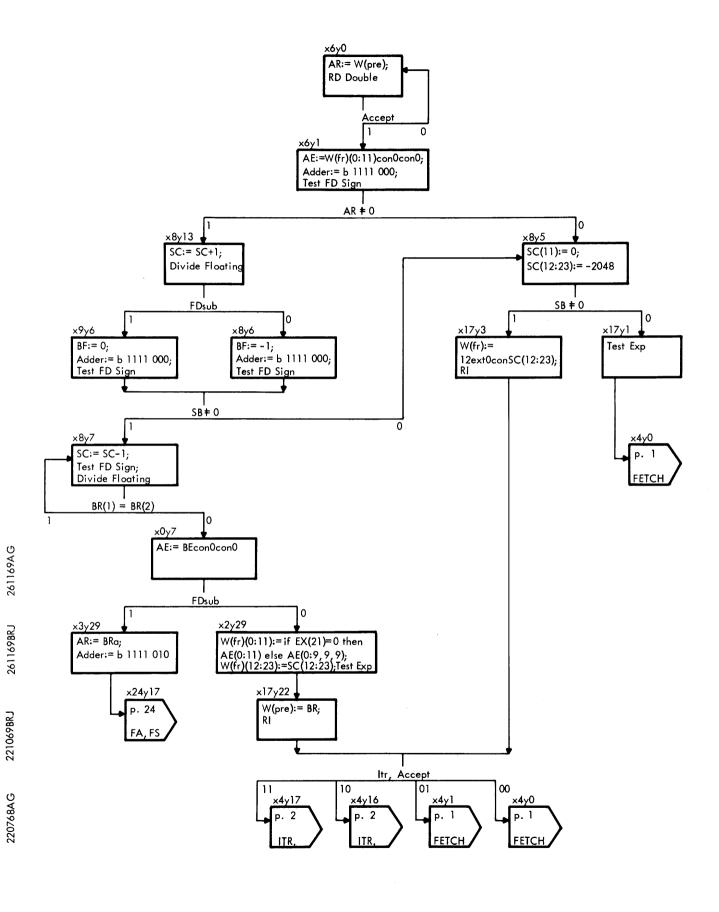

| THE MICROPROGRAM ALGORITHMS FOR THE RC 4000 COMPUTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 51-VB263 |

| THE MICROPROGRAM FOR THE RC 4000 COMPUTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 51-VB698 |

| BIT PATTERN IN THE MICROPROGRAM STORE FOR THE RC 4000 COMPUTER .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 51-VB306 |

| CORE STORE CONTROLLER FOR THE RC 4000 COMPUTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 51-VB357 |

| the property of the state of th | 37-1873  |

RCSL NO: 44-D6 TYPE : Report

AUTHOR: Allan Giese EDITION: October 1968

#### RC 4000, HARDWARE ORGANIZATION

#### Abstract

This paper gives a short description of the hardware organization of the central processor and the input/output system. The maintenance problem is discussed and diagnostic programs are presented. The problems around the selection and use of high - speed integrated circuits are considered together with mounting and wiring techniques.

## CONTENTS

|     |                                                     | page |

|-----|-----------------------------------------------------|------|

| 1.  | CPU ORGANIZATION                                    | 3    |

|     | 1.1. Design Considerations                          | 3    |

|     | 1.2. Register Structure                             | 3    |

| 2.  | INPUT/OUTPUT                                        | 7    |

|     | 2.1. Introduction                                   | 7    |

|     | 2.2. Low-Speed Data Channel                         | 7    |

|     | 2.3. High-Speed Data Channel                        | 7    |

|     | 2.4. Input/Output Control                           | 8    |

| 3.  | DIAGNOSTIC PROGRAMS FOR TESTING OF HARDWARE         | 9    |

|     | 3.1. Introduction                                   | 9    |

|     | 3.2. Diagnostic Programs for the Central Processor  | 9    |

|     | 3.3. Diagnostic Programs for the Peripheral Devices | 9    |

|     | 3.4. Automatic Error Indication                     | 10   |

| 4.  | TECHNOLOGY                                          | 11   |

|     | 4.1. Integrated Circuits                            | 11   |

|     | 4.2. Printed Circuit Boards                         | .11  |

|     | 4. 3. Wiring Technique                              | 12   |

| A [ | DDENINIY                                            | 12   |

#### 1. CPU ORGANIZATION

#### 1.1. Design Considerations

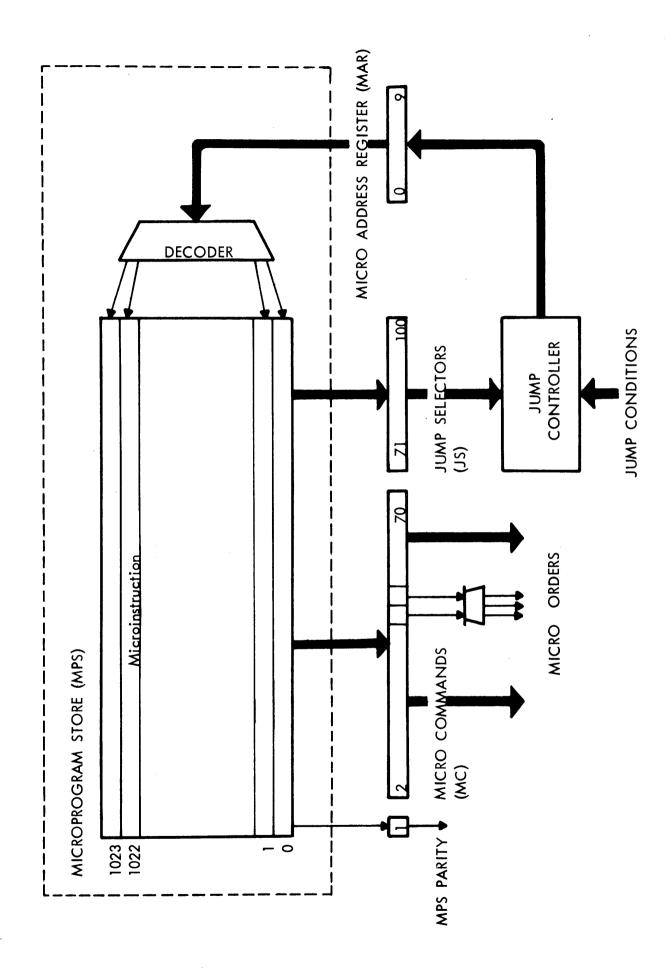

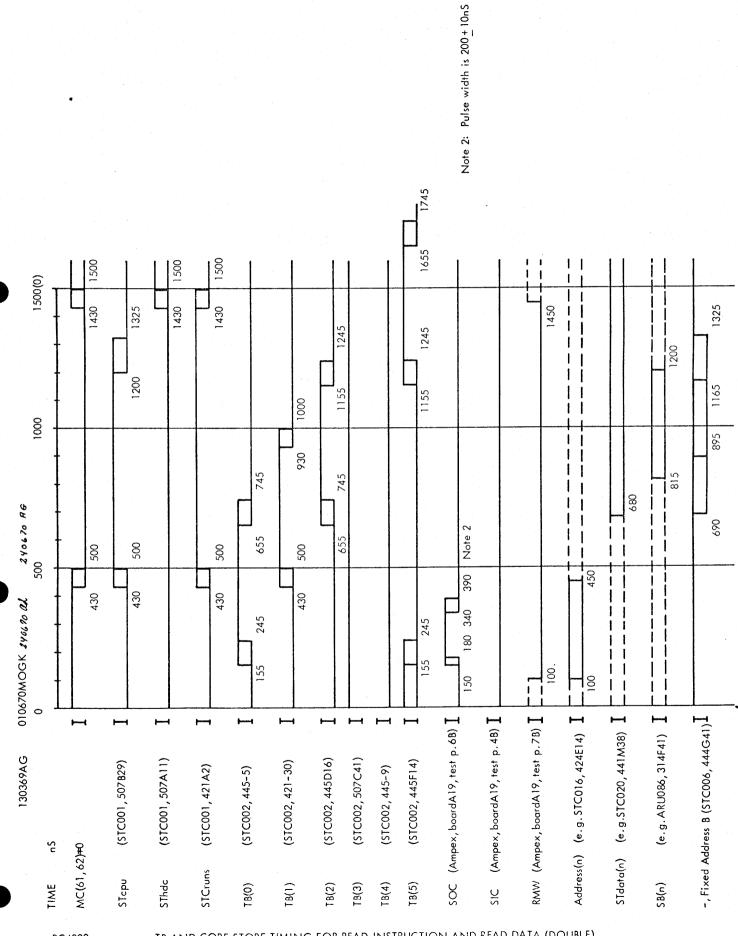

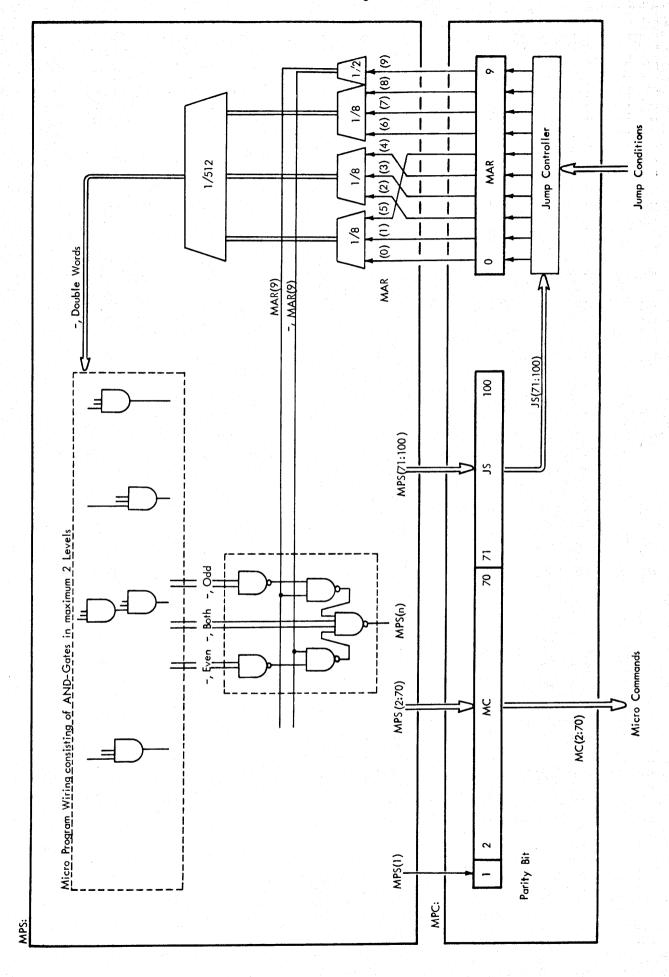

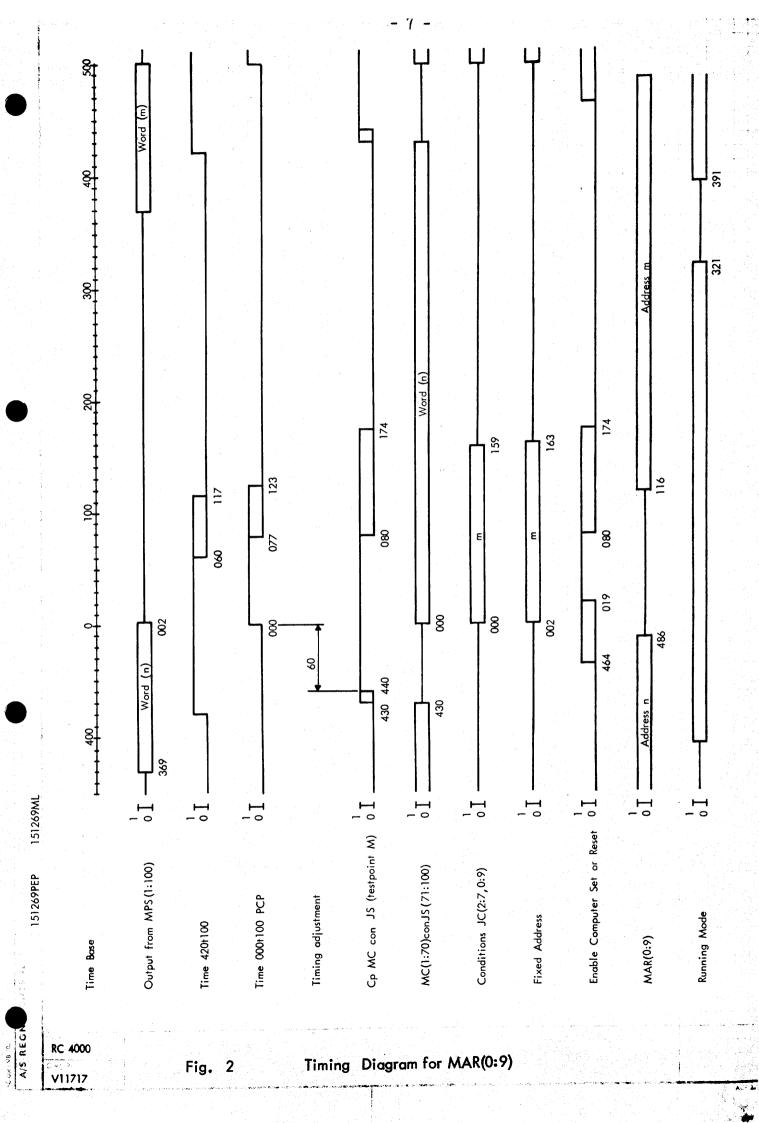

Experience from the design of the GIER computer showed that the control of a computer from a microprogram store containing the microprogram implied a number of advantages such as: flexibility, simple structure, good reliability, and moderate component cost. The disadvantage of such a scheme is that the repetition rate for control signals is limited to the cycle time of the microprogram store. In our case, however, this is not a severe obstacle, since the main factor which influences the instruction execution time is the cycle time for the core store and not that of the microprogram store. The cycle time for the core store is 1500 nanoseconds for read-restore and 2500 nanoseconds for read-modify-write, whereas the cycle time for the microprogram is only 500 nanoseconds. It was therefore decided to control the RC 4000 computer by means of a microprogram.

The microprogram store is organized like a general store having a maximum capacity of 1024 words, each of 100 bits. The store is constructed as a decoding network implemented entirely by means of integrated circuits. For maintenance purposes, the microprogram can be controlled to be executed step by step.

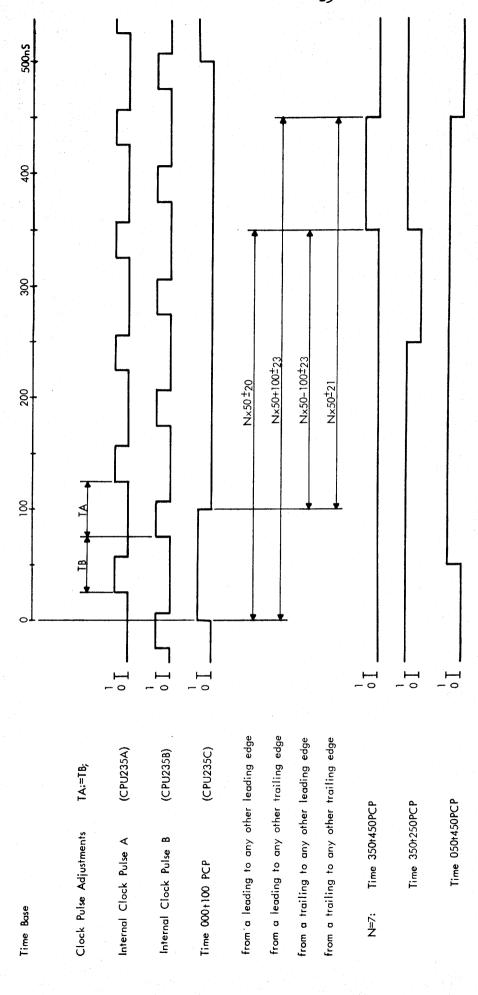

The repetition rate of 500 nanoseconds implies that all the microoperations specified in one microstep are active in this period. Certain of the logical operations, derived from the microoperations, must even within this time interval follow a strictly timed format in order for the computer to execute its instructions. The period of 500 nanoseconds is consequently subdivided into 10 intervals by pulses, having a pulse width of 100 nanoseconds and delayed 50 nanoseconds with respect to each other. The circuit which accomplishes this is a feedback shift register controlled by an oscillator.

## 1.2. Register Structure

The registers of the RC 4000 are grouped around a common bus line system, a configuration which has the advantage that all the registers can transfer data directly to one another. The block diagram, in the appendix, shows not only the data paths between the registers of the Arithmetic Unit, but also the paths to the Core Store Unit, the Interrupt Unit, and the Input/Output Unit. The direction of flow is indicated by means of arrows, and the bit numbers are written on the data paths.

Core Store Data Register; STdata(0:27):

Data communication between the Core Store Unit and the Arithmetic Unit takes place via STdata. The register is logically divided into three groups.

| STdata(O:23)  | Specifies a 24-bit dataword.                               |

|---------------|------------------------------------------------------------|

| STdata(24:26) | Specifies the protection bits.                             |

| STdata(27)    | Specifies the parity bit. (Not shown on the block diagram) |

Core Store Address Register STaddr(6:22):

This register is able to address the maximum core store configuration of 128 K words. STaddr may therefore have fewer bits in actual installations.

Working Registers W O (O:23), W 1 (O:23), W 2 (O:23), W 3 (O:23):

The four working registers, each of 24 bits, can be specified as the result register. Three of the registers (W 1, W 2, and W 3), also function as index registers. The current index register is specified by the instruction format. Since the working registers also act as the first four locations of the core store, it is possible to execute instructions stored in these registers. Like the rest of the storage words each register is supplied with its own protection bits (PB).

# <u>Protection Bits\_PB[O](O:2), PB[1](O:2), PB[2](O:2), PB[3](O:2):</u>

The four 3-bit registers determine together with the protection register, PR, whether the corresponding working register is protected or not. For example, W[O] is protected if PR(PB[O]) equals one, otherwise W[O] is unprotected.

## Protection Register, PR(O:7):

This 8-bit register specifies the protection status for the eight possible values of the protection bits. PR(O) is permanently equal to one.

## Instruction Counter, IC(5:22):

The instruction counter contains the word address of the instruction to be executed. IC is normally increased by one after execution of an instruction, but jump instructions insert explicitly the jump address in IC. A decoding of IC detects when the storage capacity is exceeded.

## Sequential Counter, SC(11:23):

The 13-bit sequential counter is used to determine the number of iterations in, for example the multiply, divide, shift, and normalize instructions. For each iteration, SC is either increased or decreased by one.

In floating-point operations, SC is also used for temporary storage of the resultant exponent.

## Funtion Register FR(O:11):

When a new instruction is fetched from storage, the function part of the instruction, i.e. the twelve left-most bits of the instruction, is assigned to the function register. FR is divided into the following five subfields:

| FR(O:5)   | Specifies 64 basic instructions.                           |

|-----------|------------------------------------------------------------|

| FR(6,7)   | Specifies one of the working registers as result register. |

| FR(8)     | Indirect addressing.                                       |

| FR(9)     | Relative addressing.                                       |

| FR(10,11) | Indexed addressing.                                        |

#### Exception Register, EX(21:23):

An exceptional outcome of an arithmetic instruction or an input/output instruction has the effect of setting the two bits EX(22) and EX(23). Bit EX(21) specifies the precision (significance mode) for floating-point operations. The contents of EX can also be altered by means of the Exception Load instruction.

#### Storage Buffer ,SB(○:23):

When a new instruction is fetched from storage, the address part (the displacement) of the instruction is assigned to the 12 right-most bits of SB. This displacement is then extended to a 24-bit signed integer. The address modifications take then place in SB in order to obtain the effective address for the data word. In consequence of, that the address for the data word is generated in SB, we have also established an address path between the core store address register (STaddr) and SB. Moreover, the 24-bit data word, which is read from the core store, is transferred to SB just as a data word from the Arithmetic Unit to the core store also passes through SB. It is therefore no coincidence that the name for this register is storage buffer.

Either the contents of SB or its complement may be employed as input data for the ADDER circuitry. This makes it possible for the ADDER to perform addition and subtraction.

#### Protect Key, PK(0:2):

Every time a word is read from storage, the protection bits are inserted in PK, and reversely, PK determines the protection bits to be stored.

## Storage Buffer Extension ,SE(O:13):

SE forms together with SB a 38-bit register which is used in floating-point operations to store the mantissa. The two extra bits SE(12,13) play an important role in the rounding calculations.

Either the contents of SE or its complement may be employed as input data for the extended ADDER circuitry.

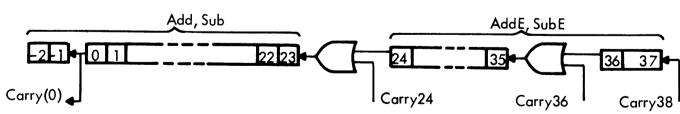

## Adder Circuitry, ADDER(-1:23):

The adder is a parallel adder utilizing extensive carry look-ahead technique. 25 bits are added in typically 120 nanoseconds and 39 bits in 140 nanoseconds.

## $A-Register_AR(-1:23)$ :

AR constitutes together with SB the two data parts to the ADDER circuitry. Bit AR(-1) detects if an overflow situation occurs.

## A-Register Extension AE(0:13):

The combined 38-bit register ARconAE is used in a manner very similar to that of SBconSE.

#### B-Register BR(0:23):

BR is mainly used by multiply, divide, and double length instruction, whereas other instructions only use the register to store temporary results.

If an instruction requires two successive storage words, the address of the second word is held in BR while the first word is fetched from core store. An address path is therefore provided from BR to STaddr.

#### B-Register Extension BE(O:11):

The BR register is extended in order to be able to execute the floating-point division instruction.

#### Display and Manual Control of Bus.

This unit consists of the two registers, DR(-1:23) and DP(O:2) which control BUS(-1:23) and PBUS(O:2), respectively.

#### Interrupt Register IR(O:23):

Each bit in IR is connected to an external or an internal device, which sets the bit in accordance with some specified condition. The left-most bits are assigned highest priority.

## Interrupt Mask IM(O:23):

IM determines whether a given interrupt request should be honoured or not. IM(O) is permanently equal to one.

## Input/Output Unit.

Each input/output device has in principle a 24-bit buffer register plus the two status bits Disconnected and Busy.

#### 2. INPUT/OUTPUT

#### 2.1. Introduction

Experiences have shown that many programs do not use the central processor very effective, because a great percentage of the total computer time is spent, waiting for the input/output devices to complete their operations. This fact has resulted in the development of monitor systems capable of executing several programs in parallel. The advantage of such a scheme is best illustrated by considering two programs A and B. When program A arrives to an input/output instruction, only a short message is sent to the selected device and the monitor will then transfer control to program B. Control is first handed over to program A again, when the external media has terminated. Hence, the central processor does not have to wait for the relatively slow devices. A scheme like this, obviously, requires that each device has its own controller, which can initiate and operate the device independent of the program.

The RC 4000 has two data channels for communication between the central processor and the peripheral devices; one for low-speed devices and one for high-speed devices.

#### 2.2. Low-Speed Data Channel

Slow, character-oriented devices like input/output typewriters, paper tape punches, and paper tape readers are connected to a single low-speed data channel, which communicates directly with the internal working registers. Each device has a separate buffer register of 24 bits, which transmits or receives one character a time to or from the external data medium.

The data channel consists of an input/output bus, with 24 bits for transfer of data to or from device buffers and 6 bits for channel control information. Transfers of data between working register and device buffers take place one at a time under program control. Transfers between buffer registers and external data media, however, are controlled independently by the devices, so that several such transfers can occur simultaneously.

## 2.3. High-Speed Data Channel

Input/output devices such as magnetic drum stores, magnetic disc stores, and magnetic tape stations, which transmit large volumes of data at high speeds, are connected to a single high-speed data channel. This channel provides input/output directly to or from the internal store on a cycle-stealing basis. Program execution and input/output operations occur simultaneously.

Block transfers can take place on several devices at once. A multiplexer switches rapidly among the devices, connecting them whenever they are ready to transfer a complete data word to or from the store.

The method of solving the multi-access competition for core store cycles influences the kind and number of peripheral transfers which may be simultaneously executed. If more than one device is ready for transfer of data, the one having the greatest transfer rate should be first served, since this device will issue its next request before the other. This strategy is adopted for the RC 4000 computer and it is implemented by means of a priority system.

The capacity of the channel is 500,000 words per second.

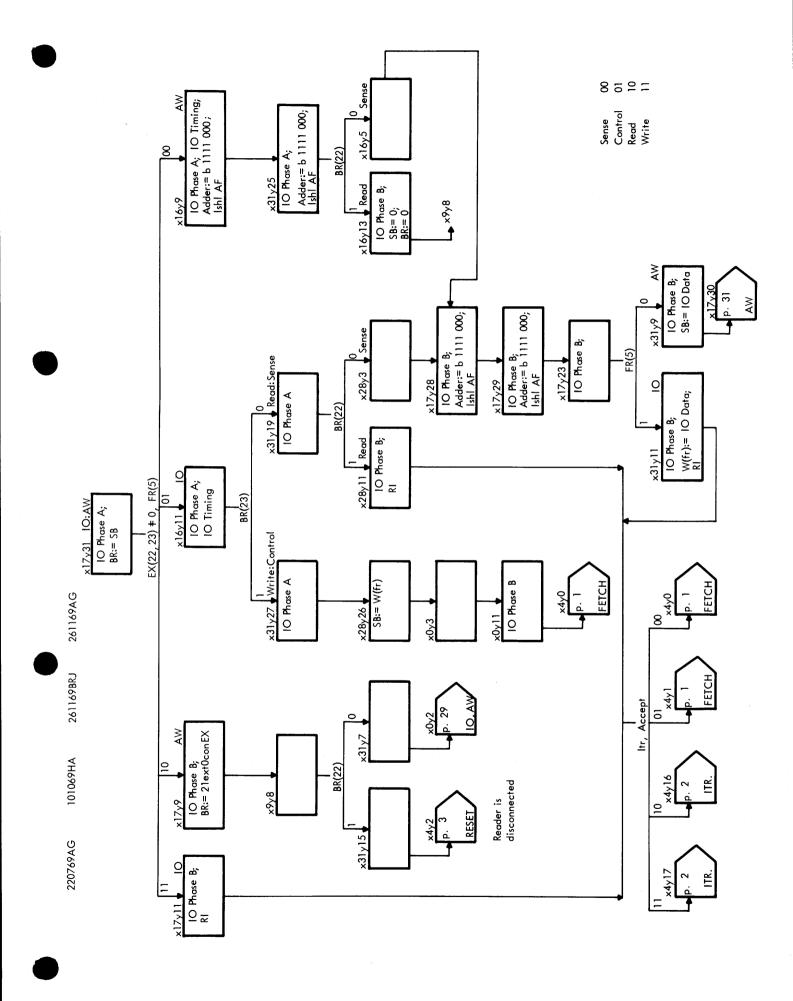

#### 2.4. Input/Output Control

There are four basic input/output commands: read, write, control, and sense. A read command initiates the input of a character to a buffer register. The write and control commands transfer the contents of a working register to a buffer register and initiate output and control operations respectively. A sense command requests a device to transfer a status word from its buffer to a working register. The exception register indicates whether the status word is available; this is the case only after the termination of an operation. The status word contains the last input or output character as well as information about parity errors and other exceptional events.

The high-speed devices use the low-speed channel to transfer commands and addresses of buffer areas in the store. All devices are thus controlled by the standard input/output instruction.

#### 3. DIAGNOSTIC PROGRAMS FOR TESTING OF HARDWARE

#### 3.1. Introduction

Experiences have shown that the use of microelectronic circuits causes maintainability problems, because errors occur so seldom that it is difficult for the service engineers to have sufficient training in error location. Thus, the new systems coupled with older maintenance techniques, will result in machine break-downs for long periods, although of lower frequency. The result is the apparent paradox of more reliable systems being less maintainable. Diagnostic programs have therefore been developed for the RC 4000 computer system.

Many of these programs do not only detect failures, but are also able to isolate them to specific modules. The programs fall into two categories; the first group comprises testprograms for the central processor, whereas the programs which check the peripheral devices constitute the second group. A major difference between the two types of programs is that the testprograms for the peripheral devices are constructed under the assumption that the central processor itself works correctly, but this, of course, can not be taken for granted for programs belonging to category one. The diagnostic programs for the central processor are therefore often referred to as self-check programs.

#### 3.2. Diagnostic Programs for the Central Processor

The self-check programs are oriented towards the checking of hardware failures in microcommands, decoding networks, arithmetic registers, etc. An O.K. message is typed on the operator's typewriter if the outcome of these tests shows that the central processor works correctly. In the case where an error is found, information concerning its nature is typed out whenever possible, but it should be noted that some errors have the effect of destroing the programs completely and thereby prevent further communication between the operator and the self-check programs. Under such circumstances, the operator must turn to the simple diagnostic programs, which can be executed manually from the technical panel.

The self-check programs are usually controlled by the monitor system which then takes care that they are executed at regular intervals. A special version of the program is also provided which can be loaded by means of the autoload key.

Special programs for testing the core store are also available. As an example, one of the programs will generate and write into the core store a worst-case bit pattern after which the program starts to read and check the store word by word. In the event of an error, the erroneous word and its location are indicated.

## 3.3. Diagnostic Programs for the Peripheral Devices

A diagnostic program is constructed for each type of peripheral device. The prime objective for this assembly of programs is to reduce the tedious task of manual error detection and location to a minimum. The programs are controlled from the operator's typewriter in a conversational mode.

The programs check for each device the four input/output commands (sense, control, read, write), the status bits, the local/remote status, plus an additional number of tests dependent on the peripheral device.

If a peripheral device does not complete its operation within a prescribed time, a watch dog timer comes into force and terminates the operation. This action is indicated by a status bit.

#### 3.4. Automatic Error Indication

The computer system is constantly supervised for gross failures even when the diagnostic programs are not running. This is made possible by additional hardware, and concerns the following:

Core Store:

check for parity error.

Read-Only Store:

check for parity error.

Power Supply:

check for current and voltage levels.

Temperature:

check of the temperature in the cabinets.

Blower Assembly:

check for that the fans are running.

#### 4. TECHNOLOGY

#### 4.1. Integrated Circuits

The use of integrated circuits (ICs) has greatly influenced the design and performance of todays computers. These circuits offer advantages such as high reliability, high-speed switching delay time, and a wide operating temperature range. This clearly indicates that ICs were going to be used as the basic logic circuits for the RC 4000 computer.

The circuits, used in RC 4000, are the Transistor-Transistor-Logic integrated circuits (TTL) as supplied by Texas Instruments in Series 74. The characteristics are: noise margins minimum 0.4 volt, typical 1 volt; propagation delay time typical 13 nanoseconds; fan-out 10 for standard gates, 30 for power gates; low impedance at both logic levels with specified good capacity driving capability; only one supply voltage of +5 volts; O to 70 degrees centigrade operating range; voltage swing minimum 2 volts; power dissipation typically 10 mW per gate; 14- or 16-lead plastic dual-inline package. Integrated circuits from the compatible Series 74H, characterized by a propagation delay time of only 6 nanoseconds, have been employed where speed is of paramount importance, as for example in the adder circuitry.

The Series 74 comprise a number of different circuits from which we have chosen: NAND-gates having 2, 4, and 8 inputs, the 4-input power NAND-gate, plus the 2-wide 2-input AND -OR-INVERT gate, and the 4-wide 2-input AND-OR-INVERT gate. Two of the Series bistable elements are employed, namely the J-K flip-flop and the D-type flip-flop both of which are edge-triggered. A 4-bit binary adder is also used.

Special circuit functions, for example line drivers, level converters etc., which are not available as ICs have been constructed from discrete components.

#### 4.2. Printed Circuit Boards

The ICs are mounted on dual-sided printed circuit boards, 11×14.7 cm, by soldering technique. The boards are provided with a 41-pin connector and test points for almost all output signals. The latter facilitates the error location on the board.

A total number of approximately 65 different board types are used for the implementation of the entire computer system. Several considerations have influenced the partitioning of the logic to the various board types. A small number of boards have the advantage of minimizing the spare part problem;

but on the other hand, too few board types imply that an excessive number of boards are necessary to construct even a simple unit. Another problem is that the physical distance between the sending and the receiving IC increases with the total number of boards used in the system, and this increased wire length may lead to severe noise problems and signal delays.

#### 4.3. Wiring Technique

The interconnection between the boards is done by means of ordinary backplane wiring. It was soon realized that the number of connections for the central processor (500 boards) would exceed 10,000 clearly indicating that some sort of automatic data processing had to be done. We, therefore, decided to make a programming system, which covers the following two principal areas:

- 1) From the logic diagrams and a list over the number of used boards, supplied by the designer, the program will analyze all interconnections between the boards, and then assign a position number to each board in the rack. The program cannot produce an optimal solution because of the almost infinite number of possible combinations; but the solutions have proved to be satisfactory.

- 2) After the boards have been positioned, the program produces the wiring lists. These lists contain information about the addresses (i.e. the position- and pin-number of the terminal) to be interconnected and the necessary wire-length.

The programming system also incorporates very useful design and checking facilities.

#### APPENDIX

RC 4000

REGISTER STRUCTURE

V 10690

RCSL: 51-VB644

Author: Allan Giese

Edited: December 1969

TECHNICAL CONTROL PANEL

AND

OPERATOR CONTROL PANEL

FOR

THE RC 4000 COMPUTER

A/S RECNECENTRALEN

Falkoneralle 1

2000 Copenhagen F

## CONTENTS:

|    |       |                                               | page |

|----|-------|-----------------------------------------------|------|

| 1. | OPERA | ATOR CONTROL PANEL                            | 3    |

|    |       |                                               |      |

| 2. | TECHN | IICAL CONTROL PANEL                           | 6    |

|    | 2.1.  | Control Panel Controls and Indicators         | 6    |

|    | 2.2.  | Alter and Display Registers                   | 11   |

|    | 2.3.  | Execute Program Instruction by Instruction    | 11   |

|    | 2.4.  | Execute the Microprogram Micro Instruction by |      |

|    |       | Micro Instruction                             | 12   |

|    | 2.5.  | Read a Word from Storage                      | 12   |

|    | 2.6.  | Insert or Modify a Word in Storage            | 13   |

|    | 2.7.  | Insert a Word in IM Register                  | 13   |

|    | _     | Clear Selected Bits in IR register            |      |

This paper serves as an introduction for manual control of the RC 4000 Computer. The control is exercised by means of keys and pushbuttons on either the Operator Control Panel or on the Technical Control Panel. Visual indications of the machine status and the contents of registers are also given.

#### 1. OPERATOR CONTROL PANEL

CPU POWER ON indicator

Green light indicates that all power supplies for the central processor function correctly.

EMERGENCY BREAK

When this knob is pulled, all power supplies are instantaneously disconnected.

OPERATOR CONTROL ON/OFF

switch

With this key-operated switch in position OFF, the pushbuttons on the operator's panel are disabled. With the key in position ON and if at the same time the Technical Control Panel is disabled (i.e. the MODE SELECTOR switch on the Technical Control Panel is in position NORMAL), then the three pushbuttons RESET, START, and AUTOLOAD will function normally.

OPERATOR MODE indicator

Green light indicates that the OPERATOR CONTROL and the MODE SELECTOR keys are in positions ON and NORMAL, respectively. Moreover, the power supplies for the central processor must work satisfactorily.

RESET pushbutton Pressing this button interrupts the program in progress. Thereafter, the return address is stored in storage word 10, and the computer is set in Monitor Mode with the interrupt system disabled. The computer remains in this reset state indicated by red light in the indicator RESET MODE, until the operator presses either the START pushbutton or the AUTOLOAD pushbutton.

The program will not enter the reset situation if an interrupt request is being served and at the same time the interrupt start address erroneously points at a non-existing core store location. This situation is indicated by no light in the CPU RUNNING indicator.

START pushbutton

When this pushbutton is pressed, the instruction counter is set to an address kept in storage word 14, after which the fetch cycle is initiated. The START pushbutton has no effect, unless the machine is in the reset state.

AUTOLOAD pushbutton

The autoload facility is used to initiate a boothstrapping routine that loads a program into the internal store from device number 0 (normally the paper tape reader). The AUTOLOAD pushbutton has no effect, unless the machine is in the reset state.

CPU RUNNING indicator

Green light indicates that the Technical Control Panel is switched off (MODE SELECTOR key in position NORMAL) and that the computer has executed a fetch cycle, i.e. an instruction has been fetched to be executed, within the last 200 milliseconds.

RESET MODE indicator

Red light indicates that the computer is in reset state waiting for the operator to depress either the START or the AUTOLOAD pushbutton

CPU PARITY ERROR indicator

Red light indicates that the computer has been stopped due to a parity failure in core store or microprogram store. The two types of errors can be distinguished by indicators on the Technical Control Panel.

#### 2. TECHNICAL CONTROL PANEL

This panel is located behind the left-hand front cover of the central processor and it is mainly intended for control of the RC 4000 Computer during maintenance periods.

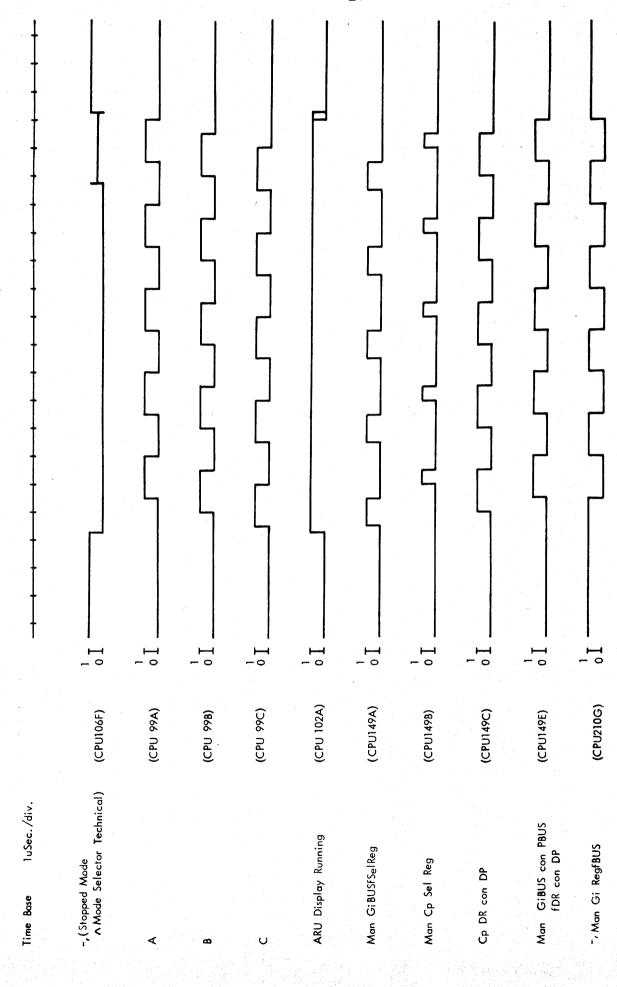

The pushbuttons on the panel are all inoperative when the MODE SELECTOR switch is in position NORMAL (Normal Mode), but turning the key to TECHNICAL position (Technical Mode) makes it possible for the operator to control and inspect the status of the computer.

Normally, the microprogram is executed and the computer is said to be in Running Mode. The opposite to Running Mode is called Stopped Mode in which case the microprogram is stopped.

Besides the Normal Mode and Running Mode (and their corresponding opposite modes) we do have two more modes, which are also opposite to one another, namely Computer Mode and Manual Mode. In Computer Mode, the next micro address is generated by the microprogram; in Manual Mode, the next micro address may be inserted manually by means of pushbuttons.

A complete list for the modes is therefore:

Normal Mode

Technical Mode

Running Mode

Stopped Mode

Computer Mode

Manual Mode

#### 2.1. Control Panel Controls and Indicators

The following list gives a detailed description of the controls and indicators on the Technical Control Panel. If nothing else is explicitly stated, an indicator lamp lights to denote the presence of a binary one.

MODE SELECTOR

NORMAL/TECHNICAL

switch

With this key-operated switch in position NORMAL, all pushbuttons on the Technical Control Panel are disabled, and the computer is automatically operating in the following modes:

- 1. Normal Mode:

- 2. Running Mode: and

- 3. Computer Mode.

It is only possible to remove the key from the lock when the key is in position NORMAL.

When the switch is turned to TECHNICAL position, all pushbuttons function normally, and the computer operates in Technical Mode. The Operator Console is disabled in this mode.

CONTINUE pushbutton

Pressing this button sets the computer in Running Mode: i.e. the microprogram is executed.

SINGLE INSTRUCTION pushbutton

When this pushbutton is pressed, the computer stops after an instruction has been fetched (fetched cycle) but before it is executed (execute cycle). The contents of the function register (FR), the storage buffer (SB), and the instruction counter (IC) equal:

FR: operation byte.

SB: address byte extended to a 24-bit integer.

IC: address of the next consecutive instruction.

> For jump and skip instructions the next instruction is not necessarily the consecutive instruction.

If SINGLE INSTRUCTION is pressed repeatedly, the computer steps through the program one instruction at a time.

If the microprogram is executing an interrupt request and if the start address of the interruption program erroneously points at a non-existing core store loaction, the microprogram will not be stopped by depressing the SINGLE INSTRUCTION pushbutton.

pushbutton

SINGLE MICRO INSTRUCTION When this pushbutton is pressed, the computer stops after each micro instruction and Stopped Mode is set. If SINGLE MICRO INSTRUCTION is pressed repeatedly, the computer steps through the microprogram one micro instruction at a time, so that the contents of registers can be observed in each step.

> Note that a step by step execution of the microprogram will not result in an instruction exception (IR(0)=1) in two cases, namely:

- the core store address exceeds the core store capacity: and

- 2. an unprotected program jumps to a protected location.

MAR COMPUTER CONTROLLED pushbutton

Pressing this pushbutton stops the computer when the current micro instruction is completed and sets the computer in Stopped Mode and Computer Mode.

MAR MANUAL CONTROLLED pushbutton

Pressing this pushbutton sets the computer in Manual Mode and in Stopped Mode.

JUMP SELECTOR REGISTER indicators

Indicate the contents of the 30-bit JS register.

MICRO COMMAND REGISTER indicators

Indicate the contents of the 69-bit MC register.

MICRO ADDRESS REGISTER pushbuttons and indicators

Indicate the contents of the 10-bit micro address to be executed. The micro address can be manually loaded by means of the pushbuttons below the indicators when the computer is in Stopped Mode and Manual Mode.

NORMAL MODE indicator

The indicator lights when the computer is in Normal Mode. The light is out in Technical Mode.

RUNNING MODE indicator

The indicator lights when the computer is in Running Mode. The light is out in Stopped Mode.

MANUAL MODE indicator

The indicator lights when the computer is in Manual Mode. The light is out in Computer Mode.

MONITOR MODE indicator

The indicator lights when the computer is in Monitor Mode. The light is out in Task Mode.

MPS CONTROL ON pushbutton

When this pushbutton is pressed, every word read from the microprogram store is checked against parity error.

Switching the Mode Selector key to Normal position causes the MPS control to be set.

MPS CONTROL OFF pushbutton

When this pushbutton is pressed, no parity check is performed on the microprogram store. The button has also the effect of erasing a possible MPS error.

MPS CONTROL indicator

The indicator lights when the microprogram is checked against parity error.

MPS ERROR indicator

In the event of a parity error caused by the microprogram store, the computer will stop at once and the indicator will light.

CORE STORE CONTROL ON pushbutton

When this pushbutton is pressed, every word read from the core store is checked against parity error.

Switching the Mode Selector key to Normal position causes the Core Store Control to be set.

CORE STORE CONTROL OFF pushbutton

When this pushbutton is pressed, no parity check is performed on the core store. The button has also the effect of erasing a possible core store parity error.

CORE STORE CONTROL indicator

The indicator lights when the core store is checked against parity error.

CORE STORE ERROR indicator

In the event of a parity error caused by the core store, the computer will stop at once and the indicator will light.

REGISTER DISPLAY indicator

This light signifies that the REGISTER DISPLAY field functions normally, and it is turned on when the computer is set in Stopped Mode.

Now the REGISTER DISPLAY indicator lights on the Control Panel can be used to display and alter the contents of all the registers in the arithmetic unit. The contents of a register is displayed in binary form by means of an array of indicators. Each indicator is controlled by two pushbuttons, one for setting the bit to 1, and one for resetting to 0. Besides this, two pushbuttons are used for collective set and reset of the whole register. The name of the register to be displayed is indicated in the top row of this field, and the function of the pushbuttons below is to connect one of the below mentioned registers to the display.

| WO | pushbutton | W(0)(0:23)conPB(0)(0:2) |

|----|------------|-------------------------|

| W1 | pushbutton | W(1)(0:23)conPB(1)(0:2) |

| W2 | pushbutton | W(2)(0:23)conPB(2)(0:2) |

| W3 | pushbutton | W(3)(0:23)conPB(3)(0:2) |

| IC | pushbutton | IC(5:22)                |

| SC | pushbutton | SC(11:23)               |

| FR | pushbutton | FR(0:11)                |

| SB | pushbutton | SB(0:23)conFK(0:2)      |

| SE | pushbutton | SE(0:13)                |

| AR | pushbutton | AR(-1:23)               |

| AE | pushbutton | AE(0:13)                |

| BR | pushbutton | BR(0:23)                |

BE(0:11) BE pushbutton PR(0:7)  $\mathbf{x}$ ) PR pushbutton EX(21:23) EX pushbutton IR(0:23) : display only IR pushbutton IM(0:23); display only  $\mathbf{I}\mathbf{M}$ pushbutton

x) PR(0:7) corresponds to the bit position numbers 16 to 23 in the display.

#### 2.2. Alter and Display Registers

1. Set the computer into Stopped Mode, which is done by depressing any of the following pushbuttons:

SINGLE INSTRUCTION,

SINGLE MICRO INSTRUCTION,

MAR MANUAL CONTROLLED, or

MAR COMPUTER CONTROLLED.

2. Now the REGISTER DISPLAY lights and the chosen register is displayed, and its contents can be altered.

#### 2.3. Execute Program Instruction by Instruction

A program may be examined in details by executing it instruction by instruction in the following manner:

- 1. Depress SINGLE INSTRUCTION.

- 2. Insert the program start address in IC.

- 3. Depress MAR MANUAL CONTROLLED and insert in the Micro Address Register x=4 and y=0.

- 4. Depress MAR COMPUTER CONTROLLED.

5. Depress SINGLE INSTRUCTION, which causes the first instruction to be fetched and loaded into FR and SB. After the first instruction has been fetched, each time the SINGLE INSTRUCTION pushbutton is operated, the previously fetched instruction is executed and the next instruction is fetched.

#### 2.4. Execute the Microprogram Micro Instruction by Micro Instruction

The microprogram may be examined in details by executing it micro instruction by micro instruction in the following manner:

- 1. Depress SINGLE INSTRUCTION.

- 2. Depress MAR MANUAL CONTROLLED and insert the wanted start address in the Micro Address Register.

- 3. Depress MAR COMPUTER CONTROLLED.

- 4. For each time the SINGLE MICRO INSTRUCTION pushbutton is operated, one micro instruction is executed.

#### 2.5. Read a Word from Storage

Any 27-bit word can be read out from storage as follows:

- 1. Depress SINGLE INSTRUCTION and insert in SB the wanted byte address.

- 2. Depress MAR MANUAL CONTROLLED and insert in the Micro Address Register x=1 and y=0.

- 3. Depress SINGLE MICRO INSTRUCTION and the 27-bit word is loaded into SB and PK from where it can be displayed.

- 4. Before returning to the normal mode of operation, depress MAR COMPUTER CONTROLLED.

#### 2.6. Insert or Modify a Word in Storage

Any 27-bit word in storage can be altered as follows:

- 1. Depress SINGLE INSTRUCTION and insert in SB the wanted byte address.

- 2. Depress MAR MANUAL CONTROLLED and insert in the Micro Address Register x=0 and y=30.

- 3. Depress SINGLE MICRO INSTRUCTION and the selected 27-bit word is read into SB and PK. SB and PK should now be modified to the word we want to store.

- 4. Insert in the Micro Address Register x=16 and y=8.

- 5. Depress SINGLE MICRO INSTRUCTION and the contents of SB and PK are stored.

- 6. Before returning to the normal mode of operation, depress MAR COMPUTER CONTROLLED.

#### 2.7. Insert a Word in IM Register

- 1. Depress SINGLE INSTRUCTION and insert in SB the word to be loaded into IM.

- Depress MAR MANUAL CONTROLLED and insert in the Micro Address Register x=12 and y=12.

- 3. Depress SINGLE MICRO INSTRUCTION. The contents of SB are inserted into IM: remember, IM(0) is always 1.

- 4. Before returning to the Normal Mode of operation, depress MAR COMPUTER CONTROLLED.

#### 2.8. Clear Selected Bits in IR register

- 1. Depress SINGLE INSTRUCTION and insert a 1 in the bits of SB, which corresponds to the bits to be cleared in IR.

- 2. Depress MAR MANUAL CONTROLLED and insert in the Micro Address Register x=12 and y=13.

- 3. Depress SINGLE MICRO INSTRUCTION and the selected bits of IR are cleared.

- 4. Before returning to the Normal Mode of operation, depress MAR COMPUTER CONTROLLED.

RCSL51: VB263

Author: Allan Giese

Edited: September 1968

# THE MICROPROGRAM ALGORITHMS FOR THE RC 4000 COMPUTER

#### ABSTRACT.

This paper presents the algorithms which control the execution of the instruction set. A survey of the data formats and the register structure is also given.

A/S RECENTRALEN

Falkoneralle 1,

Copenhagen, F.

#### PREFACE

This paper presents for every instruction a detailed algorithm which corresponds to the actual microprogram. The purpose of this is threefold:

- It enables the programmer to determine the outcome of an instruction for all possible data combinations.

- It shows the arithmetic and logic formulae used in the implementation of the instructions. A verification of the formulae is not included.

- It serves as a guide for the understanding of the microprogram.

.

Before proceeding to the algorithms in Section 4, we should like to clarify the different data formats and the register structure. The data formats are found in Section 1, and Section 2 describes the register structure together with an indication of the tasks of the registers. Section 3 shows the instruction set and the numeric codes assigned to these instructions.

## CONTENTS

|       |         |                         | page |

|-------|---------|-------------------------|------|

| 1.    | DATA FO | RMATS                   | 4    |

|       | 1.1.    | Fixed-Point Numbers     | 4    |

|       | 1.2.    | Floating-Point Numbers  | 4    |

|       |         |                         |      |

| 2.    | REGISTE | R STRUCTURE             | 5    |

| 3.    | INSTRUC | TION SET                | 10   |

| 4.    | DEFINIT | TION OF INSTRUCTIONS    | 13   |

| ¥ • ' | 4.1.    |                         |      |

|       | 4.2.    | Control Panel Functions | 14   |

|       | 4.3.    | Interruption Service    |      |

|       | 4.4.    |                         |      |

|       | 4.5.    | Instruction Exceptions  | 17   |

|       | 4.6.    |                         |      |

|       |         |                         |      |

APPENDIX

#### 1. DATA FORMATS.

.

#### 1.1. Fixed-Point Numbers.

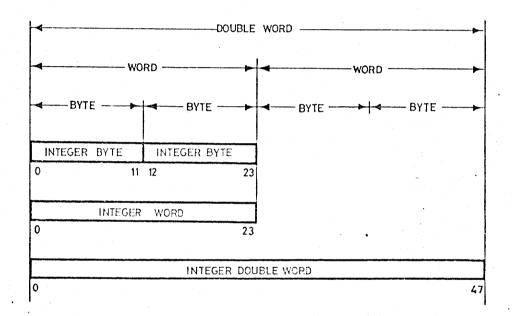

The RC 4000 accepts three formats for fixed-point numbers:

- 1) 12-bit integers (bytes)

- 2) 24-bit integers (words)

- 3) 48-bit integers (double words).

They are stored as shown in the following figure:

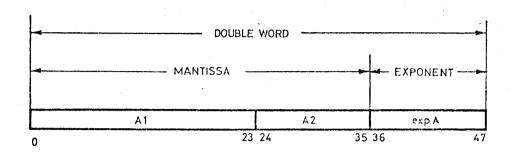

#### 1.2. Floating-Point Numbers.

A floating-point number

#### $X = A_x 2 \lambda expA$

consists of two portions, the mantissa A and the exponent expA. The mantissa is always in normalized form, which implies that A and expA are uniquely determined except when X equals zero. In this case it is perfectly clear that A must be zero, wheras expA may be any number. However, we have defined that expA for X = O should be the smallest conceivable exponent, that is in 2's complement notation 100...O. Using this notation, the following rule is always satisfied

X + 0 = X

In the RC 4000, floating-point numbers are represented by double words of 48 bits and the mantissa is divided into two fields. A1 and A2, as seen below.

If an instruction operates on two floating-point numbers  $X = A_x 2$ and  $Y = B_x 2 + \exp B$ , it is assumed that the numbers are stored as follows:

W[pre]: A1

ST[address-2]: B1

W[fr]: A2, expA ST[address] : B2, expB

#### 2. REGISTER STRUCTURE.

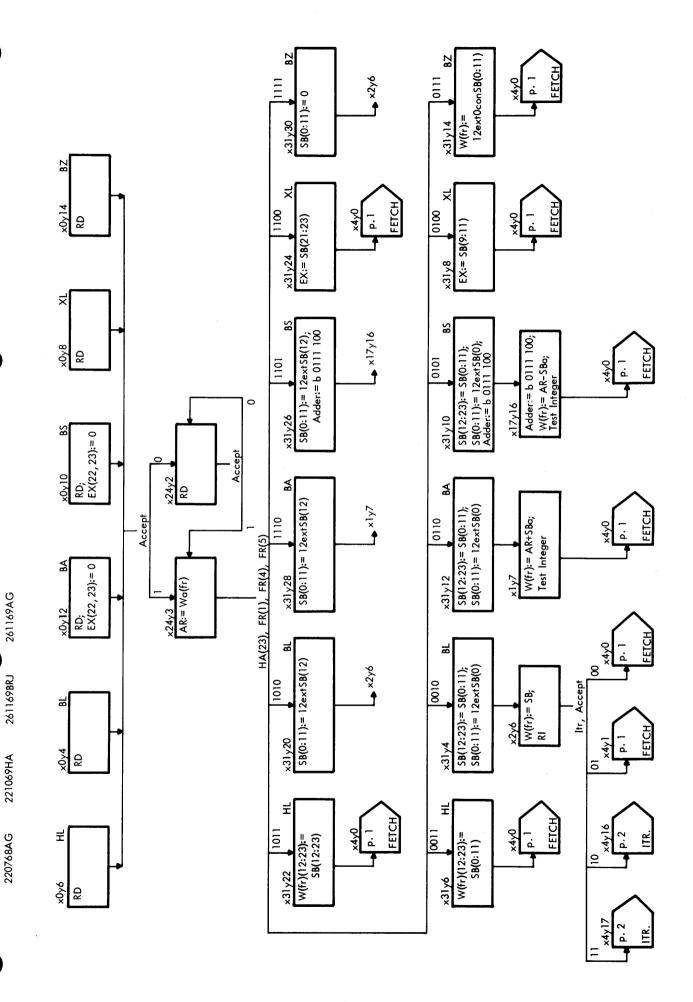

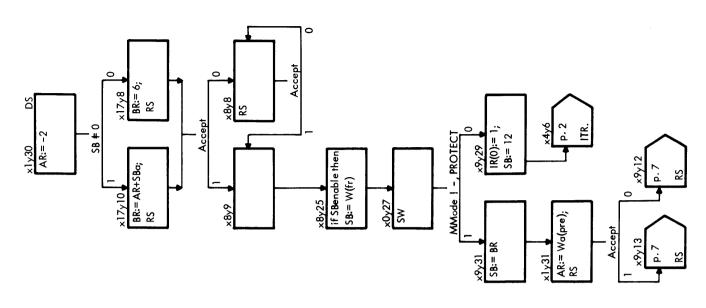

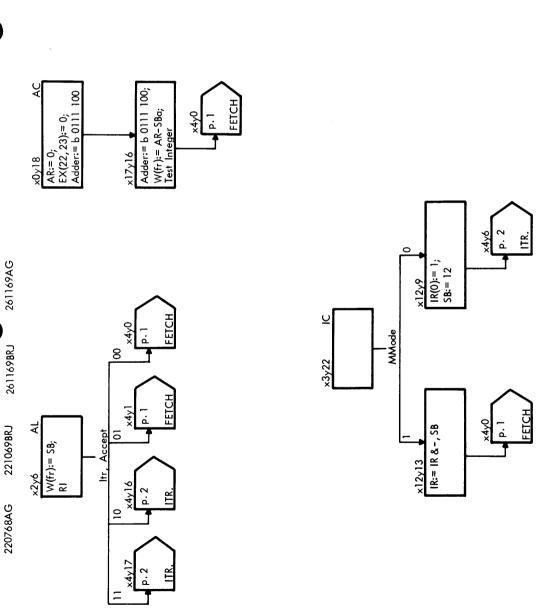

The registers of the RC 4000 are grouped around a common bus line system - a configuration which has the advantage that all the registers can transfer data directly to one another. The figure, in the Appendix, shows not only the data paths between the registers of the Arithmetic Unit, but also the paths to the Core Store Unit, the Interrupt Unit, and the Input/-Output Unit. The direction of flow is indicated by means of arrows, and the bit numbers are written on the data paths.

## Core Store Data Register; STdata(0:27).

Data communication between the Core Store Unit and the Arithmetic Unit takes place via STdata. The register is logically divided into three groups.

> STdata(0:23) Specifies a 24-bit dataword.

STdata(24:26) Specifies the protection bits.

STdata(27) Specifies the parity bit (Not shown in the Appendix).

## Core Store Address Register; STaddr(6:22).

This register is able to address the maximum core store configuration of 128 K words. STaddr may therefore have fewer bits in actual installations.

# Working Registers; W[0](0:23), W[1](0:23), W[2](0:23), W[3](0:23).

The four working registers, each of 24 bits, can be specified as the result register. Three of the registers (W[1], W[2], and W[3]), also function as index registers. The current index register is specified by the instruction format. Since the working registers also act as the first four locations of the core store, it is possible to execute instructions stored in these registers. Like the rest of the storage words each register is supplied with its own protection bits (PB).

# Protection Bits; PB[0](0:2), PB[1](0:2), PB[2](0:2), PB[3](0:2).

The four 3-bit registers determine together with the protection register whether the corresponding working register is protected or not. For example, W[0] is protected if PR(PB[0]) equals one, otherwise W[0] is unprotected.

## Protection Register; PR(0:7).

This 8-bit register specifies the protection status for the eight possible values of the protection bits. PR(0) is permanently equal to one.

## Instruction Counter; IC(5:22).

The instruction counter contains the word address of the instruction to be executed. IC is normally increased by one after execution of an instruction, but jump instructions insert explicitly the jump address in IC. A decoding of IC detects when the storage capacity is exceeded.

If the operator executes one instruction at a time by using the SINGLE INSTRUCTION pushbutton, he should be aware that IC shows the address of the instruction, which is going to be executed when he next time depresses the SINGLE INSTRUCTION button.

# Sequential Counter; SC(11:23).

The 13-bit sequential counter is used to determine the number of iterations in, for example the multiply, divide, shift, and normalize instructions. For each iteration, SC is either increased or decreased by one.

In floating-point operations, SC is also used for temporary storage of the resultant exponent.

# Function Register; FR(0:11).

ر ا ام وه

When a new instruction is fetched from storage, the function part of the instruction, i.e. the twelve left-most bits of the instruction, is assigned to the function register. FR is divided into the following five subfields:

FR(0:5) Specifies 64 basic instructions.

FR(6,7) Specifies one of the working registers as result register.

FR(8) Indirect addressing.

FR(9) Relative addressing.

FR(10,11) Indexed addressing.

# Exception Register; EX(21:23).

An exceptional outcome of an arithmetic instruction or an input/out-put instruction has the effect of setting the two bits EX(22) and EX(23). Bit EX(21) specifies the significance mode for floating-point operations. The contents of EX can also be altered by means of the Exception Load instruction.

# Storage Buffer; SB(0:23).

When a new instruction is fetched from storage, the address part (the displacement) of the instruction is assigned to the 12 right-most bits of SB. This displacement is then extended to a 24-bit signed integer. The address modifications take then place in SB in order to obtain the effective address for the data word. In consequence of, that the address for the data word is generated in SB, we have also established an address path between the core store address register (STaddr) and SB. Moreover, the 24-

bit data word, which is read from the core store, is transferred to SB just as a data word from the Arithmetic Unit to the core store also passes through SB. It is therefore no coincidence that the name for this register is storage buffer.

During the initial phase of an input/output instruction, the device address of 18 bits and the command code of 6 bits are held in SB, from which the address and the code are transmitted to the Input/Output Unit. Information from the Input/Output Unit, on the other hand, does not go via SB, but has its own direct entrance to the bus system.

Either the contents of SB or its complement may be employed as input data for the ADDER circuitry. This makes it possible for the ADDER to perform addition and subtraction.

# Protect Key; PK(0:2).

Every time a word is read from storage, the protection bits are inserted in PK, and reversely, PK determines the protection bits to be stored.

# Storage Buffer Extension; SE(0:13).

SE forms together with SB a 38-bit register which is used in floating-point operations to store the mantissa. The two extra bits SE(12,13) play an important role in the rounding calculations.

Either the contents of SE or its complement may be employed as input data for the extended ADDER circuitry.

# Adder Circuitry; ADDER(-1:37).

The adder is a parallel adder utilizing extensive carry look-ahead technique. 25 bits are added in typically 120 nanoseconds and 39 bits in 140 nanoseconds.

# A-Register; AR(-1:23).

AR constitutes together with SB the two data parts to the ADDER circuitry. Bit AR(-1) detects if an owerflow situation occurs.

# A-Register Extension; AE(0:13).

The combined 38-bit register ARconAE is used in a manner very similar to that of SBconSE.

# B-Register; BR(0:23).

BR is mainly used by multiply, divide, and double length instruction, whereas other instructions only use the register to store temporary results.

If an instruction requires two successive storage words, the address of the second word is held in BR while the first word is fetched from core store. An address path is therefore provided from BR to STaddr.

# B-Register Extension; BE(0:11).

The BR register is extended in order to be able to execute the floating-point division instruction.

# Display and Manual Control of Bus.

This unit consists of the two registers, DR(-1:23) and DP(0:2) which control BUS(-1:23) and PBUS(0:2), respectively.

# Interrupt Register; IR(0:23).

Each bit in IR is connected to an external or an internal device, which sets the bit in accordance with some specified condition. The leftmost bits are assigned highest priority.

# Interrupt Mask; IM(0:23).

IM determines whether a given interrupt request should be honoured or not. IM(0) is permanently equal to one.

# Input/Output Unit.

Each input/output device has in principle a 24-bit buffer register plus the two status bits Disconnected and Busy.

# 3. INSTRUCTION SET.

This list gives the total instruction set. The numeric code and the mnemonic code are added to each instruction.

# Address Handling

- 9 AM Modify Next Address

- 11 AL Load Address

- 33 AC Load Address Complemented

#### Register Transfer

- 3 HL Load Half Register

- 26 HS Store Half Register

- 20 RL Load Register

- 23 RS Store Register

- 25 RX Exchange Register and Store

- 54 DL Load Double Register

- 55 DS Store Double Register

### Integer Byte Arithmetic

- 19 BZ Load Byte with Zeroes

- 2 BL Load Integer Byte

- 18 BA Add Integer Byte

- 17 BS Subtract Integer Byte

#### Integer Word Arithmetic

- 7 WA Add Integer Word

- 8 WS Subtract Integer Word

- 10 WM Multiply Integer Word

- 24 WD Divide Integer Word

#### Integer Double Word Arithmetic

- 56 AA Add Integer Double Word

- 57 SS Subtract Integer Double Word

# Arithmetic Conversion

- 32 CI Convert Integer to Floating

- 53 CF Convert Floating to Integer

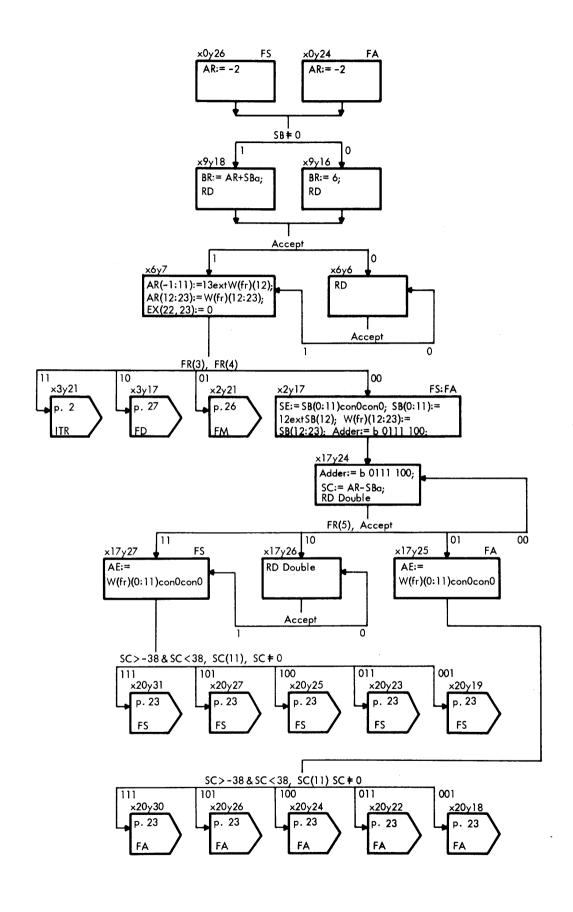

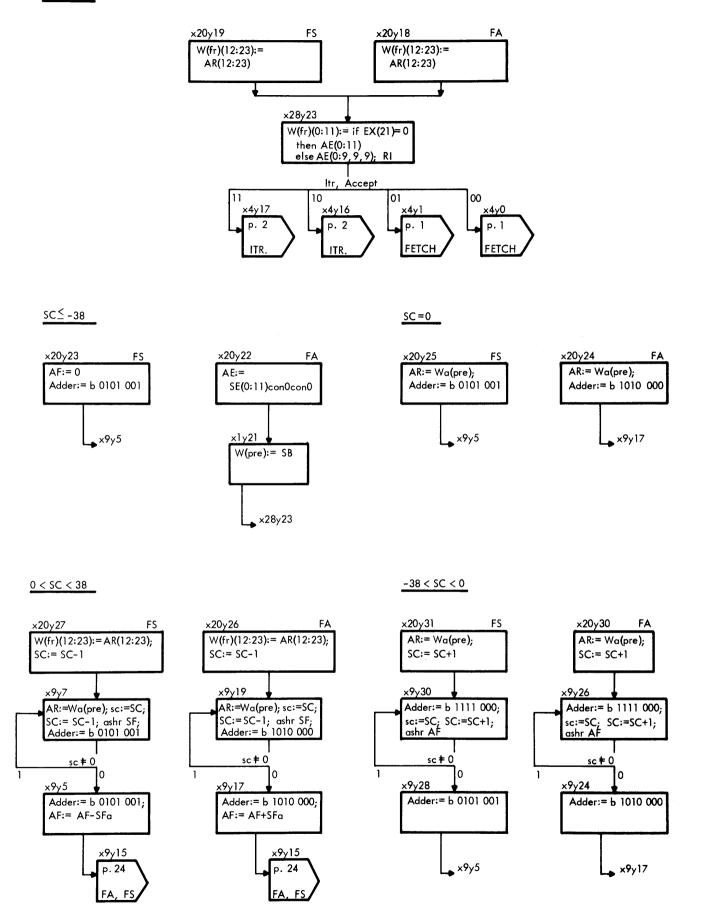

### Floating-Point Arithmetic

- 48 FA Add Floating

- 49 FS Subtract Floating

- 50 FM Multiply Floating

- 52 FD Divide Floating

### Logical Operations

- 4 LA Logical And

- 5 LO Logical Or

- 6 LX Logical Exclusive Or

### Shift Operations

. .

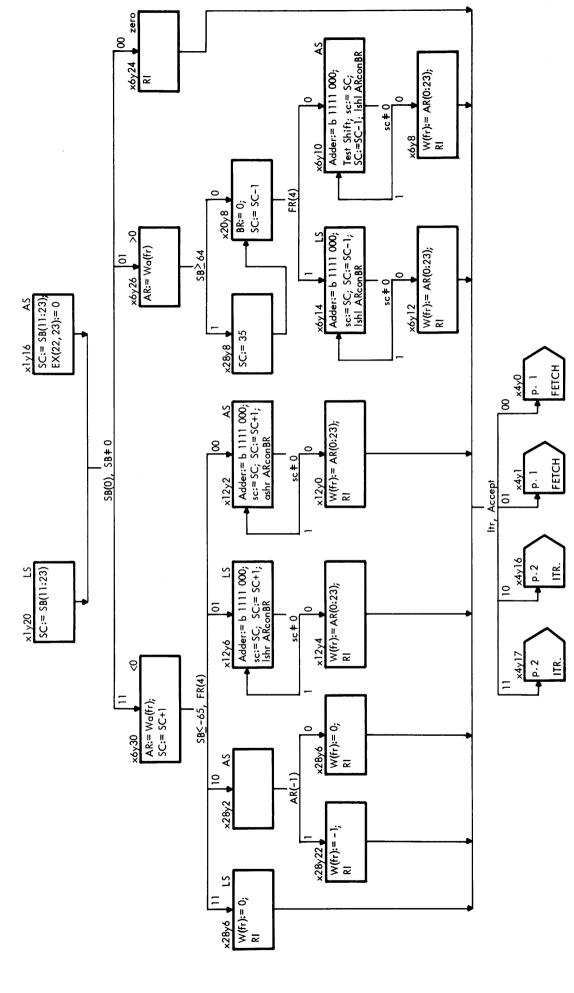

- 36 AS Shift Single Arithmetically

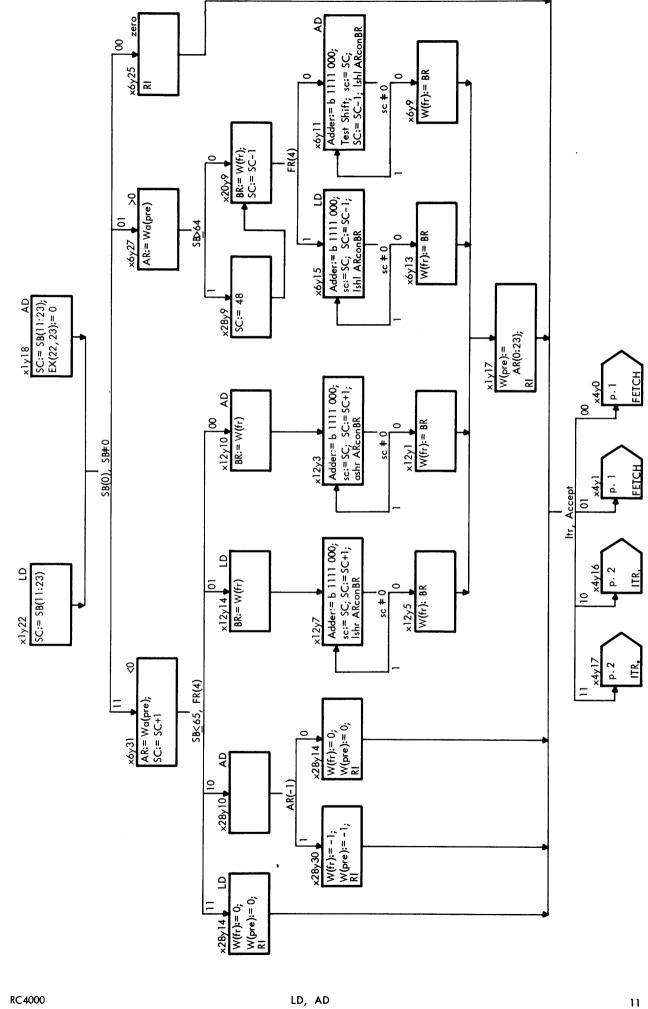

- 37 AD Shift Double Arithmetically

- 38 LS Shift Single Logically

- 39 LD Shift Double Logically

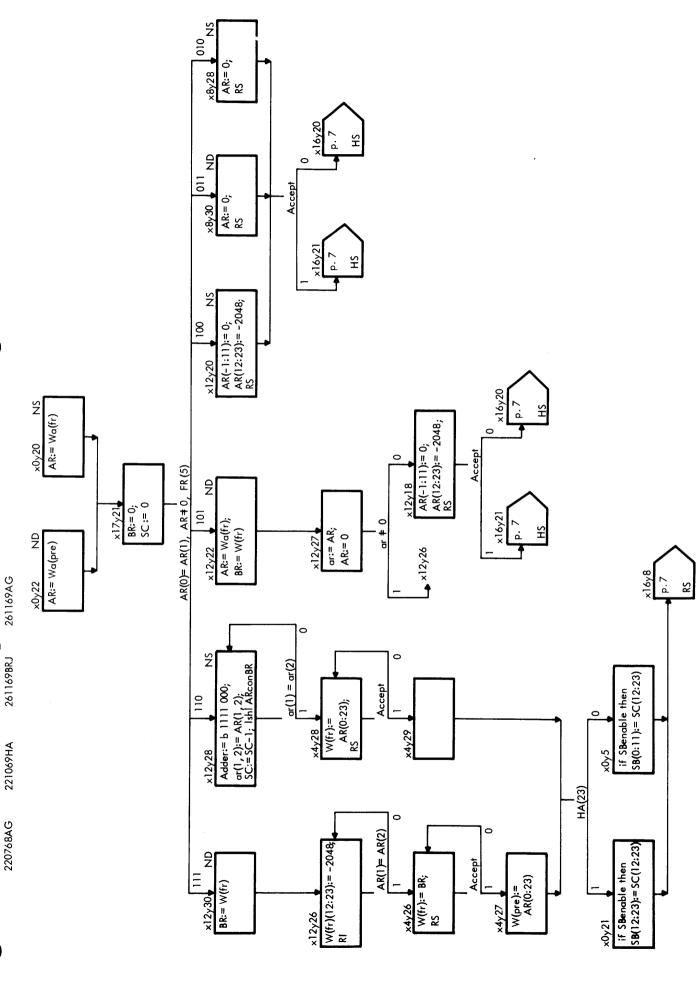

- 34 NS Normalize Single

- 35 ND Normalize Double

#### Sequencing

- 13 JL Jump with Register Link

- 40 SH Skip if Register High

- 41 SL Skip if Register Low

- 42 SE Skip if Register Equal

- 43 SN Skip if Register Not Equal

- 44 SO Skip if Register Bits One

- 45 SZ Skip if Register Bits Zero

- 46 SX Skip if No Exceptions

- 21 SP Skip if No Protection

# Monitor Control

- 15 JE Jump with Interrupt Enable

- 14 JD Jump with Interrupt Disable

- 47 IC Clear Interrupt Bits

- 31 IS Store Interrupt Register

- 12 ML Load Mask Register

- 30 MS Store Mask Register

- 16 XL Load Exception Register

- 27 XS Store Exception Register

- 28 PL Load Protection Register

- 29 PS Store Protection Register

- 22 KL Load Protection Key

- 51 KS Store Protection Key

- 1 IO Input/Output

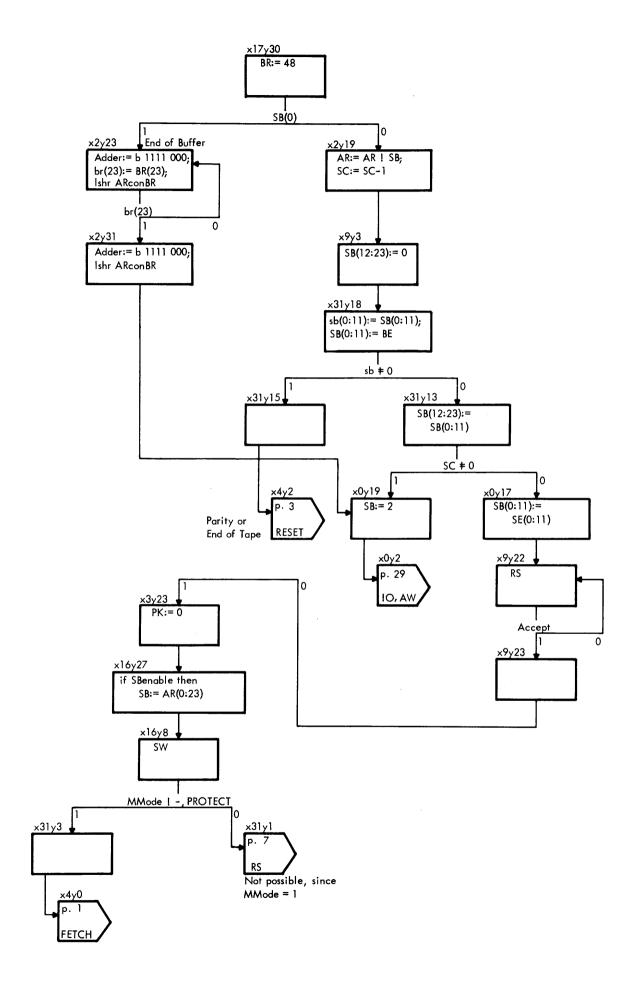

- O AW Autoload Word

#### 4. DEFINITION OF INSTRUCTIONS.

# 4.1. Notation.

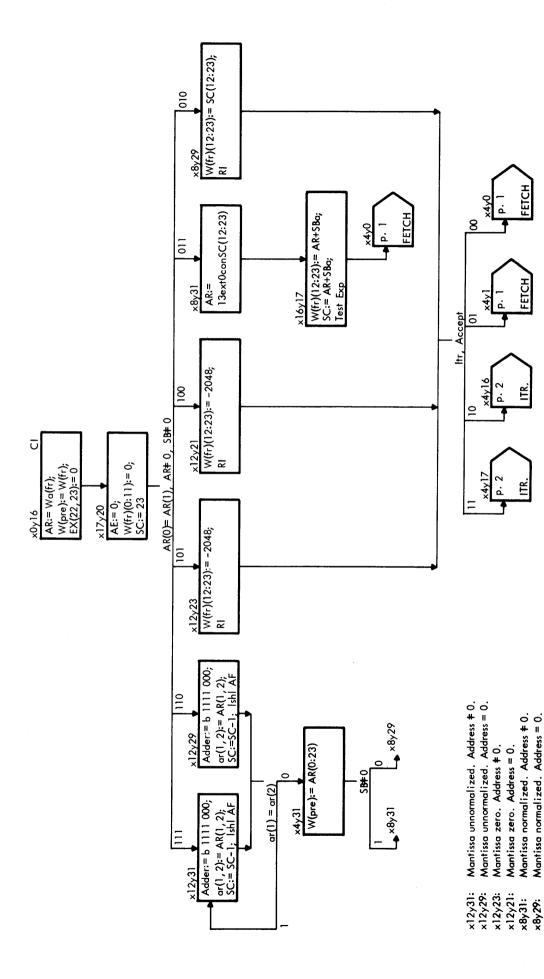

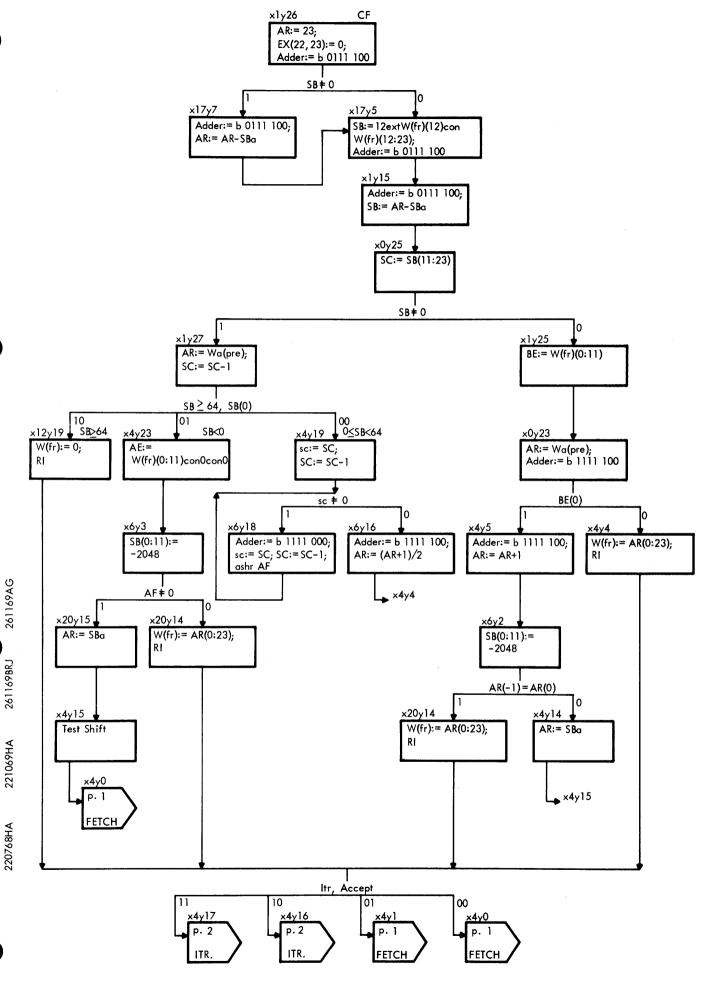

The Hargol language is used throughout this section for describing the instruction logic. Each quantity, used in the following explanation, must therefore be properly defined by a declaration. These declarations, which are listed below, are grouped for ease of interpretation.

```

Core Store Unit:

integer word limit:

register array ST[4:word limit](0:26);

register STdata(0:26), STaddr(6:22);

comment For simplicity, the parity bit is omitted:

Arithmetic Unit:

register array W[0:3](0:23), PB[0:3](0:2);

register

PR(0:7), PK(0:2), IC(5:22), SC(11:23), FR(0:11), EX(21:23),

SB(0:23), SE(0:13), AR(-1:23), AE(0:13), BR(0:23), BE(0:11);

Interrupt Unit:

register IR(0:23), IM(0:23);

Input/Output Unit:

integer Selected Device, maximum number of devices;

register array

Device Buffer[0:maximum number of devices](0:23),

Disconnected [0:maximum number of devices] (0:0),

Busy[0:maximum number of devices](0:0);

Abbreviations:

register set

SBa(-1:23) = SB(0,0:23), BRa(-1:23) = BR(0,0:23),

SF(0:37) = SB(0:23)conSE(0:13), SFa(-1:37) = SF(0,0:37),

AF(-1:37) = AR(-1:23) conAE(0:13)

BF(0:35) = BR(0:23)conBE(0:11), BFa(-1:35) = BF(0.0:35),

```

```

IRa(-1:23) = IR(0.0:23)

IMa(-1:23) = IM(0.0:23)

ICaddr(6:22) = IC(6:22),

SBaddr(6:22) = SB(6:22),

BRaddr(6:22) = BR(6:22):

register array set

Wa[0:3](-1:23) = W[0:3](0.0:23);

integer procedure fr;

fr := FR(6,7):

integer procedure pre;

pre:= if FR(6,7) = 0 then 3 else FR(6,7)-1;

integer procedure index;

index:= FR(10,11);

.Control Unit:

register

MMode(0:0), ITRenable(0:0), HA(23:23), SUM(-1:23), Carry(0:0),

Main Power Key ON(0:0),

Reset(0:0), Start(0:0), Autoload(0:0),

Single Instruction(0:0), Continue(0:0);

comb net PROTECT(0:0);

begin PR(0):= 1: PROTECT:= PR(PK) end;

switch operation:= Modify Next Address, ---, Autoload Word;

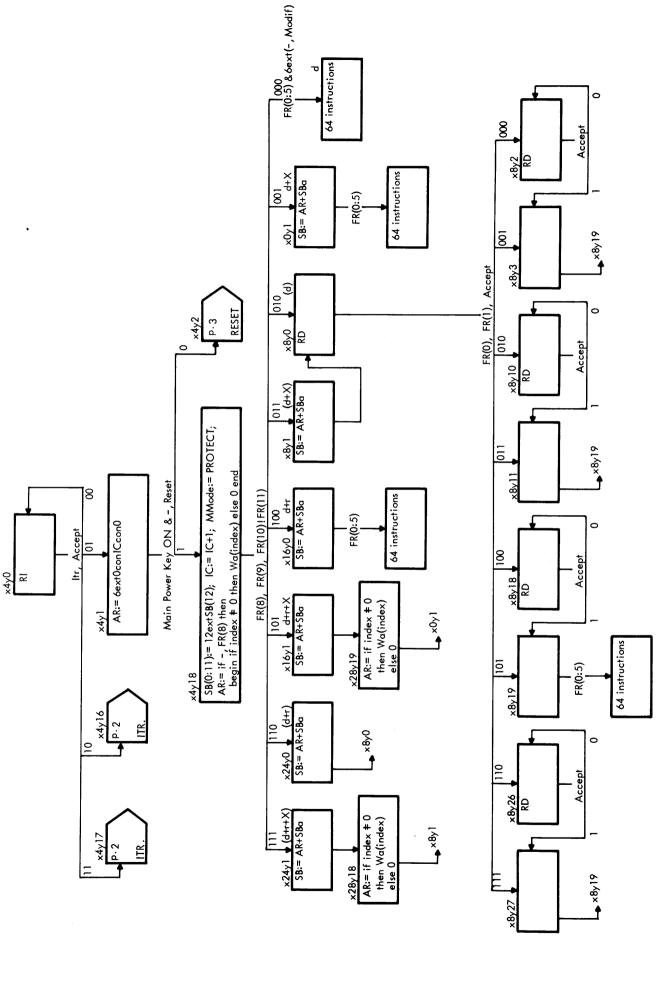

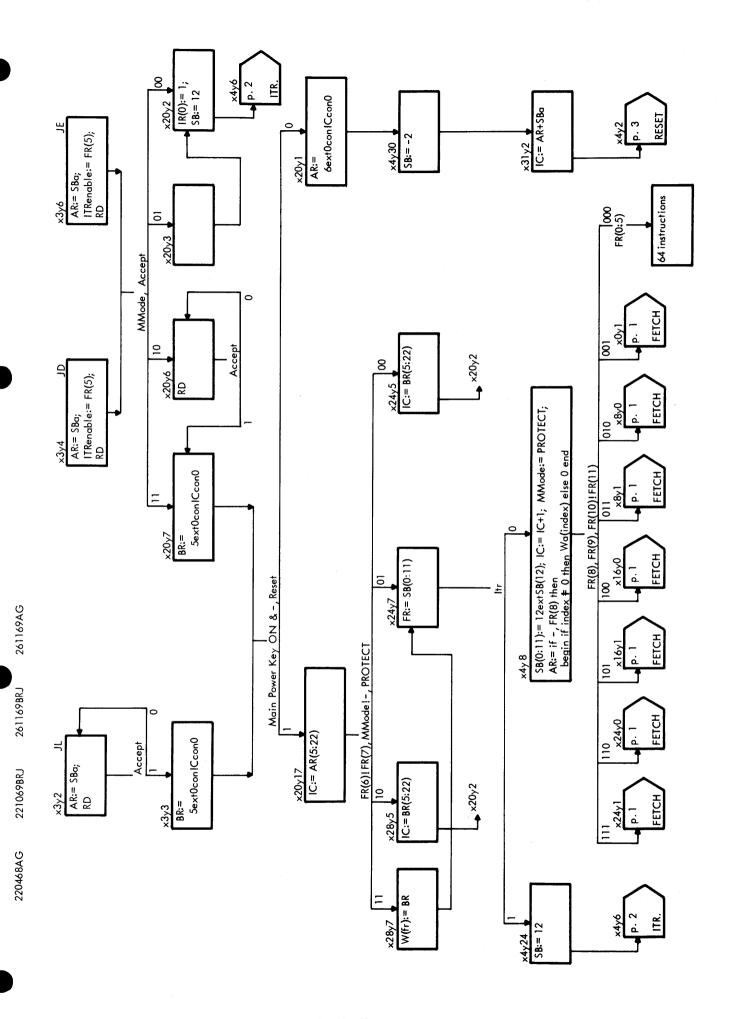

4.2. Control Panel Functions.

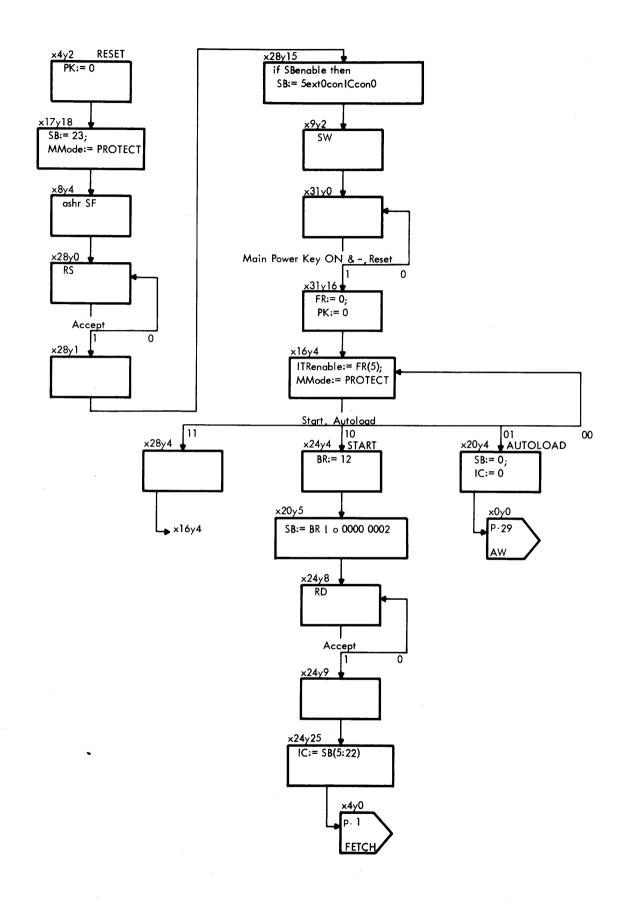

Reset System: Power Shutdown:

PK:= 0: MMode:= PROTECT:

comment MMode:= 1, since PR(0) = 1. Monitor Mode is set in order to secure

the writing into the core store;

SB:= 23: ashr SF: comment SBaddr:= 10;

wait until Accept; STaddr:= SBaddr;

SBconPK:= ST[STaddr];

SB:= 5ext0conICcon0:

ST[STaddr]:= SBconPK; comment Store IC;

wait until Main Power Key ON A - , Reset;

```

```

Power Startup:

PK:= 0: MMode:= PROTECT:

FR:= 0: ITRenable:= FR(5): comment ITRenable:= 0;

After Reset:

if Autoload then

begin

SB:= 0; IC:= 0; goto Autoload Word;

comment This is equivalent to an execution of the instruction AW O,

stored in location 0:

end;

if Start then

begin

SB:= 12 \lor 2; comment SB:= 14;

wait until Accept; STaddr:= SBaddr:

SBconPK:= ST[STaddr]: IC:= SB(5:22);

comment IC := address of start key program;

goto Next Instruction

end;

goto After Reset:

4.3. Interruption Service.

Interruption Service:

SB:= 12; BR:= 23; 1shr BF; comment BRaddr:= 10;

wait until Accept; STaddr:= SBaddr;

PK:= 0; MMode:= PROTECT; FR:= 0; ITRenable:= FR(5);

AR:= 6ext0conICcon0; comment IC:= address of interruption program;

SBconPK:= ST[STaddr]: IC:= SB(5:22);

wait until Accept; STaddr:= BRaddr; SBconPK:= ST[STaddr];

SB:= AR(0:23): ST[STaddr]:= SBconPK:

comment ST[10](0:23):= address of interrupted program;

SC:= 6; SC:= SC+2; SB:= 12ext0conSC(12:23);

wait until Accept; STaddr:= SBaddr; SBconPK:= ST[STaddr];

begin

integer ITRno;

for ITRno:= 0, ITRno+1 while (IR(ITRno) \[ IM(ITRno)) = 0 do;

IR(ITRno):= 0; SB:= ITRnox2:

```

```

comment Clear the interruption call having the highest priority;

end:

ST[STaddr]:= SBconPK: comment ST[8](0:23):= interrupt number;

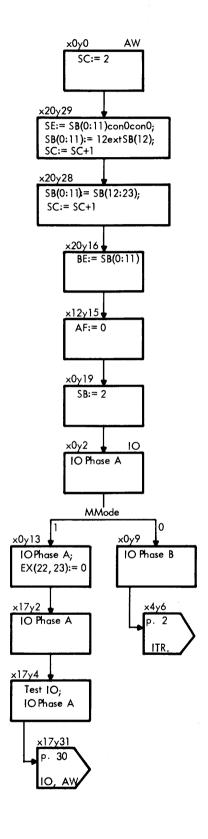

4.4. Instruction Fetch Cycle.

Next Instruction:

if or (IR A IM) A ITRenable then goto Interruption Service;

wait until Accept; STaddr:= ICaddr:

AR:= 6ext0conICcon0; comment Save relative address;

if - (Main Power Key ON A - Reset) then goto Reset System;

if IC > word limit then goto Instruction Exception;

SBconPK:= ST[STaddr]; FR:= ST[STaddr](0:11);

SB(0:11):= 12extSB(12): IC:= IC+1:

if -,FR(8) then AR:= Wa[index]; comment Speed up mechanism for indexing;

if - (MMode V - PROTECT) then goto Instruction Exception;

MMode:= PROTECT:

if Single Instruction then wait until Continue;

Address Modifications:

if FR(8) = 1 \land FR(10,11) = 0 \lor FR(8) = 0 \land FR(10,11) \neq 0 then

begin comment Relative address or indexing:

SB:= AR+SBa

end;

if FR(8) = 1 \land FR(10,11) \neq 0 then

begin comment Relative address and indexing;

SB:= AR+SBa; AR:= Wa[index]; SB:= AR+SBa

end:

if FR(9) = 1 then

begin comment Indirect address;

wait until Accept; STaddr: = SBaddr;

if SB(0:22) > word limit then goto Instruction Exception;

SBconPK:= ST[STaddr]

end;

comment SB contains the effective address and IC points at the next in-

struction;

goto operation [FR(0:5)]:

```

```

4.5. Instruction Exceptions.

Instruction Exception:

IR(0):= 1; goto Interruption Service;

procedure Test Integer:

begin

if SUM(-1) # SUM(0) then begin EX(22):= 1; IR(1):= 1 end;

if Carry(0) then EX(23) := 1

end;

procedure Test Shift;

begin

if AR(0) \neq AR(1) then begin EX(22) := 1; IR(1) := 1 end;

end;

procedure Test Exp:

begin

if SC(11) \neq SC(12) then begin EX(22) := 1; IR(2) := 1 end;

end;

4.6. Instruction Execution.

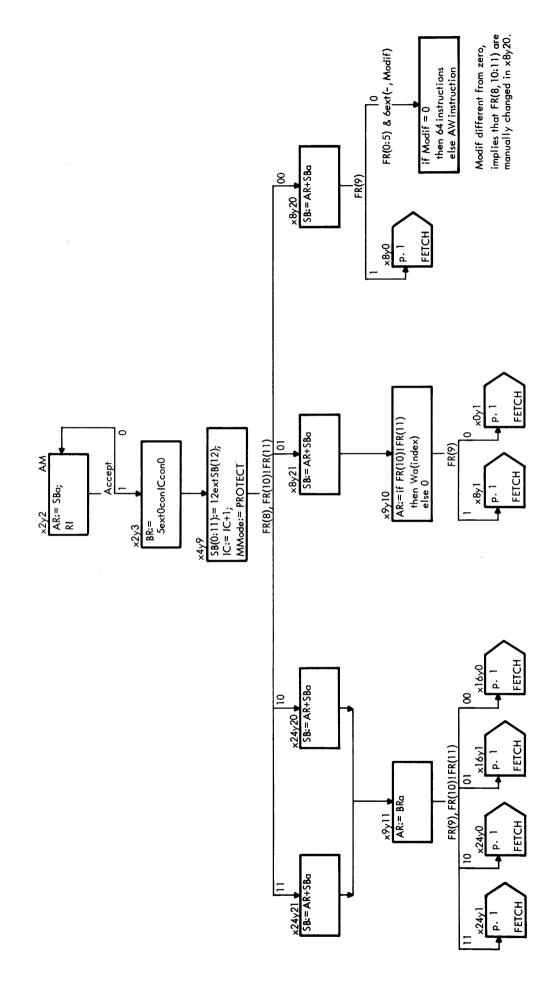

Modify Next Address:

Use the effective address as an increment to the displacement in the

next instruction. The operation changes only the effective address of

the next instruction whose D field remains unchanged.

begin

AR:= SBa:

comment The effective address of the am instruction is saved in AR:

wait until Accept: STaddr:= ICaddr:

BR:= 5ext0conICcon0; comment Save relative address;

if IC > word limit then goto Instruction Exception;

```

SBconPK:= ST[STaddr]; FR:= ST[STaddr](0:11);

if Single Instruction then wait until Continue;

if - (MMode v - PROTECT) then goto Instruction Exception;

SB(0:11):= 12extSB(12): IC:= IC+1:

MMode:= PROTECT:

```

SB:= AR+SBa;

if FR(8) = 0 \[ FR(10,11) \frac{1}{2} \] 0 then AR:= Wa[index];

if FR(8) = 1 then AR:= BRa;

goto Address Modifications

end am 9;

```

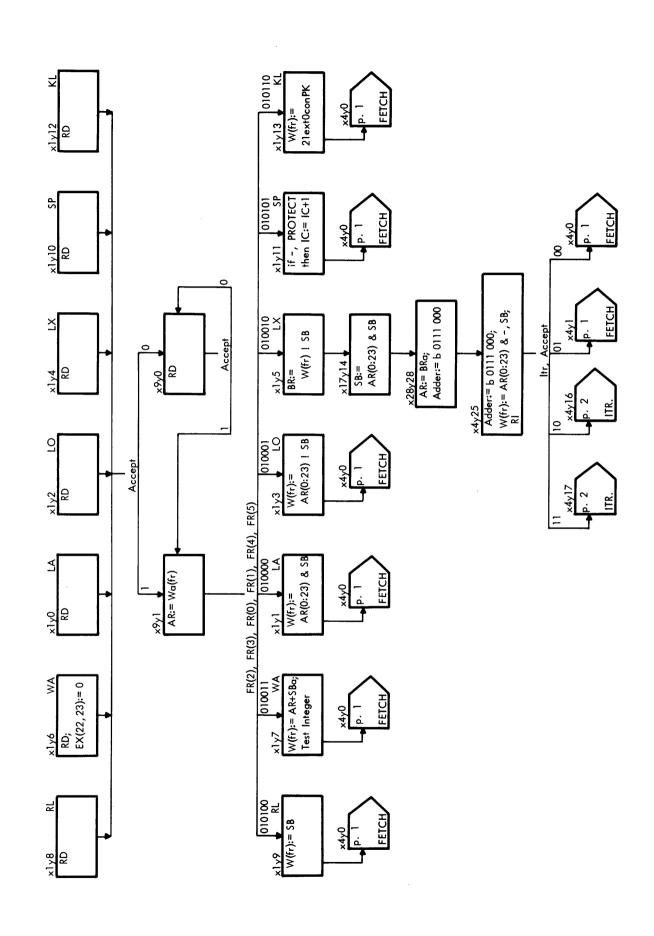

#### Load Address:

Load the W register with the effective address.

begin W[fr]:= SB; goto Next Instruction end al 11;

### Load Address Complemented:

Load the W register with the two's complement of the effective address. Complementation of the maximum negative number  $-2\lambda23$  gives the result  $-2\lambda23$  and produces an overflow.

#### begin

```

AR:= 0; EX(22,23):= 0; SUM:= AR-SBa; W[fr]:= SUM(0:23);

Test Integer; goto Next Instruction

end ac 33;

```

# Load Half Register:

Insert the storage byte addressed in the right-most 12 bits of the W register without changing the left-most 12 bits. The storage byte remains unchanged.

#### begin

```

wait until Accept; STaddr:= SBaddr; HA(23):= SB(23);

if SB(0:22) > word limit then goto Instruction Exception;

SBconPK:= ST[STaddr];

W[fr](12:23):= if HA(23) then SB(12:23) else SB(0:11);

goto Next Instruction

end hl 3;

```

#### Store Half Register: