## SPECIFICATION

## HYBRID COMPUTER LINKAGE EQUIPMENT

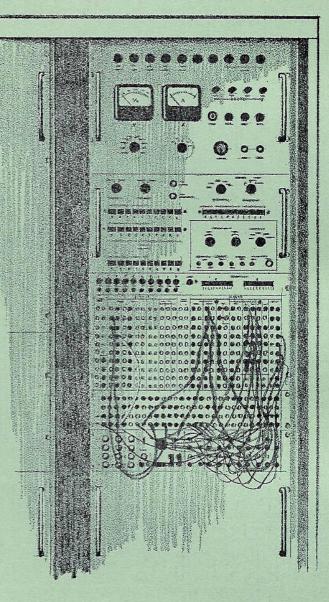

Research involving the application of digital computers to process control may be carried on effectively with a hybrid computer system, in which the process is simulated by an analog computer. The GIER System can accordingly be extended by the addition of Hybrid Computer Linkage Equipment to provide a means of communication between the GIER Computer and analog computers or other types of analog voltage systems.

The main purpose of the Hybrid Computer Linkage Equipment is to convert from analog voltages to digital numbers and vice versa. In addition, the Equipment is provided with a number of input and output channels, e.g. for digital potentiometers and on/off parameters.

ELECTRONICS

HARDWARE

Document E-14/ Revision 0/ October 1965

The GIER Computer can be provided with an interrupt unit, so that a signal to one of the interrupt channels immediately initiates a special program. The interrupt channels may be given different priorities by means of a programmed masking register.

Although the requirements of individual users differ greatly, GIER Electronics Hybrid Computer Linkage Equipment can be adapted to almost every conceivable application.

## CHARACTERISTICS

**Communication** between the GIER Computer and the Equipment takes place on a digital basis. The IL instruction transfers data to the accumulator in the computer, while the US instruction transfers data from the accumulator. One instruction transfers 10 or 20 bits.

35 Analog Input Channels These are connected to an analog/digital converter by means of a transistor multiplexer.

| Input Range:                  | + 10 V to - 10 V and/or + 100 V to - 100 V, single<br>ended                      |

|-------------------------------|----------------------------------------------------------------------------------|

| Input Resistance:             | 5 k $\Omega$ and/or 50 k $\Omega$ or 10 M $\Omega$ with optional input amplifier |

| Conversion Time:<br>Accuracy: | $60 \ \mu s$<br>$\pm 0.1\%$ of full scale, long term                             |

12 Analog Output Channels The analog outputs are generated by digital/ analog converters driven by 10-bit buffer registers.

| Output Range:      | $\pm$ 5 V (no load) |

|--------------------|---------------------|

| Output Resistance: | 2.5 kΩ ± 0.1 %      |

| Settling Time:     | 2 µs                |

10 Digital Inputs These are provided with buffer elements (10-bit registers) for temporary data storage between reading operations.

80 Digital Outputs These are provided with buffer elements arranged in 8 10-bit registers for storage of data between writing operations.

1 Control Register This 10-bit register is a digital output channel normally used for functional control purposes, such as controlling the operation modes of an analog computer. As a programming facility, the register is designed to permit the contents to be read into the computer again and data to be loaded into the control register using part of the accumulator as a masking register.

2 10-Bit Registers that can be connected by means of a switch either as a buffer register for 10 digital inputs or as a control register.

**Options** The equipment may be provided with a number of inputs or outputs, analog or digital, different from those mentioned above. The buffer registers may be expanded to 20 bits. The cabinet that houses the equipment may be placed at a distance greater than 5 m from the computer by incorporating a set of cable-drivers and -receivers.

## The Interrupt Unit

The interrupt unit containing 12 interrupt channels is housed in the central processor cabinet.

Interrupt calls are stored, until the response program can be carried out. As a programming facility, interrupt calls may be blocked by means of a 10-bit

When an interrupt call passes the mask, it causes a jump from the program in progress to a subroutine that corresponds to the interrupt channel number. After the response routine is completed, the main program continues as if nothing had happened.

Concurrent interrupt calls are processed in a fixed, built-in order.

A/S REGNEGENTRALEN FALKONERALLE 1 **COPENHAGEN F. · DENMARK**

ING.UGO DE LORENZO & C. VIA BELLARMINO 29

MILAN + ITALY

GIER ELECTRONICS GmbH SCHILLERSTRASSE 33 3000 HANNOVER · GERMANY

A Provent Provent