Aalborg Universitetscenter Institut for Elsktronicito Sychometr Laboralatiot Badehusvoj 1 A 9000 Alborg

### 001415

### DANSK DATA ELEKTRONIK

### ID-7017 DIGITAL/ANALOG CONVERSION MODULE

for the ID-7000 MICROPROCESSOR SYSTEM

June 1976

Generatorvej 6A DK-273o Herlev Denmark Author: Tom Hertz

### ID-7017 DIGITAL/ANALOG CONVERTION MODULE.

### 1. Introduction.

This module is used for generation of analog output signals from the ID-7000 microprocessor system. A maximum of 4 different analog outputs can be generated by the module. The monolithic D/A converters on the module- available in 8 bit and lo bit versions - have a 6 usec coversion time. The module is available in two versions for output range O-+10 V or O-+10V.

The module only works in ID-7000 systems with  $+/\div15V$  power supply.

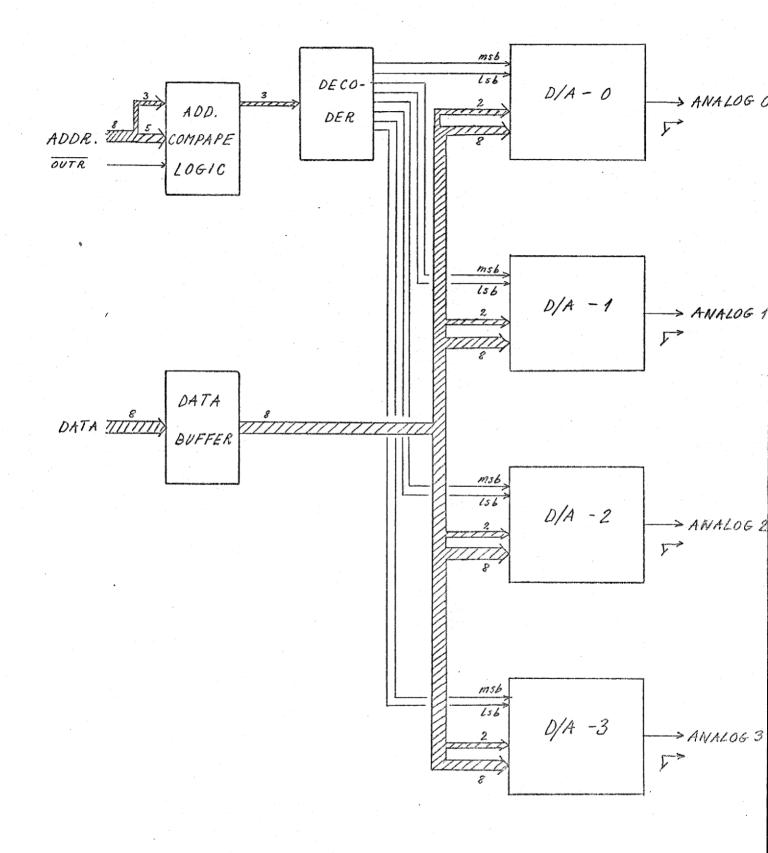

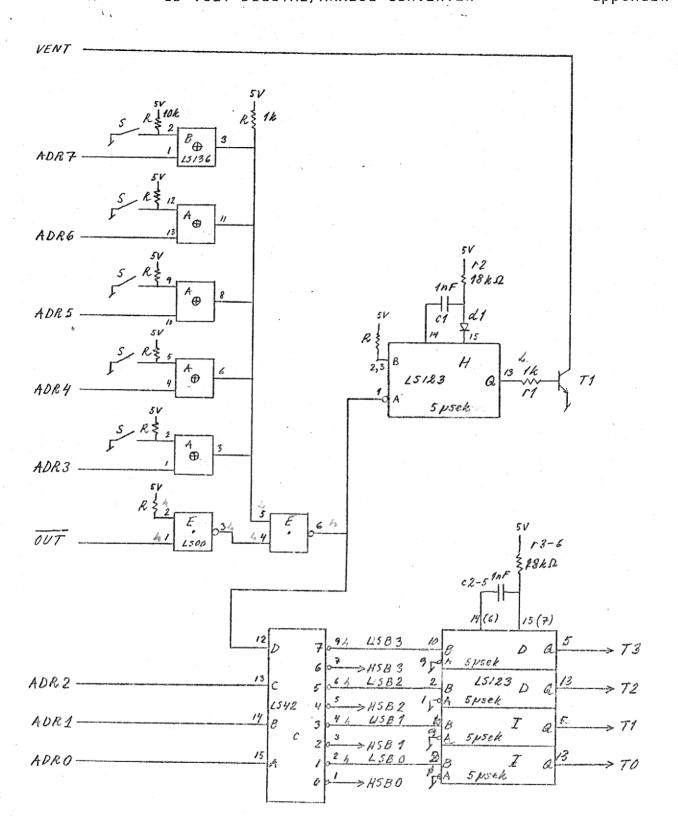

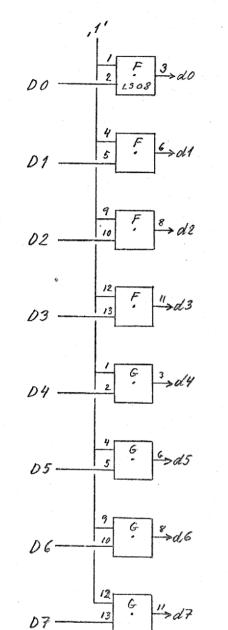

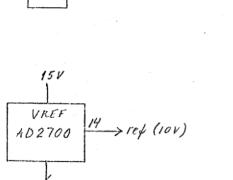

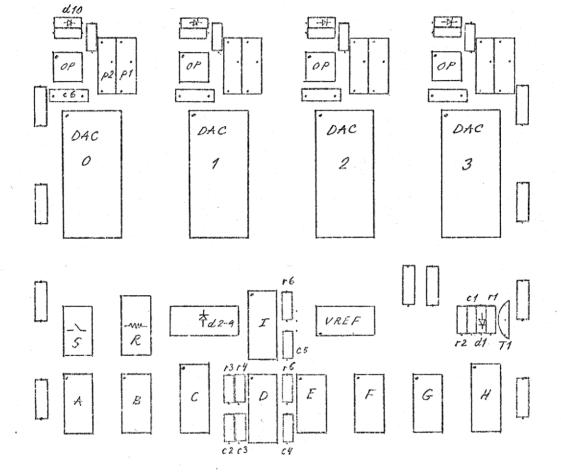

Fig. 1 shows a blocked schematic of the module.Appendix 1 is a complete diagram. Appendix 2 contains datasheets for the analog components on the board.

### 2. Description.

This section containa a description of the module from a programming point of view.

### 2.1 Addressing.

The module uses 8 consecutive addresses of the possible 256 addresses for I/O-units.The address of the module is set by a 5 bit switch register on the module.

### 2.2 Data output.

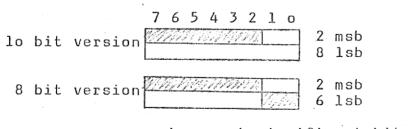

Data to the module is always sent in two parts. First the two most significant bits, and then the 6 (in 8 bit version) or 8 (in lo bit version) least significant bits. Data is interpreted as a true binary number without signbit.

ADR

|  | 4 |  | 0 |

|--|---|--|---|

|  |   |  |   |

|  |   |  |   |

| 8n   | Chernen non his | channel O |

|------|-----------------|-----------|

| 8n+1 |                 | Chaimer U |

| 8n+2 | 202000000000000 | channel l |

| 8n+3 |                 | Channer I |

| 8n+4 | CNMP PAGA VIL   | abannal 2 |

| 8n+5 |                 | channel 2 |

| 8n+6 | WIN SURPLIE     | choppel 3 |

| 8n+7 |                 | channel 3 |

msb = most significant bits

lsb = least significant bits

The analog outputs are not changed if the 2 most significant bits are altered. The change in analog value occurs shortly after the 8 (6) least significant bits are sent to the module.

### 2.3 Vent.

The module makes use ot the vent signal to delay the microcomputer in order to provide the necessary setup time for data to the D/A-chips. Each time the module is addressed the microprocessor id delayed 5 usec.

### 3. Connections.

At the top-connector the different signals are found as follow:

| pin F        | channel O     |

|--------------|---------------|

| pin 5        | analog ground |

| pin N        | channel l     |

| pin lo       | analog ground |

| pin Z        | channel 2     |

| pin 21       | analog ground |

| pin m        | channel 3     |

| pin 31       | analog ground |

| pin <u>f</u> | +15V          |

| pin h        | -15V          |

### 4. Adjustment.

The datasheet for the digital-analog converter AD7522 (in appendix 2) describes the adjustment of the converter.

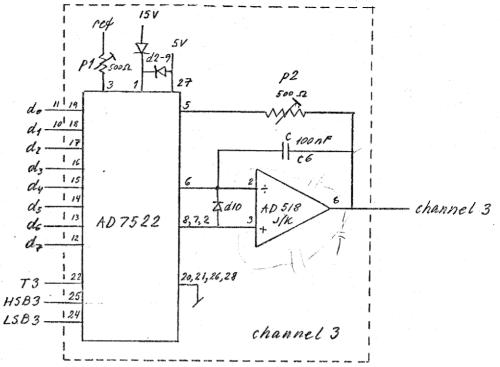

### ID 7017 DIGITAL/ANALOG CONVERTER

appendix 1.1

ID 7017 DIGITAL/ANALOG CONVERTER

appendix 1.2

channel 2

channel 1

channel O

$T^{\prime}$

# CMOS CMOS DEVICES 10-Bit, Buffered Multiplying D/A Converter

### FEATURES

10-Bit Resolution 8, 9, & 10-Bit Linearity Microprocessor Compatible Double Buffered Inputs Serial or Parallel Loading DTL/TTL/CMOS Direct Interface Nonlinearity Tempco: 2ppM of FSR/°C Gain Tempco: 10ppM of FSR/°C Very Low Power Dissipation Very Low Feedthrough

### GENERAL DESCRIPTION

The AD7522 is a monolithic CMOS 10-bit multiplying D/A converter, with an input buffer and a holding register, allowing direct interface with microprocessors. Most applications require the addition of only an operational amplifier and a reference voltage.

The key to easy interface to a data bus is the AD7522's ability to load the input buffer in two bytes (an 8-bit and a 2-bit byte), and subsequently move this data to a holding register, where the digital word is converted into an analog current or voltage (with external operational amplifier). The input loading of either 8 or 10 bits can be done in a parallel or serial mode.

The AD7522 is packaged in a 28-pin DIP, and operates with a +15V main supply at 2mA max, and a logic supply of +5V for TTL interface, or +10 to +15V for CMOS interface.

A thin film on high density CMOS process, using silicon nitride passivation, ensures high reliability and excellent stability.

### ORDERING INFORMATION

| Nonlinearity          | Temperature Range    |                 |  |  |  |  |

|-----------------------|----------------------|-----------------|--|--|--|--|

| Nonniearity           | 0°C to +75°C         | -55°C to +125°C |  |  |  |  |

| 0.2% FSR<br>(8-Bit)   | AD7522JD<br>Ad7522JN | AD7522SD        |  |  |  |  |

| 0.1% FSR<br>(9-Bit)   | AD7522KD<br>AD7522KN | AD7522TD        |  |  |  |  |

| 0.05% FSR<br>(10-Bit) | AD7522LD<br>AD7522LN | AD7522UD        |  |  |  |  |

### PACKAGE IDENTIFICATION

Suffix "D": Ceramic DIP Package Suffix "N": Plastic DIP Package

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

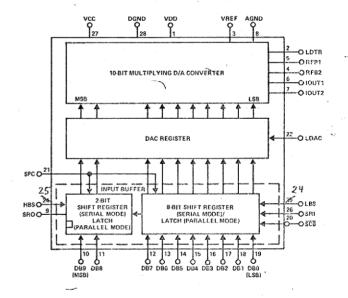

### FUNCTIONAL DIAGRAM

0.1

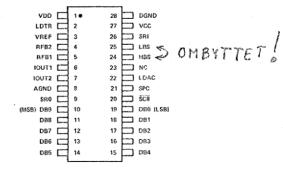

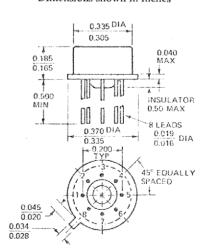

### PIN CONFIGURATION

Route 1 Industrial Park; P.O. Box 280; Norwood, Mass. 02062 Tel: (617) 329-4700 Acceleration Telex: 924491 Cable: Telex: 020400 ANALOG NORWOODMASS

# SPECIFICATIONS (VDD = +15V, VCC = +5V, VREF = ±10V, TA = +25°C unless otherwise noted)

| PARAMETER <sup>1</sup>                                  | VERSION                                      | TA = 25°C |                        |                                 | PECIFIED<br>RANGE                           | UNITS                                            | TEST CONDITIONS                         |                                                           |  |

|---------------------------------------------------------|----------------------------------------------|-----------|------------------------|---------------------------------|---------------------------------------------|--------------------------------------------------|-----------------------------------------|-----------------------------------------------------------|--|

|                                                         |                                              | MIN       | TYP                    | MAX                             | MIN                                         | мах                                              |                                         |                                                           |  |

| STATIC ACCURACY                                         |                                              |           |                        |                                 |                                             |                                                  |                                         | SC8 = "1"                                                 |  |

| <ul> <li>Resolution</li> </ul>                          | All                                          | 10        |                        |                                 | 10                                          |                                                  | Bits                                    |                                                           |  |

| Differential Nonlinearity                               | J                                            |           |                        | ±0.2                            |                                             |                                                  | % FSR                                   |                                                           |  |

|                                                         | S                                            |           |                        | ±0.2                            |                                             | ±0.2                                             | % FSR                                   |                                                           |  |

|                                                         | ĸ                                            |           |                        | ±0.1                            |                                             |                                                  | % FSR                                   |                                                           |  |

|                                                         | ି <b>T</b> ୁ                                 |           |                        | ±0.1                            |                                             | ±0.1                                             | % FSR                                   |                                                           |  |

|                                                         | L                                            |           |                        | ±0.05                           |                                             |                                                  | % FSR                                   |                                                           |  |

|                                                         | U                                            |           | 1.5                    | ±0.05                           |                                             | ±0.05                                            | % FSR                                   |                                                           |  |

| Nonlinearity                                            | J                                            |           |                        | ±0.2                            |                                             |                                                  | % FSR                                   |                                                           |  |

|                                                         | S                                            |           |                        | ±0.2                            |                                             | ±0.2                                             | % FSR                                   |                                                           |  |

|                                                         | к                                            |           |                        | .±0.1                           |                                             |                                                  | % FSR                                   |                                                           |  |

| ŧ                                                       | Т                                            |           |                        | ±0.1                            |                                             | ±0.1                                             | % FSR                                   | $-10V \le VREF \le +10V$                                  |  |

|                                                         | L                                            |           |                        | ±0.05                           |                                             |                                                  | % FSR                                   |                                                           |  |

|                                                         | U                                            |           |                        | ±0.05                           |                                             | ±0.05                                            | % FSR                                   |                                                           |  |

| Nonlinearity Tempco <sup>2</sup>                        | J, K, L                                      |           | ±1                     |                                 |                                             | ±2                                               | ppm FSR/°C                              |                                                           |  |

|                                                         | S, T, U                                      |           |                        |                                 |                                             | ±2                                               | ppm FSR/°C                              |                                                           |  |

| Gain Error                                              | J, K, L                                      |           | ±0.3                   |                                 |                                             |                                                  | % Reading                               |                                                           |  |

| Gain Error Tempco <sup>2</sup>                          | J, K, L                                      |           | ±5                     |                                 |                                             | ±10                                              | ppm of Reading/°C                       |                                                           |  |

|                                                         | S, T, U                                      |           |                        |                                 |                                             | ±10                                              | ppm of Reading/°C                       |                                                           |  |

| Output Leakage Current                                  | All                                          |           |                        |                                 |                                             | 200                                              | nA                                      | IOUT1: DB0 through DB9 = 0                                |  |

| at IOUT1 or IOUT2                                       |                                              |           |                        |                                 |                                             |                                                  |                                         | IOUT2: DB0 through DB9 = $1$                              |  |

| Power Supply Rejection                                  | J, K, L                                      |           | 50                     |                                 |                                             |                                                  | ppm of Reading/%                        |                                                           |  |

| AC ACCURACY                                             | and and a second statements and              |           | rational lancing       | in California a substance a sus | en de travent des racions e des activations |                                                  | ana ang ang ang ang ang ang ang ang ang | an seren an           |  |

| Feedthrough Error <sup>2</sup>                          | All                                          |           | 1                      | 10                              |                                             |                                                  | w.V. s. s.                              | WREE - 20W 10 - U-                                        |  |

| Output Current                                          | J, K, L                                      |           | 500                    |                                 | *_*                                         |                                                  | mV p-p                                  | VREF = 20V p-p; 10 kHz<br>To 0.05% of FSR for a FSR Step. |  |

| Settling Time                                           | J, K, L                                      |           | 300                    |                                 |                                             |                                                  | ns                                      | HBS and LBS Low to High                                   |  |

| Setting Thic                                            |                                              |           |                        |                                 |                                             |                                                  |                                         | LDAC = 1                                                  |  |

|                                                         |                                              | ·         |                        |                                 |                                             |                                                  |                                         | EDAC - 1                                                  |  |

| REFERENCE INPUT                                         |                                              |           |                        |                                 |                                             |                                                  |                                         |                                                           |  |

| Input Resistance                                        | All                                          | 5         |                        | 20                              |                                             |                                                  | kΩ                                      |                                                           |  |

| ANALOG OUTPUT                                           | La 1990, MA Carl IN IN Chief Carl And Anna 1 |           | hand the second second |                                 | a manada sa ana ani ang sa ani ang sa       | alanandramatik e one armaa na agaanta araanaanaa |                                         | an ann an amhraidh ann ann an an ann ann ann ann ann ann  |  |

| Output Capacitance                                      |                                              |           |                        |                                 |                                             |                                                  |                                         |                                                           |  |

| Courri                                                  | J, K, L                                      |           | 120                    |                                 |                                             |                                                  | pF.                                     |                                                           |  |

| COUT2                                                   | J, K, L<br>J, K, L                           |           | 40                     |                                 |                                             |                                                  | pF<br>pF                                | All Data Inputs High                                      |  |

| C <sub>OUT1</sub>                                       | J, K, L<br>J, K, L                           |           | 40                     |                                 |                                             |                                                  | pF                                      |                                                           |  |

| C <sub>OUT2</sub>                                       | J, K, L<br>J, K, L                           |           | 120                    |                                 |                                             |                                                  | pF<br>pF                                | All Data Inputs Low                                       |  |

|                                                         | J, H, D                                      |           |                        |                                 |                                             |                                                  |                                         |                                                           |  |

| DIGITAL INPUTS                                          |                                              |           |                        |                                 |                                             |                                                  |                                         |                                                           |  |

| Low State Threshold                                     | J, K, L                                      |           |                        | 0.8                             |                                             |                                                  | v                                       | -                                                         |  |

|                                                         | S, T, U                                      |           |                        | 0.8                             |                                             | 0.8                                              | V                                       |                                                           |  |

| High State Threshold                                    | J, K, L                                      | 2.4       |                        |                                 |                                             |                                                  | v                                       |                                                           |  |

| angan manganggun ang ang ang ang ang ang ang ang ang an | S, T, U                                      | 2.4       |                        |                                 | 2.4                                         |                                                  | V                                       |                                                           |  |

| Input Current                                           | J, K, L                                      |           | 1                      |                                 |                                             |                                                  | μA                                      |                                                           |  |

| LDAC Pulse Width                                        | All                                          | 5         |                        |                                 |                                             |                                                  | μs                                      | LDAC: 0 to +3V                                            |  |

| Requirement <sup>3</sup>                                |                                              |           |                        |                                 |                                             |                                                  |                                         |                                                           |  |

| HBS, LBS Pulse                                          | All                                          | 5         |                        |                                 |                                             |                                                  | μs                                      | HBS, LBS: 0 to +3V                                        |  |

| Width Requirement <sup>3</sup>                          |                                              | -         |                        |                                 |                                             |                                                  | 1                                       |                                                           |  |

| Serial Clock Frequency <sup>3</sup>                     | All                                          |           |                        | 200                             |                                             |                                                  | kHz ·                                   |                                                           |  |

Notes <sup>1</sup> Specifications subject to change without notice. <sup>2</sup> Guaranteed by design. Not tested. <sup>3</sup> Sample tested.

-2-

## SPECIFICATIONS (continued)

| PARAMETER <sup>1</sup> | VERSION | 1 <b>1</b><br>1 | ſA = +2 | 5°C |     | PECIFIED<br>RANGE | UNITS | TEST CONDITIONS |

|------------------------|---------|-----------------|---------|-----|-----|-------------------|-------|-----------------|

|                        |         | MIN             | TYP     | MAX | MIN | MAX               |       |                 |

| POWER REQUIREMENTS     |         |                 |         |     |     |                   |       |                 |

| IDD                    | All     |                 |         | 2   |     |                   | mA    | 4               |

| ICC                    | All     |                 |         | 2   |     |                   | mA    |                 |

| ABSOLUTE | MAXIMUM | RATINGS |

|----------|---------|---------|

|----------|---------|---------|

| VREF to GND ±25V                                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------|

| VDD to GND +17V                                                                                                                         |

| VCC to GND +17V                                                                                                                         |

| VCC to VDD +0.4V                                                                                                                        |

| IOUT1, IOUT2 ±5 mA                                                                                                                      |

| Operating Temperature                                                                                                                   |

| Storage Temperature $\dots \dots \dots$ |

| Power Dissipation (Package)     |          |

|---------------------------------|----------|

| Up to +50°C:                    |          |

| Plastic (Suffix N)              | 1200 mW  |

| Ceramic (Suffix D)              | 1000 mW  |

| Derate Above +50°C by           |          |

| Plastic (Suffix N)              | 12 mW/°C |

| Ceramic (Suffix D)              | 10 mW/°C |

| Digital Input Voltage Range VDI | D to GND |

CAUTION:

- 1. Do not apply voltages higher than VCC to SRO.

- 2. Do not apply voltages higher than VDD or less than GND to any other input/output terminal except VREF, RFB1 or RFB2.

- 3. The digital control inputs are zener protected, however permanent damage may occur on unconnected units under high energy electrostatic fields. Keep unused units in conductive foam at all times.

- 4. VCC should never exceed VDD by more than 0.4V, especially during power ON or OFF sequencing.

### Terminology

#### RESOLUTION

Value of the LSB. For example, a unipolar n-bit converter has a resolution of  $(2^{-n})$  (VREF). A bipolar n-bit converter has a resolution of  $[2^{-(n-1)}]$  [VREF]. Resolution in no way implies linearity.

### NONLINEARITY

Error contributed by deviation of the DAC transfer function from a best straight line function. For a multiplying DAC, the nonlinearity should be independent of the sign or magnitude of VREF. Nonlinearity is normally expressed as a percentage of full scale range (% FSR).

### DIFFERENTIAL NONLINEARITY

In a DAC, differential linearity error describes the variation in the analog output transitions between adjacent pairs of digital input numbers, over the full range of digital inputs. If each transition is equal to its neighbors' (i.e., 1 LSB), the "differential nonlinearity" is zero. If a transition differs from the ideal by more than 1 LSB, a D/A converter can be "nonmonotonic." A specific maximum differential non-linearity of  $\pm 1/2$ LSB at  $\pm 25^{\circ}$ C ensures that monotonic behavior will exist over a tangible range of temperatures.

### GAIN

The "gain" of a converter is that analog scale factor setting that establishes the nominal conversion relationship, e.g., 10V full scale. It is a linear error which can be externally adjusted. (See gain adjustment on page 6.)

### OUTPUT LEAKAGE CURRENT

Current which appears on the OUT1 terminal when the DAC register is loaded with all "0's" or on the OUT2 terminal when the DAC register is loaded with all "1's."

-3-

# Pin Function Description

1000

| PIN      | MNEMONIC    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                        | 1 | PIN | MNEMONIC  | DECONDUCY                                                                                                                                                                                                                                                                               |

|----------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | -           |                                                                                                                                                                                                                                                                                                                                                                                    | - |     | MINEMONIC | DESCRIPTION                                                                                                                                                                                                                                                                             |

| 1        | VDD<br>LDTR | +15V (nominal) Main Supply.<br>R-2R Ladder Termination Resistor.<br>Normally grounded for unipolar<br>operation or terminated at IOUT2<br>for bipolar operation.                                                                                                                                                                                                                   |   | 21  | SPC       | Serial/Parallel Control. If SPC is a<br>logic "0," the AD7522 will load<br>parallel data appearing on DB0<br>through DB9 into the input buffer<br>when the appropriate strobe inputs<br>are exercised (see HBS and LBS).                                                                |

| 3        | VREF        | Reference Voltage Input. Since the<br>AD7522 is a multiplying DAC,<br>VREF may vary over the range of<br>±10V.                                                                                                                                                                                                                                                                     |   |     |           | If SPC is a logic "1," the AD7522<br>will load serial data appearing on<br>Pin 26 into the input buffers. Each                                                                                                                                                                          |

| 4        | RFB2        | Rfeedback ÷ 2; gives full scale equal<br>to VREF/2.                                                                                                                                                                                                                                                                                                                                |   | -   |           | serial data bit must be "strobed"<br>into the buffer with the HBS and<br>LBS.                                                                                                                                                                                                           |

| 5        | RFB1        | Rfeedback, used for normal unity gain (at full scale) D/A conversion.                                                                                                                                                                                                                                                                                                              |   | 22  | LDAC      |                                                                                                                                                                                                                                                                                         |

| 6        | IOUT1       | DAC Current OUT-1 Bus. Normally<br>terminated at virtual ground of out-<br>put amplifier.                                                                                                                                                                                                                                                                                          |   | 22  | LDAC      | Load DAC: When LDAC is a logic<br>"0," the AD7522 is in the "hold"<br>mode, and digital activity in the<br>input buffer is locked out. When                                                                                                                                             |

| 7        | IOUT2       | DAC Current OUT-2 Bus, terminated<br>at ground for unipolar operation, or<br>virtual ground of op amp for bipolar<br>operation.                                                                                                                                                                                                                                                    |   |     |           | LDAC is a logic "1," the AD7522<br>is in the "load" mode, and data in<br>the input buffer loads the DAC<br>register.                                                                                                                                                                    |

| .8       | AGND        | Analog Ground. Back gate of DAC<br>N-channel SPDT current steering<br>switches.                                                                                                                                                                                                                                                                                                    |   | 23  | NC        | No Connection.                                                                                                                                                                                                                                                                          |

| 9        | SRO         | Serial Output. An auxiliary output<br>for recovering data in the input<br>buffer.                                                                                                                                                                                                                                                                                                  |   | 24  | HBS       | High Byte Strobe. When in "parallel<br>load" mode (SPC = 0), parallel data<br>appearing on the DB9 (MSB) and                                                                                                                                                                            |

| 10       | DB9         | Data Bit 9. Most significant parallel<br>data input.                                                                                                                                                                                                                                                                                                                               |   | •   |           | DB8 data inputs will be "clocked"<br>into the input buffer on the positive<br>going edge of HBS.                                                                                                                                                                                        |

| 11<br>12 | DB8<br>DB7  | Data Bit 8.<br>Data Bit 7.                                                                                                                                                                                                                                                                                                                                                         |   |     |           | When in "serial load" mode (SPC = 1), serial data bits appearing at the                                                                                                                                                                                                                 |

| 13       | DB6         | Data Bit 6.                                                                                                                                                                                                                                                                                                                                                                        |   |     |           | serial input terminal, Pin 26, will be                                                                                                                                                                                                                                                  |

| 14       | DB5 Note 1  | Data Bit 5.                                                                                                                                                                                                                                                                                                                                                                        |   |     |           | "clocked" into the input buffer on<br>the positive going edges of HBS and                                                                                                                                                                                                               |

| 15<br>16 | DB4 DB3     | Data Bit 4.                                                                                                                                                                                                                                                                                                                                                                        |   |     |           | LBS. (HBS and LBS must be clocked simultaneously when in                                                                                                                                                                                                                                |

| 17       | DB3<br>DB2  | Data Bit 3.<br>Data Bit 2.                                                                                                                                                                                                                                                                                                                                                         |   |     | х.        | "serial load" mode.)                                                                                                                                                                                                                                                                    |

| 18       | DB1         | Data Bit 1.                                                                                                                                                                                                                                                                                                                                                                        |   | 25  | LBS       | Low Byte Strobe. When in "parallel                                                                                                                                                                                                                                                      |

| 19       | DBO         | Data Bit 0. Least significant parallel data input.                                                                                                                                                                                                                                                                                                                                 |   | 25  | 1.03      | load" mode (SPC = 0), parallel data<br>appearing on the DB0 (LSB) through                                                                                                                                                                                                               |

| 20       | SC8         | 8-Bit Short Cycle Control. When in serial mode, if SC8 is held to logic                                                                                                                                                                                                                                                                                                            |   |     |           | DB7 inputs will be "clocked" into the<br>input buffer on the positive going edge<br>of the LBS.                                                                                                                                                                                         |

|          |             | "0," the two least significant input<br>latches in the input buffer are by-<br>passed to provide proper serial<br>loading of 8-bit serial words. If SC8<br>is held to logic "1," the AD7522<br>will accept a 10-bit serial word.<br>Data bits 0(LSB) and DB1 are in a<br>parallel load mode when SC8 = 0,<br>and should be tied to a logic low<br>state to prevent false data from |   |     |           | When in "serial load" mode (SPC =<br>1), serial data bits appearing at the<br>serial input terminal, Pin 26, will<br>be "clocked" into the input buffer<br>on the positive going edge of HBS<br>and LBS. (HBS and LBS must be<br>clocked simultaneously when in<br>"serial load" mode.) |

|          |             | being loaded.                                                                                                                                                                                                                                                                                                                                                                      |   | 26  | SRI       | Serial Input.                                                                                                                                                                                                                                                                           |

|          |             |                                                                                                                                                                                                                                                                                                                                                                                    |   |     |           |                                                                                                                                                                                                                                                                                         |

|          |             |                                                                                                                                                                                                                                                                                                                                                                                    |   |     |           |                                                                                                                                                                                                                                                                                         |

| 2        | ,           |                                                                                                                                                                                                                                                                                                                                                                                    |   |     |           |                                                                                                                                                                                                                                                                                         |

i de la come

.4.

### Pin Function/Description/cont/de

| PIN | MNEMONIC | DESCRIPTION                                                                                                                                                           |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 27  | VCC      | Logic Supply. If +5V is applied, all<br>digital inputs/outputs are TTL com-<br>patible. If +10V to +15V is applied,<br>digital inputs/outputs are CMOS<br>compatible. |

Note 1: Logic "1" applied to a data bit steers that bit's current to the IOUT1 terminal.

| PIN | MNEMONIC | DESCRIPTION     |

|-----|----------|-----------------|

| 28  | DGND     | Digital Ground. |

|     |          |                 |

|     | 1 B<br>1 |                 |

### **DAC** Circuit Description

### GENERAL CIRCUIT INFORMATION

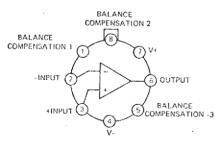

The AD7522's DAC functional block consists of a highly stable Silicon Chromium thin film R-2R ladder, and ten SPDT N-channel current steering switches. Most applications require the addition of only an output operational amplifier and a voltage or current reference.

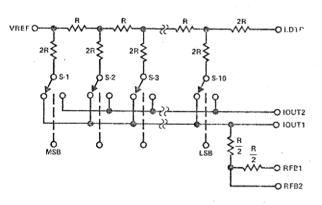

The simplified D/A circuit is shown in Figure 1. An inverted R-2R ladder structure is used — that is, the binarily weighted currents are switched between the IOUT1 and IOUT2 bus lines, thus maintaining a constant current in each ladder leg independent of the switch state.

Figure 1. DAC Functional Diagram

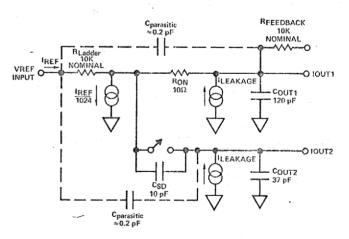

Figure 2. Equivalent Circuit (Shown for all Digital Inputs High)

### EQUIVALENT CIRCUIT

The DAC equivalent circuit is shown in Figure 2. The current source  $I_{LEAKAGE}$  is composed of surface and junction leakages to the substrate, while the  $I_{REF}/1024$  current source represents the 1LSB of current lost through the ladder termination resistor to ground. The COUT1 and COUT2 output capacitances are as shown when the DAC latches feed the

DAC with all "1's." If the DAC latches are loaded with all "0's," C<sub>OUT1</sub> is 37 pF, while C<sub>OUT2</sub> is 120 pF. In addition, C<sub>SD</sub> is shunted by 10 ohms, and the 10 ohm R<sub>ON</sub> in IOUT1 is replaced by a C<sub>SD</sub> of 10 pF. When fast amplifiers are used, it will be necessary to provide phase compensation (in the form of feedback capacitance) to cancel the pole formed by RFEEDBACK and C<sub>OUT</sub> if stability is to be maintained.

### Applications

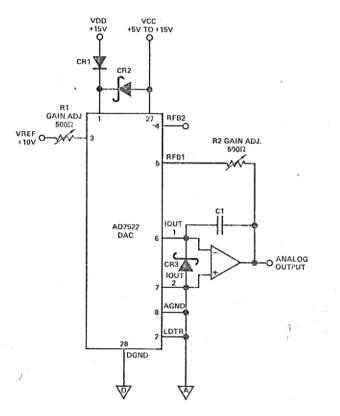

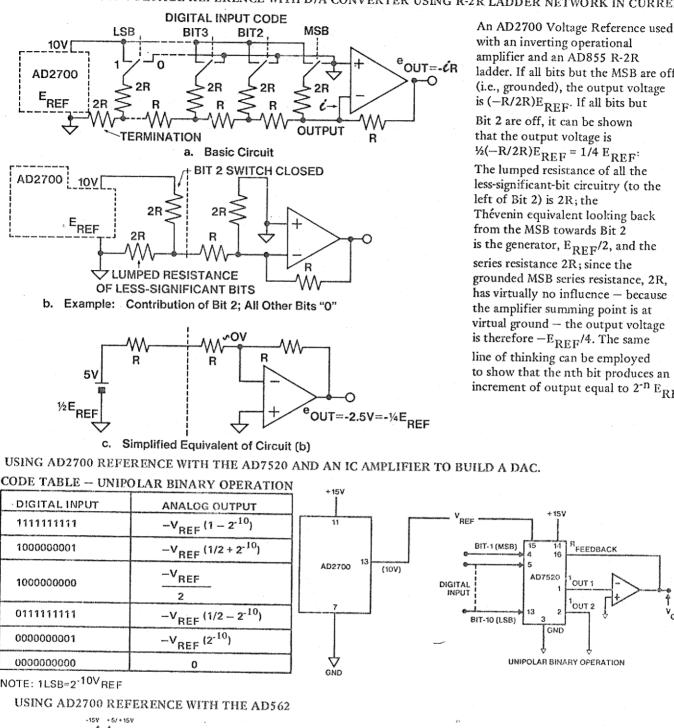

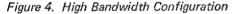

### JNIPOLAR OPERATION

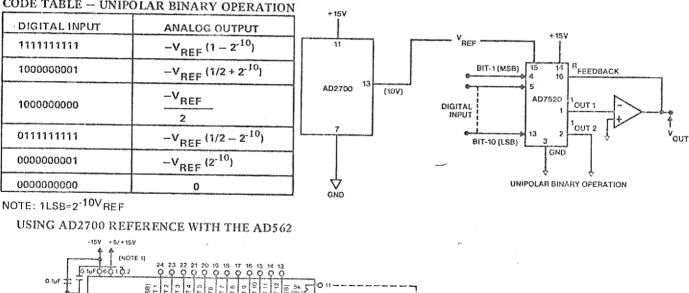

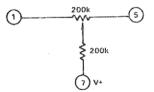

Figure 3 shows the analog circuit connections required for unipolar operation. The input code/output voltage relationthip is shown in Table 1.

### Zero Offset Adjustment

1. Adjust the op amp's offset potentiometer for < 1 mV on the amplifier junction. (Each millivolt of amplifier V<sub>OS</sub> causes  $\pm 0.66 \text{ mV}$  of differential nonlinearity which adds to the ladder nonlinearity.)

### Figure 3. Unipolar Binary Operation (2-Quadrant Multiplication)

#### Gain Adjustment

- 1. Set R1 and R2 to  $0\Omega$ . Load the DAC register with all "1's."

- If analog out is greater than --VREF, increase R1 for required full scale output. If analog out is less than --VREF, increase R2 for required full scale output.

| TABLE 1             |

|---------------------|

| UNIPOLAR CODE TABLE |

| DIGITAL INPUT | ANALOG OUTPUT          |

|---------------|------------------------|

| 1111111111    | $-VREF(1-2^{-10})$     |

| 1000000001    | $-VREF(1/2 + 2^{-10})$ |

| 1000000000    | -VREF/2                |

| 0111111111    | $-VREF(1/2-2^{-10})$   |

| 0000000001    | $-VREF(2^{-10})$       |

| 0000000000    | 0                      |

TABLE 2 BIPOLAR CODE TABLE

| DIGITAL INPUT | ANALOG OUTPUT                 |

|---------------|-------------------------------|

| · 1111111111  | $-$ VREF $(1 - 2^{-9}) - 10V$ |

| 100000001     | VREF (2 <sup>-9</sup> )       |

| 1000000000    | 0                             |

| 0111111111    | VREF (2 <sup>-9</sup> )       |

| 0000000001    | VREF $(1 - 2^{-9})$ (0)       |

| 0000000000    | VREF                          |

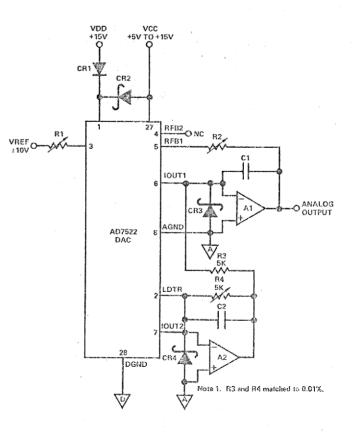

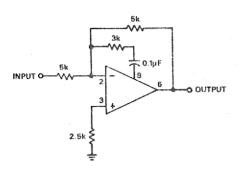

### **BIPOLAR OPERATION**

Figure 4 shows the analog circuit connections required for bipolar operation. The input code/output voltage relationship is shown in Table 2.

### Zero Offset Adjustment

Adjust the offset potentiometer of amplifier A1 and A2 for <1 mV on the respective summing junctions. If the analog out for code 1000000000 is not zero, sum current into or out of the summing junction of A1 for 0V at analog out.

#### Gain Adjustment

1. Load the DAC register with all "0's." Set R1 and R2 to  $0\Omega$ .

2. If analog out is greater than +VREF, increase R2 until it reads precisely +VREF. If analog out is less than +VREF, increase R1 until it reads precisely VREF.

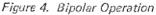

### SINGLE BYTE PARALLEL LOADING

Figure 5 illustrates the logic connections for loading single byte parallel data into the input buffer. DB0 should be grounded on "K" and "T" versions, and DB0 and DB1 should be grounded on "J" and "S" versions for monotonic operation of the DAC. DB9 is always the MSB, whether 8-bit, 9-bit, or 10-bit linear AD7522's are used.

When data is stable on the parallel inputs (DB0-DB9), it can be transferred into the input buffer on the positive edge of the strobe pulse.

Data is transferred from the input buffer to the DAC register when LDAC is a logic "1." LDAC is a level-actuated (versus edge-triggered) function, and must be held "high" at least  $3\mu$ s for data transfer to occur.

Figure 5. Single Byte Parallel Loading

### TWO BYTE PARALLEL LOADING

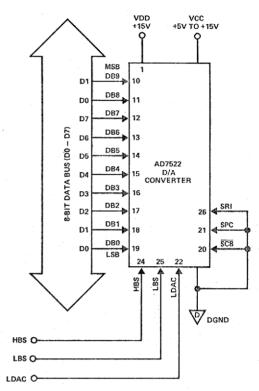

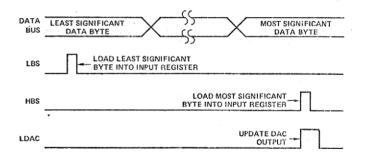

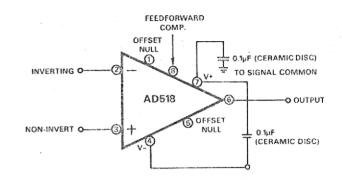

Figures 6 and 7 show the logic connections and timing requirements for interfacing the AD7522 to an 8-bit data bus for two byte loading of a 10-bit word.

First, the least significant data byte (DB0 through DB7) is loaded into the input buffer on the positive edge of LBS. Subsequently, the data bus is used for status indication and instruction fetching by the CPU. When the most significant data byte (DB8 and DB9) is available on the bus, the input buffer is loaded on the positive edge of HBS. The DAC register updates to the new 10-bit word when LDAC is "high." LDAC may be exercised coincident with, or at any time after HBS loads the second byte of data into the input buffer.

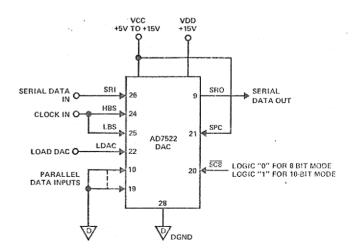

#### SERIAL LOADING

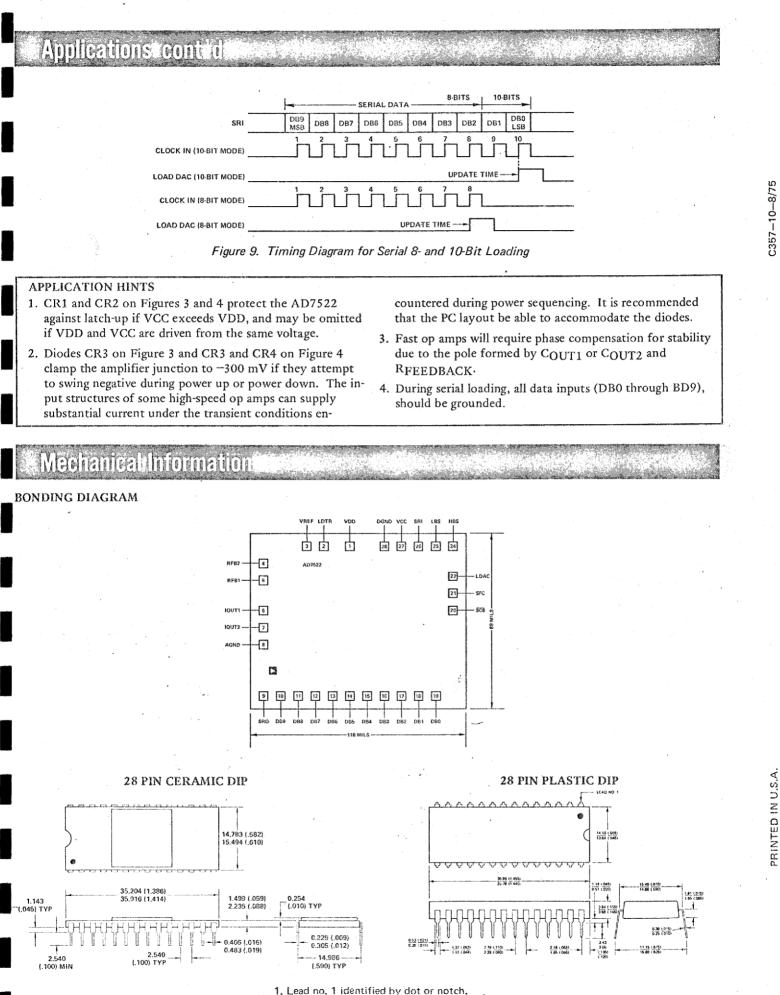

Figure 8 and Figure 9 show the connections and timing diagram for serial loading.

To load a 10-bit word (SC8 = 1), HBS and LBS must be strobed simultaneously with exactly 10 positive edges to clock the serial data into the input buffer. For 8-bit words (SC8 = 0), only 8 positive edges are required.

The DAC register can now be loaded by holding LDAC "high."

NOD PRIMORS MORE

18

Figure 6. Two Byte Parallel Loading

Figure 7. Timing Diagram

-7-

Lead no. 1 identified by dot or notch.

Dimensions in millimeters (inches).

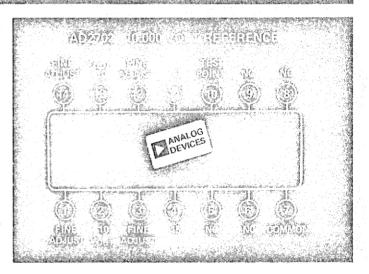

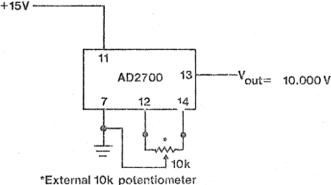

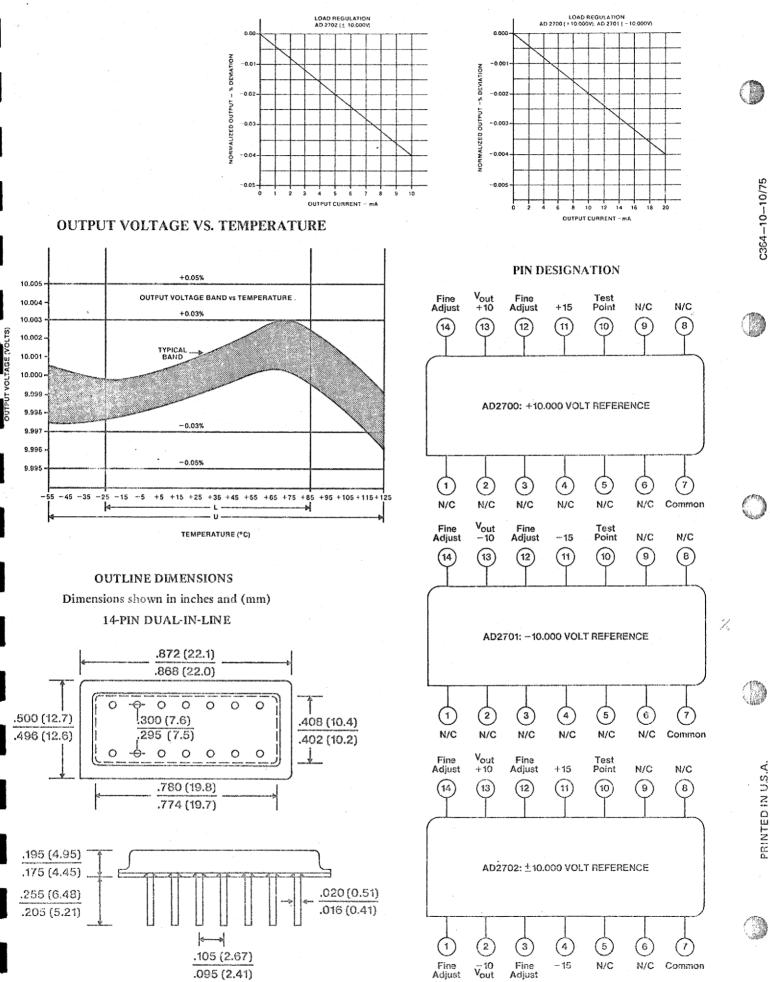

## ± 10.000 ± .001 Volt Precision Reference

### AD27/00 AD27/01 AD27/02

### PRELIMINARY TECHNICAL DATA FEATURES

3-Terminal Device: Voltage In/Voltage Out Total Output Error at T<sub>MAX</sub> to: 2mV Excellent Long Term Stability: To 50ppm/yr. OP. Range: -55 °C to + 125 °C 20mA Current Output Capability Available Screened to MIL-STD-883A Use withAD7520, AD7570, AD562 Short Circuit Protected

### PRODUCT DESCRIPTION

MODEL

AD 2700

AD2701

AD2702

The AD2700 is a medium cost, high stability, temperature compensated voltage reference source. The reference output is accurately fixed at 10V. With excellent temperature stability and long term stability of 50ppm/year, the AD2700 offers a convenient solution to regulated voltage requirements which may previously have been met with bulky power supplies or elaborate diodes and ovens. This product is made possible by the combination of the best available semiconductor technology with high precision thin film resistors which are functionally trimmed.

The AD2700 is recommended for use in 10- or, 12-bit A/D, and D/A converter circuits and other precise analog circuits. Its small size and hermetic seal make it adaptable to essentially any application or environment.

The operation of the AD2700 is 3 terminal, voltage in/voltage out. No external components are required. Offset adjustment terminals are provided for optional use if accuracy of better than 1mV is desired.

OUTPUT

+10.000V

-10,000V

$\pm 10.000 V$

provides  $\pm 30$ mV output offset adjust. Temperature effect is  $\pm 4\mu$ V/°C per mV of offset correction.

\*(External Adjustment Optional)

ANALOS DIVICES A/S MÁLOVGARDSVEJ S 2750 BALLERUP TLE. 97.95.90

Note: Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use; nor for any infringements of patents or other rights granted by implication or otherwise under any patent or patent rights of Analog Devices. P.O. Box 280; Norwood, Massachusetts 02062 U.S.A. Telex: 924491 Cables: ANALOG NORWOODMASS

# **SPECIFICATIONS** (typical at 25°C and $V_{in}$ = +15V unless otherwise specified)

| ABSOLUTE MAX RATINGS                 |                         |

|--------------------------------------|-------------------------|

| Input Voltage                        | 20VDC                   |

| Power Dissipation @ +25°C            | 400 mW                  |

| Derate Above 25°C                    | 1mW/°C                  |

| Storage Temperature Range            | -65 to $+150^{\circ}$ C |

| Lead Temperature (soldering, 10 sec) | 250 <sup>°</sup> C      |

| Operating Temperature Range – L & U  | -55°C to +125°C         |

| Short Circuit Protection             | Continuous              |

|                                      |                         |

| ELECTRICAL CHARACTERISTICS                                                                                                | •                                                    | MIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ТҮР                                                                                                                          | MAX                                                                                                                                   | UNITS                                  |

|---------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Output Voltage @ 25°C, No Load                                                                                            | -2700<br>-2701<br>-2702                              | +9.999<br>10.001<br>+9.999                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | +10.000<br>-10.000<br>$\pm 10.000$                                                                                           | +10.001<br>9.999<br>+10.001                                                                                                           |                                        |

| Output Current                                                                                                            |                                                      | n monorman mes con non patri ancente de la consecutiva de la consecutiva de la consecutiva de la consecutiva d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ±18                                                                                                                          | ±20                                                                                                                                   | mA                                     |

| Total Maximum Output Error<br>(Including Initial Offset)<br>"L"Guarnateed -25°C to +85°C<br>"U"Guaranteed -55°C to +125°C | @-55°C<br>-25°C<br>+25°C<br>+70°C<br>+85°C<br>+125°C |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $\begin{array}{c} \pm 0.02 \\ \pm 0.02 \\ \pm 0.02 \\ \pm 0.005 \\ \pm 0.02 \\ \pm 0.02 \\ \pm 0.02 \\ \pm 0.03 \end{array}$ | $\begin{array}{r} \pm 0.03 \\ \pm 0.03 \\ \pm 0.02 \\ \pm 0.01 \\ \pm 0.03 \\ \pm 0.03 \\ \pm 0.03 \\ \pm 0.03 \\ - 0.05 \end{array}$ | %<br>%<br>%<br>%                       |

| Input Regulation/Power Supply<br>Rejection (V <sub>in</sub> = 12 to 18 V)                                                 | en versionen andere en versionen ander Weiner an er  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | .0003                                                                                                                        | .0004                                                                                                                                 | %/%                                    |

| Load Regulation<br>AD 2700/01 0 to $\pm$ 10mA<br>AD 2702 0 to $\pm$ 5mA<br>(See Graphs Page 4)                            |                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | .0015<br>.015                                                                                                                | .002<br>.02                                                                                                                           | %<br>%                                 |

| Input Voltage, Operating                                                                                                  |                                                      | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15                                                                                                                           | 18                                                                                                                                    | V                                      |

| Input Current, No Load                                                                                                    | anan "antor direction kangana kangana kangana ka     | annan konstanten (der ja den na de over det signinger gens agen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | en la presidente, este maria en al este de este de la presidente de la constanción de la constanción de la const             | 12                                                                                                                                    | mA                                     |