MULTI PURPOSE MULTI PROCESSOR BOARD

DOCUMENT NO PRODUCT SPECIFICATION CR2000-/000--/00 CSD-MIC/005/PSP/0033

PREPARED BY HENNING SKOVLY HANSEN

AUTHORIZED BY GOTTLOB BORUP

C

DISTRIBUTION : ASM (5), GB, VS, HSH, EL, MBJ (2), FILE (2), KFL (4)

| DATE                   | SIGNATURE | 7  |

|------------------------|-----------|----|

| <u>1.1 1.111. 1573</u> | fls       | 2  |

| •                      |           |    |

|                        |           | •  |

| 717 - A - 71           |           | ÷= |

| 3                      | •         |    |

|                        |           |    |

|                        |           |    |

# APPROVED BY:

<u>.....</u>

400-919

A

-1 -1 -

۲.

|                |                                           | CSD-MIC/005/P    |                                                         |

|----------------|-------------------------------------------|------------------|---------------------------------------------------------|

| דית. דוזא      | PURPOSE MULTI PROCESSOR BOARD             | sign/date        | page ii ·                                               |

|                |                                           | HSH/820219       | project                                                 |

| MPMP           | PRODUCT SPECIFICATION                     | TK/810501        |                                                         |

| ٦              |                                           |                  | <u>~</u>                                                |

| *              | · · · · · · · · · · · · · · · · · · ·     | <u>ب</u> د       | с.<br>С                                                 |

| - 1            |                                           | i .,             | •<br>•<br>• • • • •                                     |

| - ×            | Table of content                          | ~ š***           |                                                         |

|                |                                           | •                | * * *<br>*                                              |

| \$             | Scope                                     | *                |                                                         |

|                |                                           |                  | ۹<br>*****                                              |

|                |                                           |                  |                                                         |

| 0.             | Applicable Documents<br>System Advantages | . <sup>1</sup>   |                                                         |

|                |                                           | ۰ ۰ ۰ ۲ ۲<br>۲   | 1 4 1 4 1 4<br>1 4 1 4 1 4 1 4 1 4 1 4 1 4              |

| 1.             | Introduction                              | ÷                | • • • •                                                 |

|                |                                           | х<br>* ,         | · · · ·                                                 |

|                | 1.1 Functional Summary                    | -                |                                                         |

|                | 1.2 Block Diagram                         | м<br>7           | · · ·                                                   |

| · ·*           | 1.2.1 Main Processor                      |                  | مه<br>ب                                                 |

|                | L.2.2 Front Processor                     | •                | 5 / 5 )                                                 |

|                | 1.2.3 Multibus Interface                  | ***              | `                                                       |

|                | 1.2.4 Multimodule Interface               | • · · ·          | *<br>; ÷                                                |

| •              | 1.2.5 Bus Arbiter & Control               | Logic            | هي <sup>ع</sup> سر<br>م <sup>نا</sup> م <sup>مي</sup> ع |

| ÷              | 1.3 Mechanical Layout                     |                  | 10 A A                                                  |

| ۶.             |                                           | · ~              | الجم<br>روانه مو 1                                      |

| 2              | Interface Specifications                  | •                |                                                         |

| 24 B           | THREFIACE PRECIFICATIONS                  | ۰۰, ۲            | ****<br>***                                             |

| ~<br>* ,       |                                           | •                | . —                                                     |

|                | 2.1 Multibus Interface                    | ¥                |                                                         |

| *              | 2.1.1 Signal Specification                |                  |                                                         |

|                | 2.1.2 Electr. Specification               |                  | v <u>⊨</u>                                              |

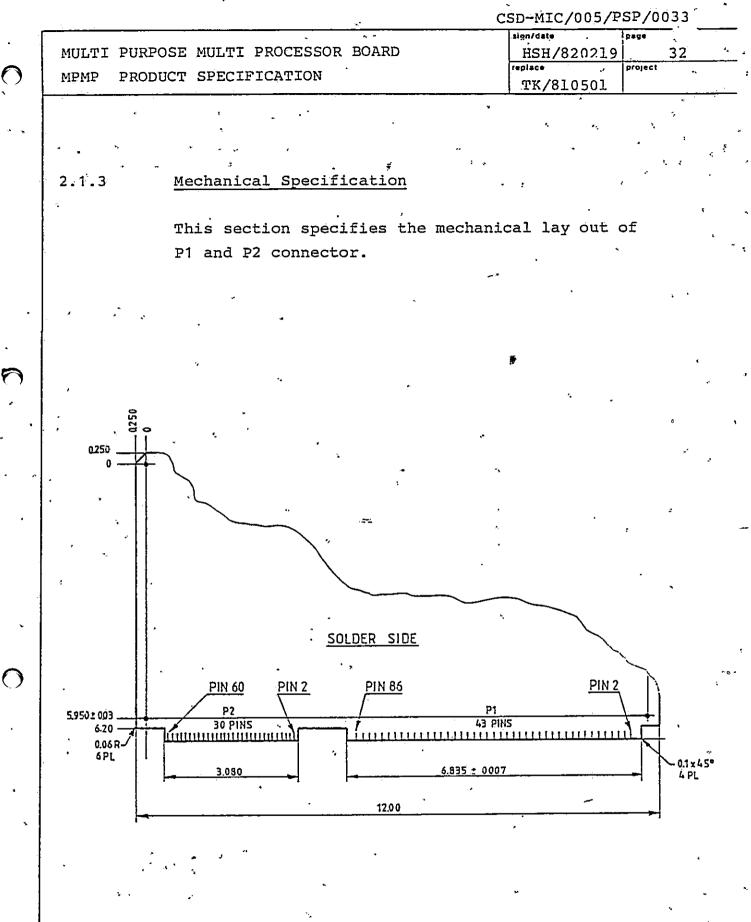

| -<br>- A       | 2.1.3 Mech. Specification                 |                  |                                                         |

| •              | 2.2 Multiboard Interface                  | 4. (1)<br>4. (1) |                                                         |

|                | 2.2.1 Signal Specification                | •<br>**          | •                                                       |

| <u>.</u>       | 2.2.2 Electr. Specification               |                  |                                                         |

|                | 2.2.3 Mech. Specification                 | 1                | . ,                                                     |

| 2              | 2.3 Floppy Disc Interface                 | <u>.</u>         | • •                                                     |

|                | 2.3.1 Signal Specification                | 2 / /            | ه <u>۱</u>                                              |

| •              | 2.3.2 Electr. Specification               |                  | <b>.</b>                                                |

| •              | 2.4 Line Communication Interface          |                  |                                                         |

| ۰.<br>۲.       | 1. z                                      | •                |                                                         |

|                | 2.4.1 Signal Specification                | × *              | * <u>-</u>                                              |

| 4 <sup>1</sup> | 2.4.2 Electrical Specificati              | on               | 4                                                       |

| * e<br>ç       | 2.4.3 Mech. Specification                 |                  |                                                         |

|                | 2.5 Boot Load PROM                        |                  | ۰۰<br>ج                                                 |

| - + ;          | 2.5.1 Signal Specification                | · ·              | ې چې کې<br>مړينې کې کې د                                |

|                | ·                                         |                  | -                                                       |

1

7

.. •

۰.

۲

, K

• 5

Ó

é

, O

×

0

| •                                     |                                                     | CSD-MIC/005/                          | Inane                                    |

|---------------------------------------|-----------------------------------------------------|---------------------------------------|------------------------------------------|

|                                       | MULTI PURPOSE MULTI PROCESSOR BOARD                 | HSH/820219                            |                                          |

| 0                                     | MPMP PRODUCT SPECIFICATION                          | replace<br>TK/810501                  | project                                  |

| 3                                     |                                                     |                                       | · · · · · · · · · · · · · · · · · · ·    |

| ٤4                                    |                                                     |                                       | ×<br>* , , , .                           |

|                                       | 2.5.2 Electr. Specification                         |                                       |                                          |

|                                       | 2.5.3 Mech. Specification                           | ° i                                   | * *                                      |

| · · ·                                 | 2.6 Mathematic Co-processor                         | -                                     | · · · ·                                  |

|                                       | 2.6.1 Signal Specification                          |                                       | 3                                        |

|                                       | , 2.6.2 Electr. Specification                       | s <sup>1</sup> ,                      | مر می می<br>چو<br>مرجع می می می          |

| •                                     | 2.6.3 Mech. Specification                           | ≻                                     |                                          |

| •                                     |                                                     | w.                                    | ج.<br>۱,                                 |

| ۰.                                    | 3. Operation                                        |                                       | 5. A<br>5.                               |

| ••                                    |                                                     | * t                                   | the second second                        |

| $\bigcirc$                            | 3.1 Address Map                                     |                                       |                                          |

|                                       | 3.2 Map Function                                    |                                       | ام <sup>د</sup>                          |

| 1<br>1<br>1                           | 4. Options                                          | *                                     | · · · · · · · ·                          |

| , *<br>•                              |                                                     | 4 *                                   |                                          |

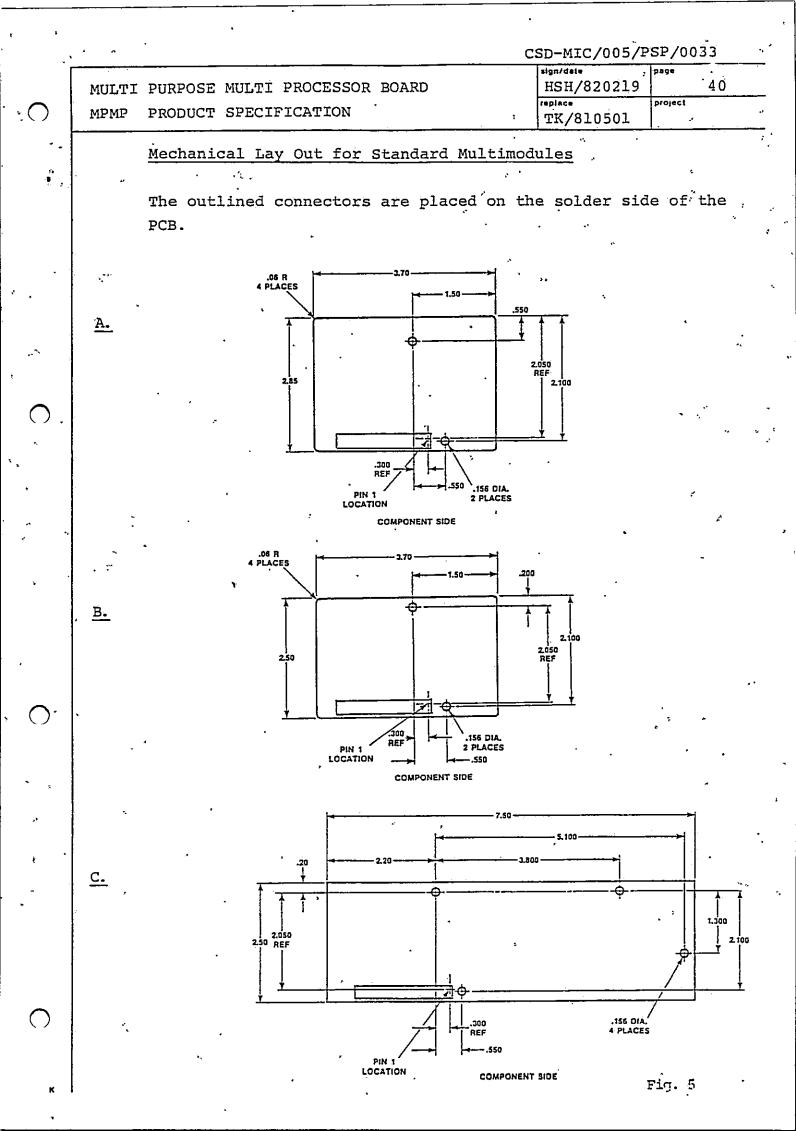

| من ا                                  | 4.1 Multimodules                                    | *<br>* :                              | 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1 |

|                                       | 4.1.1 TDX-Interface                                 | *                                     | *** %                                    |

| :                                     | 4.1.2 PAM Interface                                 | ۰.                                    | * *                                      |

| * *                                   | 4.1.3 UPI Interface<br>4.1.4 Line Communication Int |                                       | n.                                       |

|                                       | 4.1.4 Line Communication int<br>4.2 Battery Back-Up | ,<br>,                                | 1. 1.<br>1.<br>1.                        |

|                                       | 4.2 Ballery Back-Up                                 | ۳<br>۳                                |                                          |

|                                       | 5. Power Specifications                             | م<br>م م<br>م                         |                                          |

| ية.<br>بە ب                           | J. IOWEL OPECIFICATIONS                             | ¢                                     | 1° ý                                     |

|                                       | 6. Environmental Specifications                     | ,                                     |                                          |

| · · ·                                 |                                                     | •                                     |                                          |

|                                       |                                                     |                                       | 2                                        |

| • • • • • • • • • • • • • • • • • • • |                                                     | a*                                    | ž                                        |

|                                       | The following names used in this o                  | document are                          | · · ·                                    |

| ş                                     | trademarks of INTEL:                                | 2.<br>2.                              |                                          |

| *                                     |                                                     |                                       | × 2                                      |

| ۰ <sup>۲</sup>                        | MULTIBUS, MULTI MODULE, SBC,                        | iSBX                                  | · · ·                                    |

| •                                     |                                                     |                                       | 5 "                                      |

| .e5                                   |                                                     |                                       |                                          |

| -                                     |                                                     | •<br>•                                | ×.                                       |

|                                       |                                                     | <b>`</b>                              |                                          |

| $\sim$                                |                                                     | · · · · · · · · · · · · · · · · · · · | a an |

| • •                                   |                                                     |                                       | • •                                      |

|                                       |                                                     | ,                                     | ~                                        |

| ĸ                                     |                                                     |                                       | *                                        |

| ,                                     | • ,                                                 |                                       |                                          |

|            |       |         |                 |       | 1 | sion/date                             | page    |   |

|------------|-------|---------|-----------------|-------|---|---------------------------------------|---------|---|

|            | MULTI | PURPOSE | MULTI PROCESSOR | BOARD | 1 | HSH/820219                            | 1.      | 2 |

| 1          | MDMD  | DODUCE  | CDECTETCARTON   |       | • | replace                               | project |   |

|            | MPMP  | PRODUCT | SPECIFICATION   | ·     |   | TK/810501                             |         |   |

| - <b>г</b> |       |         |                 |       |   | · · · · · · · · · · · · · · · · · · · |         |   |

### Scope

... ( )

The scope of this document is to specify the interface characteristics of the Multi Purpose Multi Processor Board ( $(MP)^2$ ) which is a general microcomputer board interfacing to MULTIBUS (Intel) and to a wide range of communication and storage systems as TDX-Bus, PAM lines, UPI lines, Floppy Discs, communication I/F etc.

The document specifies only the hardware and that part of the firmware which includes address decoders, state controllers etc., while software is outside the scope of this specification.

•

|            | MULTI PURPOSE MULTI PROCESSOR BOARD | HSH/820219 | 2 <sup>3</sup> |   |

|------------|-------------------------------------|------------|----------------|---|

| $\bigcirc$ | MPMP PRODUCT SPECIFICATION          | TK/810501  | project        | - |

# Applicable Documents

TBS

• \*

۰.

Ö

$\bigcirc$

0

· \_ . ·

•

. . . .

MULTI PURPOSE MULTI PROCESSOR BOARD MPMP PRODUCT SPECIFICATION

0.

|   | • •        |         |   |

|---|------------|---------|---|

| Ì | sion/d=+-  | page    | • |

| 1 | HSH/820219 | - 3     |   |

|   | replace .  | project |   |

|   | TK/810501  | 4       |   |

#### SYSTEM ADVANTAGES

The Multi Purpose Processor, (MP)<sup>2</sup> card, is a standard micro computer module designed and manufactured, by CHRISTIAN ROVSING A/S (CRAS).

The module is a highly integrated single card, dual processor micro computer system with a wide range of on-board interfaces and options, which makes it expandable to meet application requirements ranging from very small to very large systems.

- Mechanically and electrically compatible with INTEL'S SBC boards, making the single board multiprocessor ((MP<sup>2</sup>)) share a large no. of commercially available packing and power supply options with INTEL's multibus boards (SBC).

- Standard INTEL Multibus Interface (IEEE796) making the single board multiprocessor expandable with standard Multibus boards, (available from INTEL and hundreds of commercial vendors); such as Parallel I/O. Analog interface boards, memory boards, processor boards, hard disc interface, etc.

- (MP<sup>2</sup>) highly compatible with CRAS standard communication interfaces (LTU), making communications S/W (Protocols) interchangeable.

|     | MULTI PURPOSÈ  | MULTI PROCESSOR BOARD | sign/date<br>HSH/820219 | page 4    |

|-----|----------------|-----------------------|-------------------------|-----------|

| ÷ . | MPMP " PRODUCT | SPECIFICATION         | TK/810501               | project * |

On-board connectors and Multimodule I/F for expansion with up to 3 standard INTEL iSBX Multimodule or CR custom interface modules

The (MP)<sup>2</sup> may be installed with two processors, one processor (8088 or 280) or without any processors as a general memory and input/output board.

The Main Processor (8088) may be extended with on-board mathematic co:-processor (8087).

On-board RAM 128 K byte, divided as 64 K byte local RAM on each of the two processors, and globally the total 128 K RAM is accessible by both processors.

PROM area (standard 4 or 8 K byte) may be extended with on-board standard INTEL or CR custom PROM extension card to max. 64 K byte.

On-board Floppy Disc interfaces for up to four floppy disc drives.

Two on-board serial interfaces, one limited (terminal) and one full modem interface capable of synchroneous/asynchroneous operation with HDLC, SDLC, BSC etc.

| 4 - 1<br>7-1 | MULTI PURPOSE MULTI PROCESSOR BOARD | sign/date<br>HSH/820219 | page    |

|--------------|-------------------------------------|-------------------------|---------|

| )            | MPMP PRODUCT SPECIFICATION          | TK/810501               | project |

On-board TDX or X-net interface, by CR custom interface module.

On board UPI OF PAM serial process control interface and drivers, by CR Custom interface module each capable of handling 2 UPI or PAM lines, making hybrid systems combining UPI and PAM circuits possible.

|                                     | sign/date            | page    |

|-------------------------------------|----------------------|---------|

| MULTI PURPOSE MULTI PROCESSOR BOARD | ISH/820219           | 6       |

| MPMP PRODUCT SPECIFICATION          | replace<br>TK/810501 | project |

#### INTRODUCTION

The Multi Purpose Multi Processor ((MP)<sup>2</sup>) specified in this document is a high performance dual microcomputer configured with a Multibus interface by which the module may communicate with slavemodules as well as master modules.

The two microcomputers are configured as general microcomputers with common access to all on board in- output devices, to the Multibus and to all on board memory, except for that part of each processors memory being reserved to contain its program code, which optionally can be protected via the address decoder.

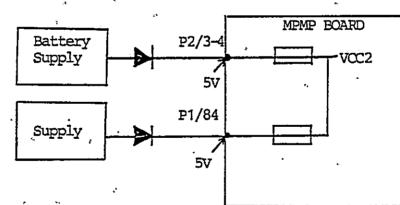

Both computers may be equipped with up to 64 K memory (Dynamic RAM) which all may be battery backed up to ensure no data loss during Power failures.

To obtain the highest degree of expandability the internal bus structure  $((MP)^2$  Bus) is connected to three 36 pin on board connectors to which Multimodules and CR custom interface modules may be plugged in.

To control the Multibus  $(MP)^{\frac{2}{2}}$  Bus and its interfaces a central Bus Control And Arbiter Logic is implemented.

A PROM area is interfaced to the (MP)<sup>2</sup> Bus. This area is normally only accessed during a boot load procedure or after a system-reset when the programs for builtin-test are accessed. This PROM area is 4K Byte bus is extendable to 64K by use of a small on board extension board.

3

$\bigcirc$

Ä

()

C

| :                   | •.                                              | $\checkmark$                                | ÷ •                  | -                                        |                                        |

|---------------------|-------------------------------------------------|---------------------------------------------|----------------------|------------------------------------------|----------------------------------------|

| · 0                 | ······································          | ÷ •                                         | :                    | 4 1                                      |                                        |

| ور<br>• میرد<br>• • | ب<br>ب<br>ب                                     | •<br>•<br>•                                 |                      | * •.<br>* •                              |                                        |

|                     | Picht Critiscus BOAD<br>Hulth 10-POC            | HULTHOUVE,                                  |                      |                                          |                                        |

| s.                  |                                                 | · ·                                         | -<br>-               |                                          |                                        |

| -                   | τ.                                              | · · ·                                       |                      | ,                                        | * .<br>*<br>*                          |

|                     | NT2                                             | -                                           | · · ·                | T                                        |                                        |

| 0.                  | (MP) <sup>2</sup><br>Onboard Extension Overview | Totale 97-62-69<br>Drawn TK/JFL<br>Parts no | A5210411d            | 10.110 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | 2<br>32-0306                           |

| •                   | · · · · · · · · · · · · · · · · · · ·           | Pret no                                     | Sinnet 1 of 1 shoets |                                          | ······································ |

CSD-MIC/005/PSP/0033.

| MULTI PURPOSE MULTI PROCESSOR BOARD | •. | HSH/820219 | page    | 9 | *  | -<br>- |

|-------------------------------------|----|------------|---------|---|----|--------|

| MPMP PRODUCT SPECIFICATION          |    | TK/810501  | project |   | ** | -      |

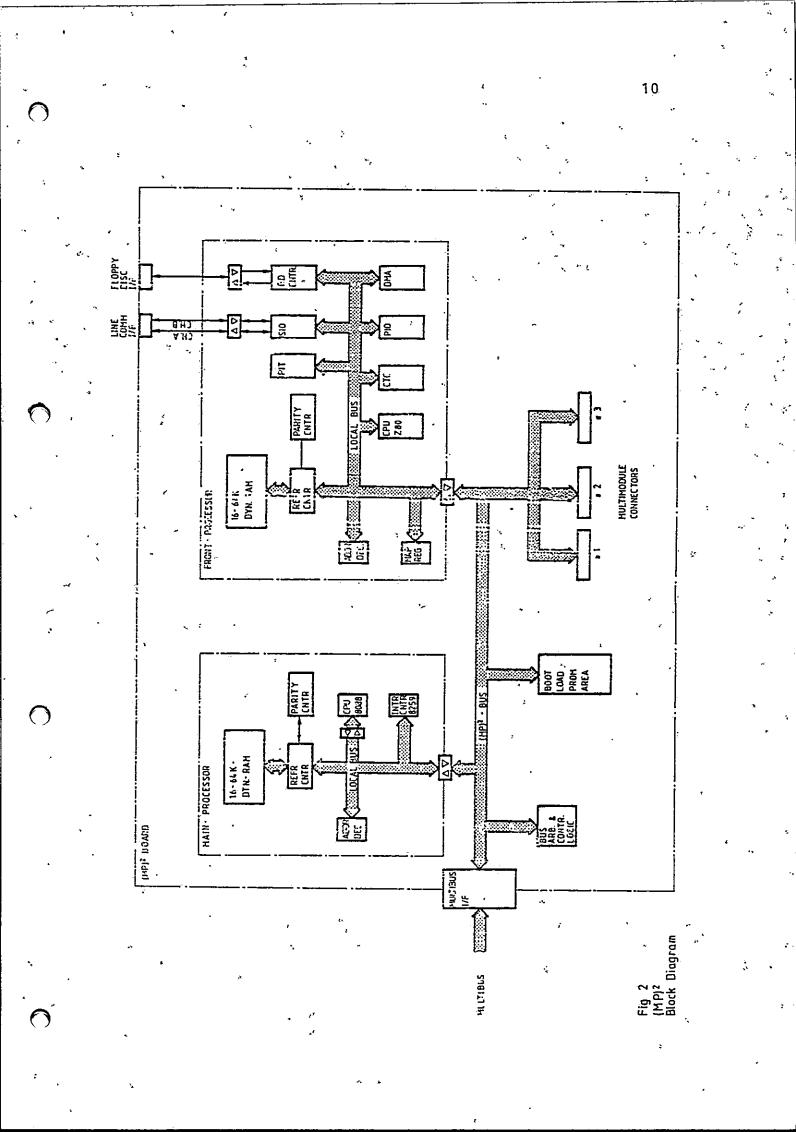

Functional Summary

This brief functional description is based on the block diagram on fig. 2. The description handles only special interfaces and conditions as the (MP) is designed ot be a simple general microcomputer with bidirectional access to a common bus system. All referred circuits are implied to be wellknown by the reader and only the HW interfaces and the addresses are included in this document.

The real performance of this module will not be obtained without an operating system controlling the interface between the two systems and the use of all . common addressable devices as the DMA, the MAP register etc. by f.x. semaphore protection technics.

#### ]

1.2

1.1

# Block Diagram

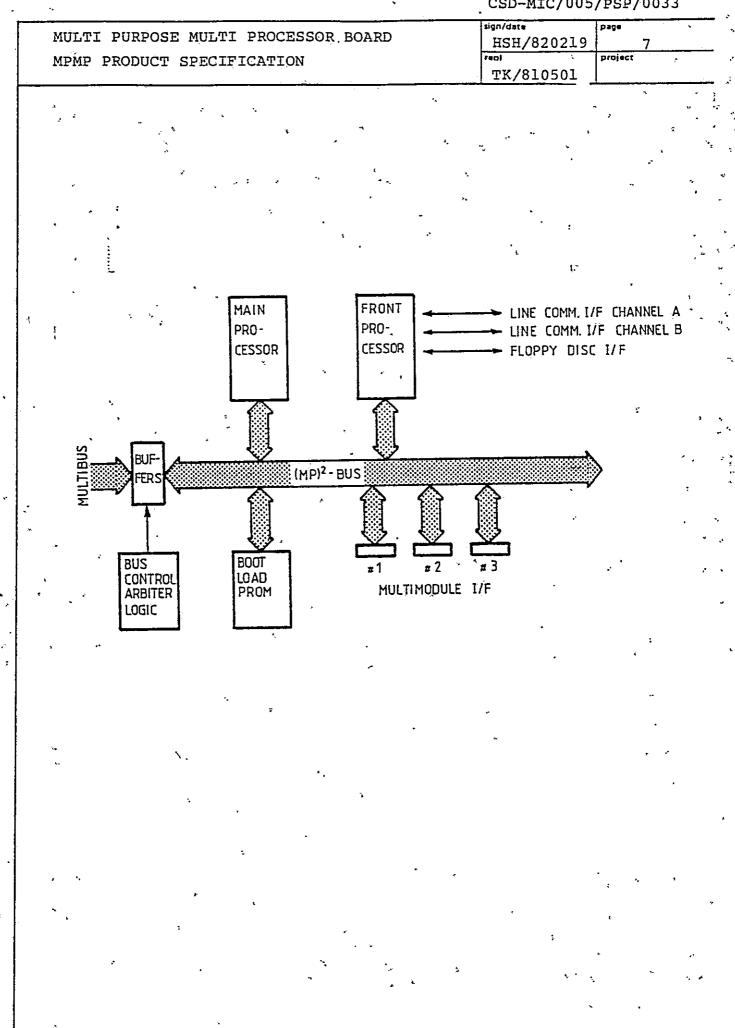

Fig. 2 shows the (MP)<sup>2</sup> Block Diagram containing common internal husstructure called (MP)<sup>2</sup> - Bus interfacing to following logic functions:

- o Main Processor

- o Front Processor

- o Multibus Interface

- o Multimodule Interface

- O Bus Arbiter & Control Logic

- o Boot Load Prom

The following sections describe briefly the functions and control of these logic blocks.

| •. | MULTI | PURPOSE | MULTI  | PROCESSOR  | BOARD | sign/dato<br>HSH/820219 | side    | 11 |  |

|----|-------|---------|--------|------------|-------|-------------------------|---------|----|--|

|    | MPMP  | PRODUCT | SPECII | FICATION - |       | erstatter<br>TK/810501  | projekt |    |  |

#### Main Processor

The Main Processor is a microcomputer with its own local bus, 8 bit data bus and 20 bit address bus allowing control of 1 MByte memory.

The Main Processor consists of a CPU ( 18088 ), an interrupt controller ( 18259 ), a 16/64K Ram-memory with parity control and a (MP)<sup>2</sup>-bus interface. Refresh and control of the memory is automatic generated by the Ram interface circuit.

1.2.1.1 <u>CPU</u>

1,2.1

The CPU is configured in "Maximum Mode" for a well' defined multiprocessor control via a handshake sequence. Following pin configurations of the CPU must be observed :

Reset is activated by the Power Control Logic when the power supplies are below the defined levels and kept active about 40 msec after the levels have been re-established.

Reset may be supplied to, or activated from the multibus. See sect. 2.1.

<u>NMI</u> is activated by a parity error, by time out during (MP)<sup>2</sup>-bus access, by a watchdog alarm, or by Power Fail interrupt. NMI is ored together with NMI on Front Processor.

#### 1.2.1.2 Interrupt Controller

The Interrupt Controller ( i8259A ) is controlling following interrupts, all supplied from the Front Processor.

IR0 : INT MBT Interrupt from Multibus Interface

IR1 : Floppy Disc Controller

CSD-MIC/005/PSP/0033 -

| MULTI | PURPOSE | MULTI PROCESSOR | BOARD |       | sign/date<br>HSH/820219 | page     | 12                |   |

|-------|---------|-----------------|-------|-------|-------------------------|----------|-------------------|---|

| MPMP  | PRODUCT | SPECIFICATION   | • .   |       | TK/810501               | project  | т. <sub>н</sub> . |   |

|       |         | •               |       | · · · | -                       | <u> </u> |                   | — |

|   | . • • | IR2   |            | CHANNEL ( | ) from PIT (8253)              |    |

|---|-------|-------|------------|-----------|--------------------------------|----|

| ٠ |       | IR3   |            | INTMP     | INTERRUPT FROM FRONT PROCESSOR |    |

|   |       | IR4 < | :          | N.C.      | · •                            | •. |

|   |       | IR5   | :          | MINTRO    | MULTIMODULE I/F - 0            | •• |

| • |       | IR6   | ` <b>:</b> | MINTR1    | MULTIMODULE I/F - 1            |    |

| 1 |       | IR7   |            | MINTR2.   | MULTIMODULE I/F - 2            |    |

|   |       |       | •          | 4 .       | 1 4                            |    |

#### Front Processor

The Front Processor is a microcomputer with its own local bus, 8 bit databus and 16 bit address bus extended during global access with a 4 bit MAPregister.

The Front Processor consists of a CPU, a 16/64K RAMmemory with parity control, a (MP)<sup>2</sup>-Bus interface, a timer, a DMA and some in- output circuits.

1.2.2.1 <u>CPU</u>

1.2.2

The CPU is a Z80A on which following pin connections must be observed:

<u>Reset</u> is activated by the Power Control Logic when power supplies are below the defined levels and kept active about 40 msec after the levels have been re-established.

Reset may be supplied to, or activated from the Multibus.

<u>NMI</u> is activated by a parity error, by timeout during (MP)<sup>2</sup>-bus access, by watchdog alarm or by Power Fail interrupt. NMI to FP and MP are ored together.

1.2.2.2 <u>CTC</u>

The Timer-circuit ( Z80-CTC ) is configured as timer and interrupt controller as follows :

J

••

|                         | · · · · ·                           | CSD_MIC/005             | /PSP/0033            |

|-------------------------|-------------------------------------|-------------------------|----------------------|

|                         | MULTI PURPOSE MULTI PROCESSOR BOARD | sign/dato<br>HSH/820219 | aide<br>13           |

| $\overline{\mathbf{O}}$ | MPMP PRODUCT SPECIFICATION          | erstatter               | projekt              |

|                         |                                     | TK/810501               | <u> </u> ·           |

|                         |                                     |                         | ·                    |

|                         | CHO : Interrupt from DMA (EOP)      | ,                       |                      |

|                         | CHI : Floppy Disc-interrupt         | , :                     |                      |

| •                       | CH2 : Software Timer.               |                         |                      |

|                         | CH3 : Interrupt from Mainproce      |                         | * .                  |

|                         | -Jumper Possibility for             |                         | · ·                  |

|                         | from Multibus Interface             | instead of.             | the interrupt        |

| 4                       | from the Mainprocessor.             |                         | 2 <sup>41</sup><br>- |

|                         |                                     |                         | ۳<br>پر ۲            |

|                         | 1.2.2.3 <u>DMA</u>                  |                         | 4                    |

| $\mathbf{O}$            |                                     | <i>c</i>                | · · · ·              |

|                         | The DMA controller Am9517A is co    | ntigured as             | follows:             |

|                         |                                     |                         |                      |

| ·.,                     | CHO : Floppy Disc controller.       |                         |                      |

|                         | CH1 :                               | <b>N</b>                | د <sub>و</sub>       |

|                         |                                     |                         | •                    |

| •                       | CH2 : Z80-SIO channel A.            |                         |                      |

|                         |                                     |                         |                      |

|                         | CH3 : Z80-SIO channel B.            | •                       |                      |

| •                       |                                     |                         |                      |

|                         | CHO and CHL are also used during    | memory to m             | emory                |

| 7-                      | transferes.                         |                         | • • • •              |

| $\circ$                 | · · ·                               |                         |                      |

|                         | The DMA programming: 1. Normal      | timing                  | 4                    |

|                         | 2. Late wr                          | ite                     |                      |

|                         | 3. DREQ ac                          | tive high               | ~                    |

| •                       | 4. DACK ac                          | tive low                | •                    |

| **                      |                                     |                         |                      |

|                         | 1.2.2.4 <u>SIO</u>                  |                         |                      |

| 3                       |                                     |                         |                      |

|                         | The line communication interface    |                         |                      |

|                         | dualized serial interface with V    | 24/V28 drive            | rs/re-               |

|                         | <b>,</b>                            |                         | c.                   |

| * .                     |                                     | ¥                       |                      |

| · 0                     |                                     | **<br>**                |                      |

|                         | · · ·                               |                         |                      |

| • •                     | *                                   |                         |                      |

•

, X

<u>م</u>

· ·

| CSD-MIC/005/PSP/0033 | CSD-MIC. | /005 | /PSP/ | 0033 |

|----------------------|----------|------|-------|------|

|----------------------|----------|------|-------|------|

| MULTI PURPOSE |               | ISH/820219           | page .               | -4 |

|---------------|---------------|----------------------|----------------------|----|

| MPMP 'PRODUCT | SPECIFICATION | replace<br>TK/810501 | biolečt <sup>s</sup> |    |

Further specification of the interface is found in section 2.4.

Channel A : Extended Line Communication Interface. Channel B : Limited Line Communication Interface.

The Z80-SIO may be serviced by one DMA channel per serial interface, receive or transmit direction selected by software, or it could be serviced in an interrupt or polling scheme.

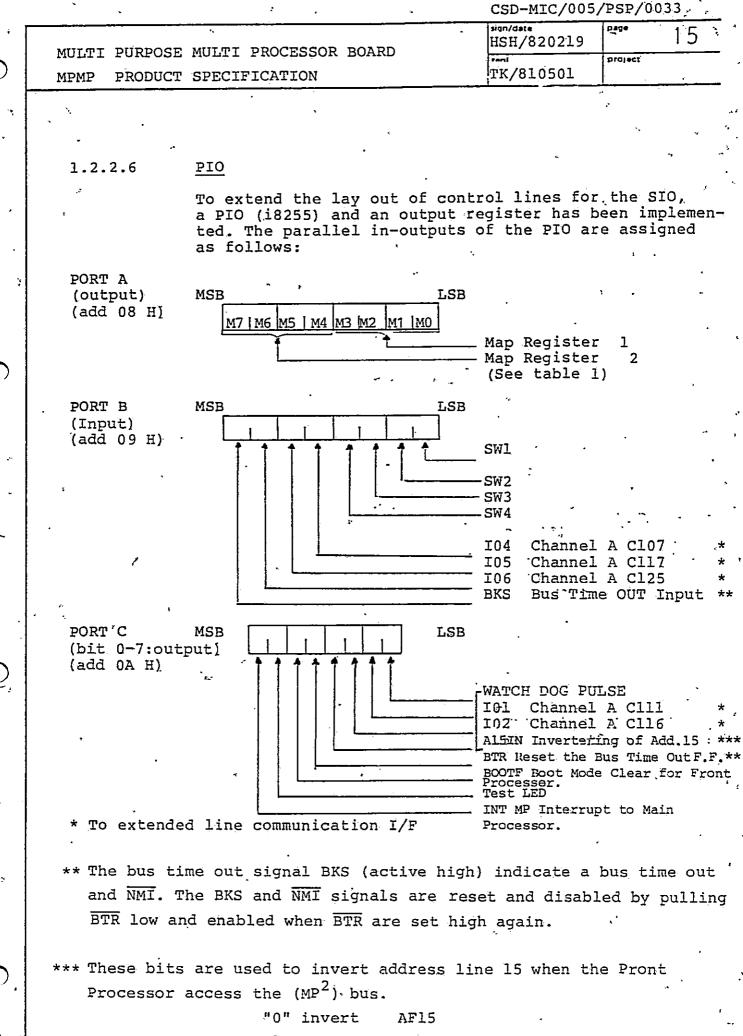

1.2.2.5 PIT 8253

ceivers.

| Channel 0: | Interrupt to Main Processor Bus Time For (8259A interrupt line 2) MP <sup>2</sup> bus. |

|------------|----------------------------------------------------------------------------------------|

| Channel 1: | Baudrate generator to Channel A.                                                       |

| Channel 2: | Baudrate generator to Channel B.                                                       |

Input frequency to the PIT is 1,25 MHz.

"1" non invert AF15

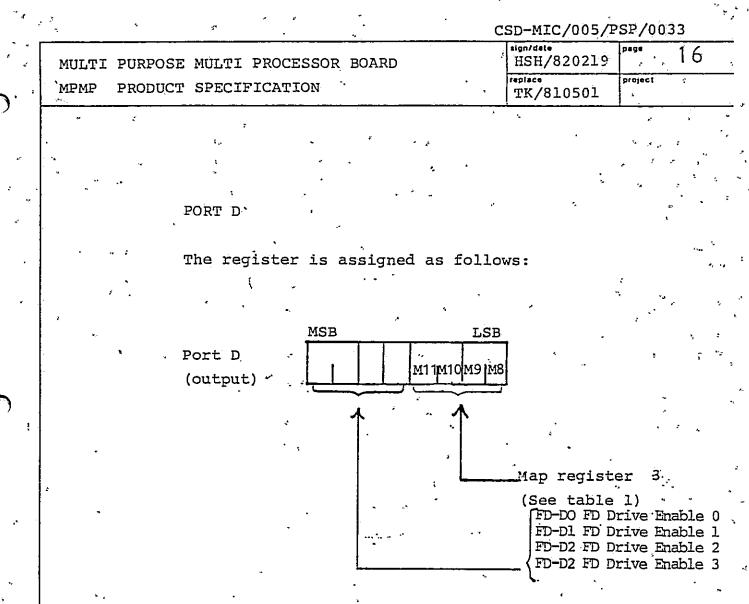

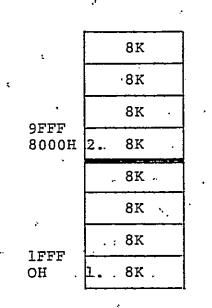

To extend the area addressed directly by Front Processor and DMA, a tripple MAP register is implemented. The control of these registers is rather complicated and must be executed under semaphore protection by a general operating system. (See sect. 3.1).

| MULTI PURPOSE MULTI PROCESSOR BOARD | • | HSH/820219           | 17 .      | • |

|-------------------------------------|---|----------------------|-----------|---|

| MPMP PRODUCT SPECIFICATION          |   | replace<br>TK/810501 | project . | • |

#### 1.2.2.7 Floppy Disc. Controller

A general floppy disc. controller (WD 1797 or 1793) has been implemented for accessing one to four single or double density, single or double sided, 8" or 51/4" floppy disc. drives.

The controller is connected to a DMA channel and to an interrupt-input of the Front Processor which means that data transfers are normally controlled by this processor.

### 1.2.2.8 Interrupt Priority

The Z80-CTC and Z80-SIO is connected in a daisy chain interrupt structure where the Z80-CTC has highest priority.

#### 1.2.3 <u>Multibus Interface</u>

The structure of the Multibus is built upon the masterslave concept where the master device in the system takes control of the Multibus interface and the slave device upon decoding its address, acts upon the command provided by the master. Multimasters are allowed to interface the Multibus, controlled by a simple arbitor/grant technic.

The (MP)<sup>2</sup> Multibus interface is provided to act as master or as an intelligent slave on the Multibus addressing 1M byte on an 8-bit databus structure. The interface is buffered and controlled according to the multibus specifications. (sect. 2.1.)

| MULTI | PURPOSE | MULTI PROCESSOR | BOARD | 4 | ; ~ | H5H/820219 | page    | 18 - |

|-------|---------|-----------------|-------|---|-----|------------|---------|------|

| MPMP  | PRODUCT | SPECIFICATION ' |       |   |     | TK/810501  | project |      |

# Multimodule Interface

On the (MP)<sup>2</sup> board three connectors are placed for interfacing standard iSBX modules or special purpose/function modules.

Each of the three connectors are addressed in a separate I/O area of 16 consecutive addresses.

Interrupt request lines are connected to main processor but DMA-request lines have no connection on the (MP)<sup>2</sup>-board.

## 1.2.5. Bus Arbiter & Control Logic

The (MP)<sup>2</sup>-bus includes an 8-bit databus, 20-bit address bus and a control bus.

The interfaces to the bus are seperated in the slave interfaces (multimodule I/F) and the master/slave interfaces (Multibus I/F, Main Proc., Front Proc.)

Seen from the Bus-Arbiter and Control Logic there is no difference between the three interfaces and the complete function is issued by a state controller performing a rotating access-priority scheme and a very fast arbitration mechanism operating with the functions request/grant/release.

Overleaf is shown timing diagram for a (MP)<sup>2</sup> bus access.

|     |                                                      | ð                                       | CSD-MIC/005   | /PSP/0033 |

|-----|------------------------------------------------------|-----------------------------------------|---------------|-----------|

|     | MULTI PURPOSE MULTI PROC<br>MPMP PRODUCT SPECIFICATI |                                         | HSH/820219    | project   |

|     | MPMP PRODUCT SPECIFICATI                             |                                         | TK/810501     | <u> </u>  |

|     |                                                      | ۸                                       |               |           |

| :   | 2.                                                   |                                         |               |           |

|     | (MP <sup>2</sup> ) BUS ACCESS TIMING                 | * * *                                   |               | •         |

|     |                                                      |                                         | *             | ٤٢        |

|     |                                                      |                                         | *             | y.        |

|     |                                                      | · ·                                     | •             |           |

|     | or 10 MT-                                            | <u>nnnn</u> ń                           | nnnn          | 'n ~ ·    |

|     | CLK 10 MHz                                           |                                         |               | J L_      |

|     |                                                      |                                         |               |           |

|     | REQ                                                  | _ / · \                                 |               |           |

|     | (generated by a                                      |                                         |               |           |

| ·   | local address de-                                    |                                         |               | .         |

|     | coding)                                              | }                                       |               | /. •      |

|     | GRANT                                                | t                                       |               |           |

|     | (to master                                           | /                                       | $\frac{1}{1}$ | \         |

|     | RSP                                                  | ;;                                      |               | <u></u>   |

| 3 J | (from responding                                     |                                         | i             |           |

|     | dev.)                                                |                                         | (             |           |

|     | ACK                                                  | / · · · · · · · · · · · · · · · · · · · |               |           |

|     | (-generated by                                       | - Le                                    |               |           |

|     | the control logic)                                   |                                         |               |           |

|     | Local Wait                                           | <u> </u>                                |               |           |

|     | WAIT on (MP <sup>2</sup> ) Bus                       |                                         | • /           | * /       |

|     |                                                      | Tunn /                                  |               | / ·       |

|     | Data/addr. Bus                                       | · `*                                    | /             |           |

|     | (-on the (MP <sup>2</sup> ) Bus)                     |                                         | >             |           |

$\bigcirc$

•\*

0

Fig. 3

| Γ           |         |                   | CTP MIT  | LTI PROCESSO |                                | CSD-MIC/005/<br>sign/date<br>HSH/820219 | page       | 20                                     |

|-------------|---------|-------------------|----------|--------------|--------------------------------|-----------------------------------------|------------|----------------------------------------|

|             | MOLTI   |                   |          | ECIFICATION  |                                | replace<br>TK/810501                    | project    | ······································ |

| ┝           |         |                   | <u> </u> | ¥<br>        |                                |                                         |            | <br>                                   |

|             |         |                   |          | *            | * ``                           |                                         | ÷          | به <sup>م</sup> ر ا                    |

|             |         | ,                 | 2        | ·· ·         | -                              | e<br>Ng s                               | •          |                                        |

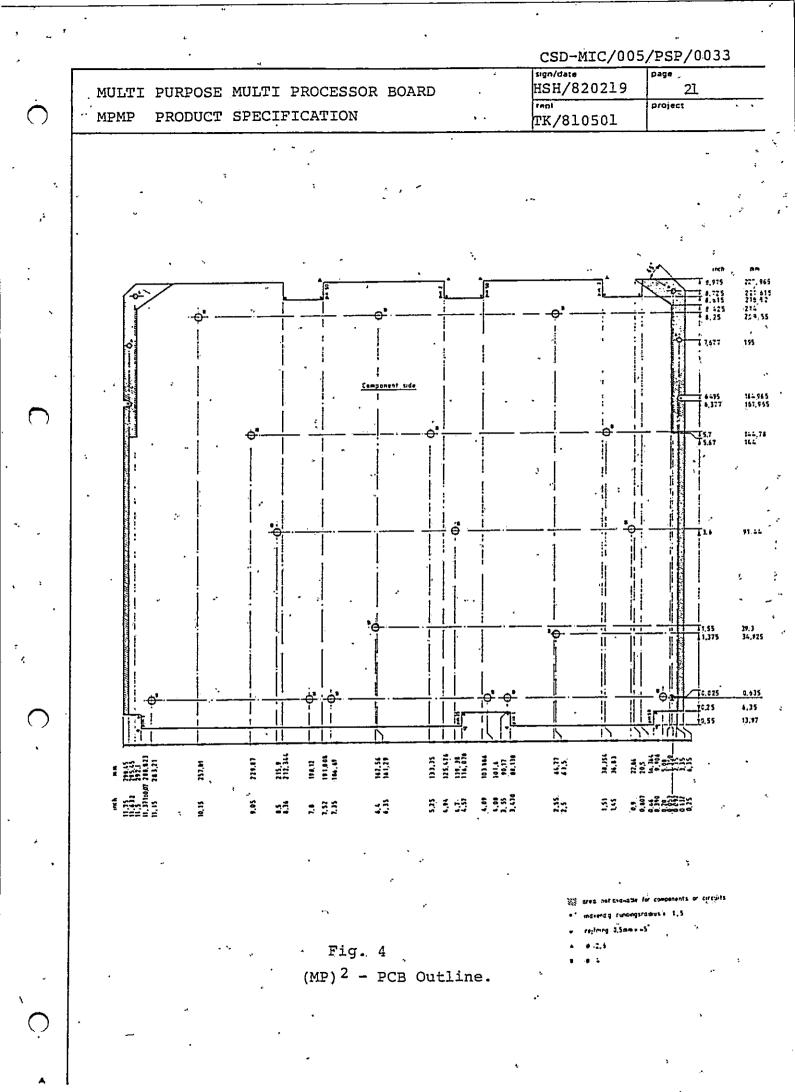

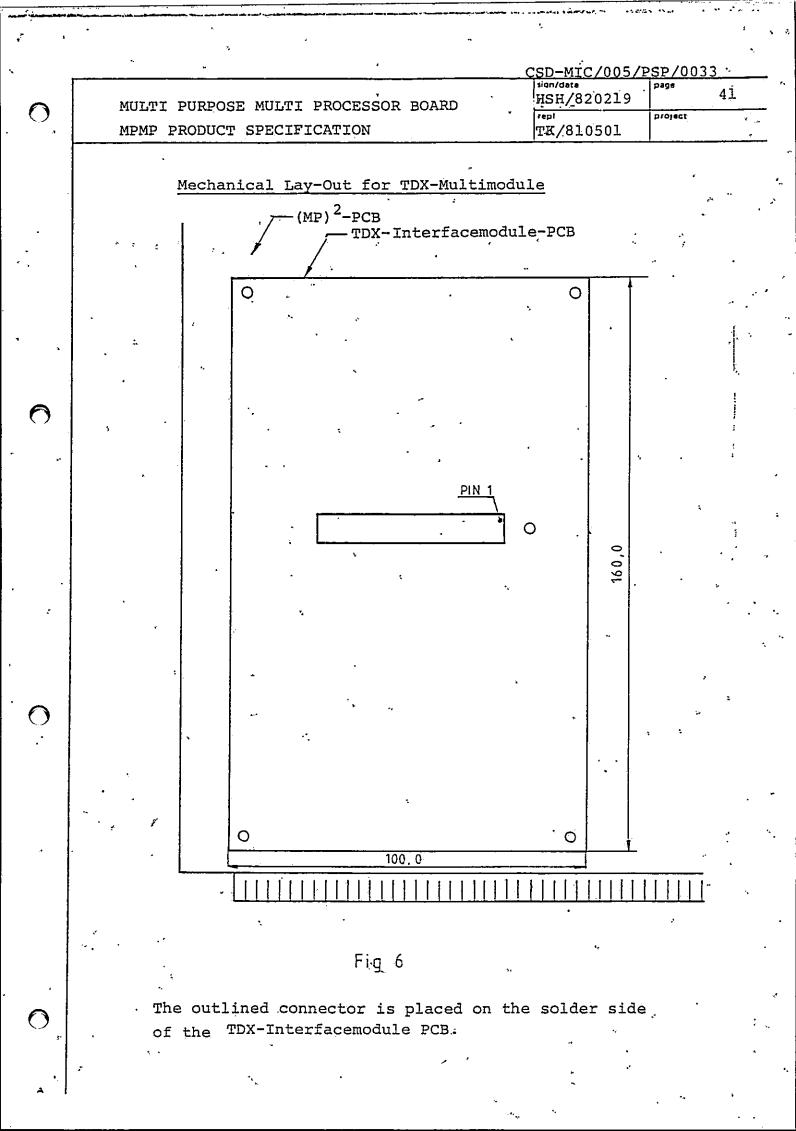

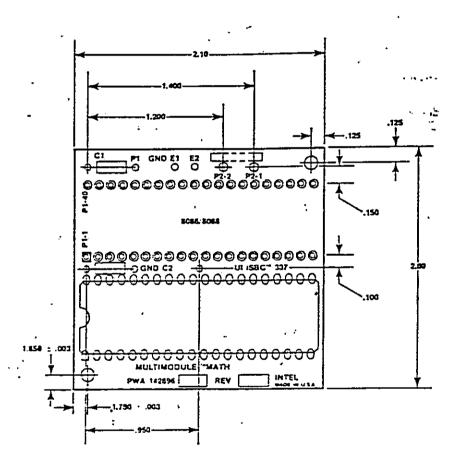

|             | l       | . 3. <sup>-</sup> | Mech     | anical Layou | <u>t</u> · · · · ·             |                                         |            | :                                      |

|             | ه'<br>۲ |                   |          |              |                                |                                         |            | **<br>                                 |

|             | <i></i> | •                 | Fig.     | 4 shows the  | outline of the                 | (MP) board.                             |            | ءَ<br>ج                                |

|             | •       |                   | Conn     | ector Assign | ment ·                         | . :                                     |            | *<br>~<br>*                            |

|             |         | ه                 | P3:      | Floppy Disc  | Interface.                     |                                         |            | ~                                      |

|             | •       |                   | P4:      | Pin 0-25     | Extended Line Co<br>Interface, | ommunication                            | •          |                                        |

|             |         |                   |          | Pin 26-50    | Limited Line Con<br>Interface. | munication                              | ··         |                                        |

|             |         |                   | J1:      | Multimodule  | Interface # 1.                 |                                         |            | * ~                                    |

| ŀ           |         |                   | J2:      | Multimodule  | Interface # 2                  |                                         | · .        |                                        |

|             |         | *                 | J 3:     | Multimodule  | Interface # 3.                 |                                         |            |                                        |

|             | • -     |                   | P1:      | Multibus In  | terface .                      | -                                       |            | •                                      |

| •<br>•<br>• | *       |                   | P2:      | Optional Bu  | s (Part of Multik              | ous spec.)                              | ,          | 5 .<br>t <sub>a</sub>                  |

|             |         | · '               |          | ,            |                                | £                                       | :<br><br>2 | , , , , , , , , , , , , , , , , , , ,  |

|             | •       |                   | •        |              |                                |                                         |            | •                                      |

|             |         |                   |          | ·            |                                |                                         |            | •                                      |

| ľ           |         |                   |          |              |                                | •                                       | •¢         | • . • •                                |

|             |         |                   | ï        |              | 3                              |                                         | I          | ~<br>;<br>t                            |

|             |         | ч<br>К            |          | х.<br>2      | , i ,                          | م<br>ب خ                                | *          | \$                                     |

į

. . . .

| MULTI | PURPOSE | MULTI  | PROCESSOR | BOARD |

|-------|---------|--------|-----------|-------|

| MPMP  | PRODUCT | SPECIE | FICATION  |       |

2.

$\bigcirc$

| HSH/820219 | page<br>22 - |

|------------|--------------|

| TK/810501  | tolect.      |

# INTERFACE SPECIFICATIONS

The  $(MP)^2$  interfaces to external devices via the edge connectors Pl, P2, P3, P4 and the on board connectors J1, J2, J3 and optionally for special purposes via the CPU socket and the Boot-load Promsocket.

In the following section all these interfaces will be specified in the matter of signals, mechanical as well as electrical sizes and values.

|   |       |         |                 |       | •                                     | page       |

|---|-------|---------|-----------------|-------|---------------------------------------|------------|

|   |       | DUDDOCE | MULTI PROCESSOR | POAPD | HSH/820219                            | 23         |

| 1 | MULTT | PURPUSE | MODIT PROCESSOR | BOARD | · · · · · · · · · · · · · · · · · · · | project    |

|   | MPMP  | PRODUCT | SPECIFICATION   | ~~    | <u>TK /810501</u>                     | <u>_</u> _ |

#### Multibus Interface

2.1.

The MULTIBUS interface is the flexible bus structure used to interface the family of SBC boards which include 8- and 16-bit single board computer, memory expansion boards, digital and analog I/O boards and peripheral controllers. It supports direct addressability up to one megabyte through 20-bit addresses and 8- and 16-bit data transfers.

The bus structure is built upon the master-slave concept where the master device in the system takes control of the MULTIBUS interface and the slave device, upon decoding its address, acts upon the command provided by the master. This handshake between master and slave devices allows modules of different speeds to use the MULTIBUS interface and allows data rates up to five million byte transfers per second.

Another important MULTIBUS feature is the ability to connect multiple master modules for multiprocessing configurations. The MULTIBUS interface provides control signals for connecting multiple masters either in a daisy-chain priority fashion or in parallel. With this latter arrangement, up to sixteen masters may share MULTIBUS resources.

The MULTIBUS Interface of the (MP)<sup>2</sup> is a limited MULTI-BUS Interface as defined in the following sections.

It may be configured as master module or as intelligent slave module.

| 2. 4  | 3       |                       | 2       | CSD-MIC/005/P           | SP/0033 |

|-------|---------|-----------------------|---------|-------------------------|---------|

| MULTI | PURPOSE | MULTI PROCESSOR BOARD |         | sian/dete<br>HSH/820219 | 24      |

| MPMP  | PRODUCT | SPECIFICATION         | تر<br>۲ | TK/810501               | project |

2.1.2.

$\bigcirc$

### Signal Specifications

Table 2 and 3 contain definitions of the signals which appear on the limited multibus connector P1 and . P2.

Timing specifications are according to those recommended for Multibus interfaces.

TABLE 2.

MULTIBUS Connector (P1) Signal Definitions

| SIGNAL                              | FUNCTIONAL DESCRIPTION                                                                                                                                                                                                                                                                     |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADR0/<br>ADRF/<br>ADR10/<br>-ADR13/ | Address. These 20 lines transmit the address of the memory location or I/O port to be accessed. For memory access, ADRO/ (when active) enables the even byte bank (DATO/-DAT7/) on the Multibus; i.e., ADRO/ is active for all even addresses. ADR13/ is the most significant address bit. |

| BCLK/                               | Bus Clock. Used to synchronize the bus contention logic on all bus masters.                                                                                                                                                                                                                |

| BPRN/                               | Bus Priority In. When low indicates to a particular<br>bus master that no higher priority bus master is re-                                                                                                                                                                                |

| · · · ·                             | questing use of the bus. BPRN/ is synchronized with<br>BCLK/.                                                                                                                                                                                                                              |

2

٩.

·· .

| MULTI PURPOSE MULTI PROCESSOR BOARD<br>MPMP PRODUCT SPECIFICATION<br>BPRO/ <u>Bus Priority Out.</u> In serial (dais<br>resolution schemes, BPRO/ must be<br>BPRN/ input of the bus master wit<br>bus priority.<br>BREQ/ <u>Bus Request</u> . In parallel priority<br>BREQ/ indicates that a particular<br>control of the bus for one or mor<br>BREQ/ is synchronized with BCLK/.<br>BUSY/ <u>Bus Busy.</u> Indicates that the bus<br>prevents all other bus masters fr<br>of the bus. BUSY/ is synchronized                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | e connected to<br>th the next lo<br>y resolution s<br>r bus master r<br>re data trans<br>is in use an<br>rom gaining co                                      | o the<br>ower<br>schemes<br>requires<br>fers.<br>nd<br>ontrol          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| TABLE 2 (CONTINUED)BPRO/Bus Priority Out. In serial (dais<br>resolution schemes, BPRO/ must be<br>BPRN/ input of the bus master wit<br>bus priority.BREQ/Bus Request. In parallel priority<br>BREQ/ indicates that a particular<br>control of the bus for one or mor<br>BREQ/ is synchronized with BCLK/.BUSY/Bus Busy. Indicates that the bus<br>prevents all other bus masters from                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | TK/810501<br>sy chain) price<br>the connected to<br>the the next lo<br>y resolution a<br>r bus master to<br>re data transt<br>is in use an<br>com gaining co | ority<br>o the<br>ower<br>schemes<br>requires<br>fers.<br>nd<br>ontrol |

| BPRO/ <u>Bus Priority Out.</u> In serial (dais<br>resolution schemes, BPRO/ must be<br>BPRN/ input of the bus master wit<br>bus priority.          BREQ/ <u>Bus Request</u> . In parallel priority<br>BREQ/ indicates that a particular<br>control of the bus for one or mor<br>BREQ/ is synchronized with BCLK/.         BUSY/ <u>Bus Busy.</u> Indicates that the bus<br>prevents all other bus masters from                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | sy chain) price<br>connected to<br>th the next lo<br>y resolution s<br>r bus master r<br>re data trans<br>is in use an<br>rom gaining co                     | ority<br>o the<br>ower<br>schemes<br>requires<br>fers.<br>nd<br>ontrol |

| BREQ/ indicates that a particular<br>control of the bus for one or mor<br>BREQ/ is synchronized with BCLK/.<br>BUSY/ <u>Bus Busy.</u> Indicates that the bus<br>prevents all other bus masters fr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | r bus master :<br>re data trans:<br>is in use an<br>rom gaining co                                                                                           | requires<br>fers.<br>nd<br>ontrol                                      |

| prevents all other bus masters fr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | com gaining co                                                                                                                                               | ontrol                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                              |                                                                        |

| CBRQ/ <u>Common Bus Request.</u> Indicates that<br>control of the bus but does not<br>trol. As soon as control of the<br>the requesting bus controller rai                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | presently hay<br>bus is obtain                                                                                                                               | ye con-<br>ned,                                                        |

| CCLK/ <u>Constant Clock</u> . Provides a clock<br>frequency for use by other system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -                                                                                                                                                            | nstant ,                                                               |

| DATO/<br>DAT7/ <u>Data</u> . These 8 bidirectional data in receive data to and from the address cation or I/O port. DAT7/ is the received at a state of the s | ressed memory                                                                                                                                                | 10-                                                                    |

| INIT/ <u>Initialize</u> . Reset the entire syste<br>ternal state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | cem to a knowr                                                                                                                                               | n in-                                                                  |