# minicomputer

## CR80 minicomputer

### Hardware

The CR80 mini is a modern, high speed, general purpose minicomputer designed by CHRISTIAN ROV-SING A/S and produced since 1975.

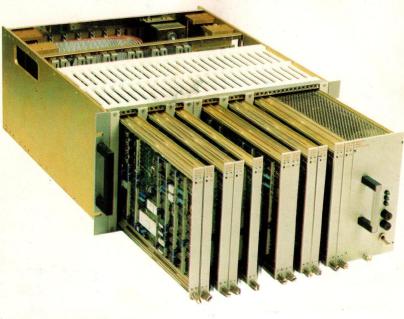

The emphasis has been on a modular and reliable hardware configuration, utilizing state of the art LSI's (Large Scale Integration) and fast Schottky TTL technology.

The philosophy behind the hardware architecture is that of interfacing completely selfcontained, two-ported modules (building blocks) via two types of ultra high speed backplane Bus's; the Main-Bus connecting all modules, and Sub-Bus's for local processing by a group of modules without loading the Main-Bus.

The CR80 mini standard catalogue shown overleaf now contains nearly one hundred different modules.

A complete range of processors, memories, I/O modules and application oriented modules ensures technically and economically correct solutions and extension capabilities in accordance with future needs, without lengthy interrupts of computer operations.

Outstanding among the CR80 minicomputer building blocks are:

- A peripheral processor file management system, connecting data bases of up to 16 disk drives of 300 megabytes capacity via multicomputer ports to one or more CR80 minicomputers, relieving the main CPU's completely of disk and file related processing

- A fast serial I/O bus, the TDX-Bus (Time Divisioned Multiplexed), which extends the standard parallel I/O bus to several kilometers from the computer, and provides high speed communication at 1.6384 Mb/s between several hundreds of I/O devices, communication ports, terminals and computers. This greatly reduces the number of separate circuits required in many systems, so that many large and expensive multicore cables can be replaced by a single cable-pair.

- X-net, an upwards compatible serial multidrop TDX-Bus which can connect several thousand terminals, via wall outlets to one or more Host computers and central printing stations. The X-net makes it possible to access central computing power from every room in a building complex covering several kilometers in area, via a single cable-pair.

- An extensive range of microcoded communication ports covering most common line protocols.

|        |   |      |        |                  | 2-100   |           |            |        |         | Z#100=>PSH(15:13, DISABLE TIMER  |

|--------|---|------|--------|------------------|---------|-----------|------------|--------|---------|----------------------------------|

| 001198 | 1 | JOIE | ;      | LON              | 2#100   |           |            |        |         | ENIOG-PESHCIDELIST DISABLE FINES |

| 001199 |   |      |        |                  |         |           |            |        |         |                                  |

| 001199 | + | JUIF | 1      |                  |         | COUNT     | ANCY       | CHECK  | (1.9.0) | PROCESSING (ESG STATE 1)         |

|        |   |      |        | LUNGIIL          | DINAL P | EDUM      | DANCT      | LHELK  | LACI    | FROCESSING TESS STATE IN         |

| 001201 |   |      |        |                  |         |           |            |        |         |                                  |

|        |   |      |        |                  |         |           |            |        |         | G LRC PROCESSING:                |

|        |   |      | ESP030 |                  |         |           |            | 8.0    |         | G ERC PROCESSING.                |

| 001203 |   |      |        |                  | ESGVSN  |           |            |        |         | IF PRIMARY_ESS ACTIVE            |

| 001204 |   |      |        | I E Q<br>M3VC    |         |           | ESGPA      | 85     |         | THEN PVS_ADDR=>ADDR              |

| 001205 |   |      |        |                  |         |           |            |        |         |                                  |

| 001206 |   |      |        | IEQ              |         |           | ESGSV      | 3      | : .     | ELSE SYS_ADDR=>ADDR              |

| 001207 |   |      |        |                  | SYSES   |           |            | 85     | :       | ADDR-BASE=>ADDR                  |

| 001208 |   |      |        | SUB              |         |           |            |        |         | TOTAL_SIZE=>N                    |

| 001209 |   |      |        |                  | -XHNAME | +X45      | S12.X5     | KO DO  |         | N-1=>N                           |

| 001210 |   |      |        | ADDC             | -1      |           |            | RD     |         | N-1=>N                           |

| 001211 |   |      |        | MOD              | -       |           |            |        |         | N.ADDR=>PLRC                     |

| 212100 |   |      |        | NJAX             | 0.      | ×5        |            | 91     |         | N.AUUR=>PLRC                     |

| 001213 |   |      |        | NON              |         | 81        | PLRC       |        |         |                                  |

| 001214 |   |      |        | HOVE             | #FFFF   |           |            | R2     |         | #FFFF=>LRC                       |

| 001215 |   |      |        |                  |         |           |            |        |         | WHILE N:=N-1 <> 0 DD             |

|        |   |      | ESP031 |                  |         |           |            |        |         | BEGIN                            |

| 001217 |   |      |        | XJR              |         | ×5        |            | RZ     |         | LRC XOR ADDR.ESG=>_RC            |

| 001218 | 1 | 002F |        | ADDC             | 1       |           |            | RS     |         | ADDR+1=>ADDR                     |

| 001219 | 1 | 0030 |        | 538              |         |           | ESP03      |        |         | END                              |

| 001220 | 1 | 0031 |        | NOV              |         |           | CLRC       |        |         | LRC=>CLRC                        |

| 155100 | 1 | 2000 |        | INE              |         | R1        |            | R 2    |         | IF CLRC<>PLRC                    |

| 255100 | 1 | 0033 |        | JHP              |         |           | ESP10      | 0      | ;E      | THEN GOTU ESS_RECOVER            |

|        | 1 | 0034 | ;      |                  |         |           |            |        |         |                                  |

| 655100 | 1 | 3034 | ;      |                  |         |           |            |        |         |                                  |

| 455100 | 1 | 0034 | ; ESG  | PREP !           | START.  | PRO       | CESSIN     | G (ESC | G STA   | TE 1)                            |

| 655100 | 1 | 2034 | ;      |                  |         |           |            |        |         |                                  |

|        | 1 | 0034 | ;      |                  |         |           |            |        |         |                                  |

|        |   |      | ESP040 |                  |         |           |            |        |         | G PREPARATION:                   |

| 001227 | 1 | 0034 |        | LOM              |         |           |            |        |         | 2#111=>PSH(15:13), DISABLE INT   |

| 855100 | 1 | 0035 |        | ABAC             | DAESCI  | 2<9       |            | 82     |         | ESCCP_DEVICE_ADDR=>DA            |

| 001229 | 1 | 0036 |        | SIO              |         | 20        |            |        |         | READID(DA, STATUS)               |

| 001230 | 1 | 0037 |        | IBN              |         | RO        | BESCO      |        | T;      | IF ESCCP_START                   |

| 001231 | 1 | 0038 |        | JMP              |         |           |            | 0      |         | THEN GOTO ESG_START              |

| 555100 | 1 | 0039 |        | IBZ              |         | RO        | BESCO      |        | ;       | IF ESCCP_PREP                    |

| 001233 | 1 | 003A |        | JMP              |         |           |            | 0      |         | THEN GOTO INT_RESERVATION        |

| 001234 | 1 | 0038 |        | NOVC             | MESCO   | PPREP     |            | 20     |         |                                  |

| 001235 | 1 | 0030 |        | CIO              |         | RO        |            | 82     | ;       | HRITEID. (DA, PREP=1)            |

| 001236 | 1 | 0030 |        | HOV              |         |           |            | R5     |         | LET_ADDR=>LET                    |

| 001237 |   |      |        | SDZ              | -       | SYSES     | R+LTHS     | 1.x5   | ;       | IF LTMS1.LET <> 0                |

| 001238 | 1 | 0040 |        | JMP              |         |           | ESP01      | 0      |         | THEN GOTO INT_RESERVATION        |

| 001239 | 1 | 2041 |        |                  |         |           |            |        | ;       | ELSE                             |

| 001240 | 1 | 2041 |        |                  |         |           |            |        | ;       | BEGIN                            |

| 001241 | 1 | 0041 |        | INC              | -       | SYSES     | R+LTHS     | 1.X5   | ;       | INCREMENT MESSAGELET             |

| 001242 |   |      |        | HOVC             | 30000   | /10       |            | 20     |         |                                  |

| 001243 |   |      |        | MOV              | 80 -    | SYSES     | R+LTHS     | 4. 15  |         | 3D SECONDS=>MESSAGE4.LET         |

| 001244 |   |      |        | MON              |         |           |            |        | ÷ .     | SEND_LETTER (TO RTC)             |

| 001245 |   |      |        | JMP              |         | 54        | ESPE5      | 0      | ;E      | LETTER ERROR, GOTO ERRORS        |

| 001246 |   |      |        | JMP              |         | 100       | ESPOL      |        | 1       | GOTO INT_RESERVATION             |

| 001247 |   |      |        | 200              |         |           | 1000000000 |        |         | END                              |

|        |   | 204A |        |                  |         |           |            |        |         |                                  |

| 001248 |   |      |        |                  |         |           |            |        |         |                                  |

|        |   |      |        | ISTART.          | PROCE   | 24122     | (ESG       | STATE  | 01      |                                  |

|        |   |      |        |                  | 0 -> 2  |           |            |        | 1512    |                                  |

| 001251 |   |      |        |                  |         |           |            | 10     |         |                                  |

| 001231 |   | 0044 |        | Lettre-setter at |         | 7000 8000 |            |        |         |                                  |

### Software

AU0 AU0 AU0

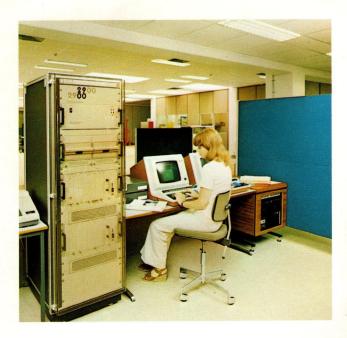

Like the CR80 hardware, the CR80 software follows a completely modular concept. This policy enables the user to select a number of existing modules, create a few special purpose modules and integrate them all into a customized system, which is easy to implement, to test, and to maintain.

The System Software package used on the CR80 computer is the CR80 SYSTEM ONE.

CR80 SYSTEM ONE supports interrupt handling, multiprocessing in up to 8 CPU's and time shared multiprogramming in each single CPU. Process communication is available either as message handshake communication or as an extremely fast data buffer exchange facility.

The CR80 SYSTEM ONE FILE MANAGEMENT SY-STEM enables manipulation of disk files, virtual cardreaders and line printers. The File Management System supports random (direct) access and sequential access. The access method as well as the record-size is a file-open parameter.

Software development on the CR80 is fully supported by the CR80 SYSTEM ONE UTILITY PACKAGE which includes such standard facilities as editor, assembler, binder and patch programmes. Furthermore, the package includes a PASCAL compiler providing the facility of programming the CR80 in one of the most advanced high-level languages of the future.

The CR80 SYSTEM ONE DRIVER PACKAGE supports the standard peripherals plus a wide range of special units interfacing the CR80. Especially in the area of handling communication lines, CHRISTIAN ROVSING A/S has developed an extensive set of System Modules.

To support the highly reliable hardware modules, CHRISTIAN ROVSING A/S has designed an advanced system of on-line and off-line Diagnostic Software giving fast error detection and thereby further improved system availability.

## Systems

The flexible architecture of the CR80 mini, together with fast interrupt handling capabilities and the comprehensive instruction set, enables the CR80 mini to cover a wide range of applications in the field of fast data processing and data manipulation, process control, intelligent terminal applications, administration systems etc. Furthermore, the CR80 mini covers the area of more specialised systems when used as a front-end processor, concentrator or array processor.

Due to the modularity of the CR80 mini, simple low cost processors can be configured for less demanding applications, and high throughput rate and processing power requirements can be met by means of its multiprocessing facilities.

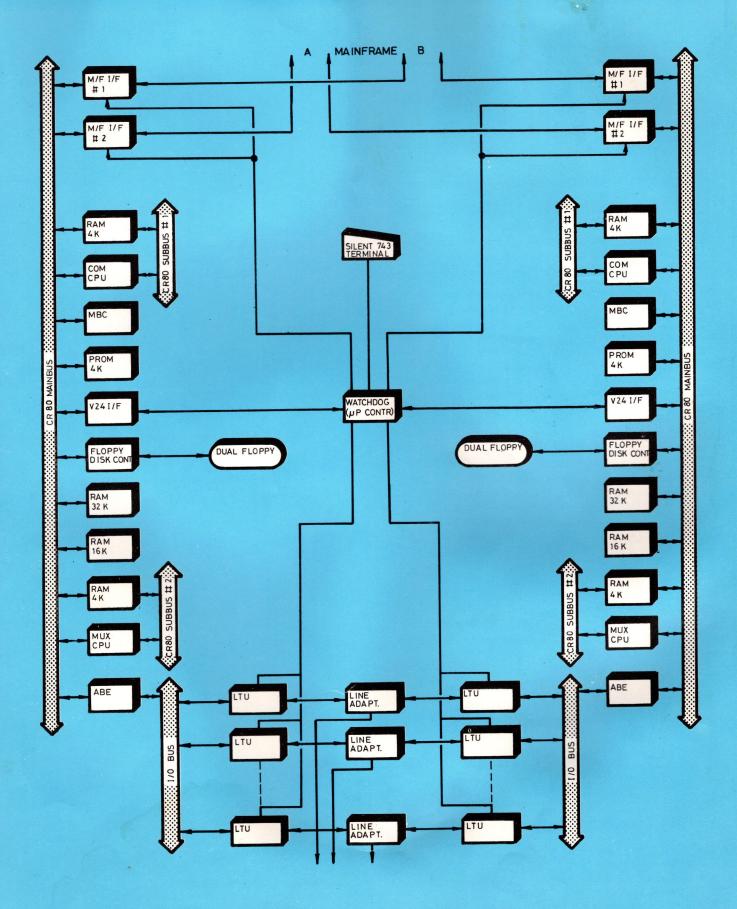

For applications requiring high reliability, such as node processors in data communication networks, the CR80 mini can be dualized using the Watchdog module to control the switch over from the failed branch to the hot standby. This is based on on-line diagnostic programmes running in both halves with the status regularly transmitted to the Watchdog module. The lines carrying the information between the nodes, interface through Line Termination Units connected to the CR80 mini via I/O or TDX bus's.

Utilizing the TDX bus all line multiplexing is done by interleaving of packets on the bus without loading of the CR80 minicomputer.

Since its introduction in 1975, the CR80 mini has been implemented successfully in many systems. The CR80 mini has proven itself in over 50 different applications:

- Node Processor in data communication networks.

- Message Editing and Distribution Processor for terminal clusters.

- Array Processor handling satellite data in real time.

- Data Network Control Centre Computer incl. 300 Mb. disks.

- Fast Formatter/Control Processor for High Density Digital Tape Stations.

- Color Image Manipulation System.

- Laser Plotter Controller.

- Front-End Computer for Mainframes (IBM & others).

- Traffic Analysis Systems.

- Process Control Systems.

- Data Communication Concentrator and Message Switcher.

- Telemetry Systems.

- Automation of TV-studios.

#### CR80 minicomputer features.

THE CR80 IS AN EXTREMELY FAST MULTIPROCESSING AND MULTIPROGRAMMABLE MINICOMPUTER BASED ON SCHOTTKY-LSI TECHNOLOGY.

- 16 bit words, 2's complement processing.

- Bidirectional Main Bus and local Sub Busses, max. transfer speed: 4M words/sec.

- Addressing range: Main Bus 256K words or 512K bytes

Sub Bus 256K words or 512K bytes

- 274 instructions, fixed length 16 bits, extendable by MODIFY to double length.

- Execution: 0.5 to 1 million instructions per second with standard memory (in multiprocessing mode up to 5.0 Mips).

- CPU clock rate: 8MHz.

- 12 addressing modes: Immediate, base relative, program relative, location relative, register, and indexed. Word (16 bits, 2's complement) and byte (8 bits) addressing.

- 6 types of vectorized prioritized interrupts, 3 maskable, 64 vectors and 4 priority levels.

- 14 internal registers: 8 accumulators, BASE pointer, MODIFY register, PROGRAM pointer, PROGRAM counter, TIMER register, and PROGRAM STATUS register.

- Automatic loading and saving of all CPU registers with programs during multiprogram execution.

- User accessible CPU microcode RAM, dynamically alterable user extensions of instruction set during execution.

- Special instructions make CPU microcode available on local Sub Busses for direct fast execution by function module (up to 8 FUNC modules per Sub Bus), e.g. fast fourier transform, floating point etc.

- Max. 8 CPU's in a CR80 System, safe hardware based multiprocessing.

- Max. 63 I/O devices (DMA & FUNC devices excepted).

- Direct Memory Addressing (DMA) devices to 2.6 Mw/sec. with standard memory.

- Wide range of peripheral and communications interfaces, incorporating LSI's and bipolar microprocessors for further distribution of computing power.

- Hardware and firmware have taken over many functions previously done by system software.

## **CR80**minicomputer

### STANDARD MODULES

| CR 8000/2<br>CR 8001/2<br>CR 8001/1<br>CR 8002<br>CR 8003<br>CR 8004<br>CR 8005<br>CR 8006<br>CR 8010<br>CR 8011<br>CR 8012<br>CR 8013<br>CR 8014<br>CR 8022<br>CR 8030<br>CR 8031<br>CR 8032<br>CR 8033<br>CR 8034<br>CR 8035<br>CR 8036<br>CR 8037<br>CR 8038<br>CR 8039<br>CR 8039<br>CR 8040<br>CR 8041 | CPU                                                            |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--|

| CR 8041<br>CR 8042                                                                                                                                                                                                                                                                                          | External Asynchronous LTU<br>Synchronous Line Termination Unit |  |

|                                                                                                                                                                                                                                                                                                             |                                                                |  |

| CR 8044<br>CR 8045<br>CR 8045<br>CR 8046<br>CR 8047<br>CR 8049<br>CR 8050<br>CR 8050<br>CR 8051<br>CR 8052<br>CR 8053<br>CR 8054<br>CR 8055<br>CR 8055<br>CR 8056<br>CR 8059<br>CR 8060<br>CR 8061<br>CR 8064<br>CR 8065<br>CR 8065<br>CR 8070<br>CR 8071<br>CR 8072<br>CR 8081/1 | Internal Line Termination Unit<br>Disk Storage System<br>VDU<br>CR 80 DMA<br>BIT SYNCHRONIZER<br>Frame Synchronizer<br>Hamming Calculator<br>Diskette Drive 140<br>Diskette Formatter 1140<br>Floppy Disk Controller<br>Vizir I/F<br>Varian V77 I/F<br>HDTR Controller<br>TLM I/F<br>IBM I/F<br>ICL 2900 I/F<br>HP I/F<br>Card Reader CB 105-B<br>Line Printer 8396<br>Watchdog<br>Async. LTU (internal 300 baud generator)<br>CPU Simulator<br>Tape I/F<br>Crypto I/F<br>Disc I/F<br>Active Bus Ext. (Transmitter)<br>Active Bus Ext. (Receiver)<br>Memory Mapping Bus Ext.<br>Serial I/O<br>TDX I/F<br>Analog I/F<br>LTU, for TDX I/F<br>SCM |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CR 80101                                                                                                                                                                                                                                                                          | CPU (Mainbus)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| CR 80102                                                                                                                                                                                                                                                                          | CPU (Subbus)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 01100102                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

### **TDX Modules:**

| CR 1070<br>CR 1071<br>CR 1072 | TDX CDMA<br>TDX RD<br>TDX CDSP |

|-------------------------------|--------------------------------|

| CR 1060                       | LTUX, 9.6kb                    |

| CR 1061                       | LTUX, X21                      |

| CR 1062                       | LTUX, Sync.                    |

| CR 1063                       | LTUX, Async. A                 |

| CR 1064                       | LTUX, 9.6kb Internal           |

| CR 1065                       | LTUX, 32kb                     |

| CR 1066                       | LTUX, Async. B                 |

| CR 1067                       | LTUX, Async. B Special         |

| CR 1068                       | LTUX, NBS Crypto               |

| CR 1090                       | LTUX, MM master module         |

| CR 1091                       | LTUX, GIO General I/O          |

| CR 1092                       | LTUX, PIO Parallel I/O         |

| CR 1093                       | LTUX, ADC AD-conv.             |

| CR 1094                       | LTUX, DAC DA-conv.             |

| CR 1095                       | LTUX, MBI Main Bus I/F         |

| CR 1096                       | LTUX, IOPU I/O Protection unit |

### X-Net modules:

| CR 2510 | Terminal wall outlet   |

|---------|------------------------|

| CR 2520 | Amplifier and splitter |

| CR 2530 | Terminal               |

| CR 2540 | X-net Controller       |

| CR 2541 | X-net output driver    |

| CR 2550 | Terminal adapter       |

| CR 2551 | ID-Card reader         |

| CR 2552 | V24 Terminal interface |

| CR 2553 | Modem interface        |

Redundant front-end processor configuration. Up to 80K character throughput between communication lines and main frame.

CHRISTIAN ROVSING A/S 2 Lautrupvang DK-2750 Ballerup Denmark

Phone: 02-65 11 44 Telex: 3 51 11 cr dk

#### CHRISTIAN ROVSING INC. 828 Capitan Street Thousand Oaks California 91360 U.S.A. Phone: 805-498-2135 Telex: 910-33 65 733

Design: Ingelise Bengtson . Printed in Denmark . Rosenborg Tryk