DANSK DATA ELEKTRONIK <u>ID-7037D 48K DYNAMIC RAM MODULE</u> for the SPC-1 MICROPROCESSOR SYSTEM APRIL 1981

Author: Knud Arne Nielsen

۰.

Aalberg, Gulas is to admit r Institutfer Color Laters and

្នុនខណ្ឌ**ាព**

4712

de

Las els solution 13 Science victoria 13 8000 Alborg

#### 1. INTRODUCTION.

The ID-7037D Dynamic RAM Module contains 48K bytes of dynamic memory. The memory module is desigend to be used in single or multi user MIKADOS systems but the module can be used in in other memory configurations as well.

The module can be strapped to use two different implementations of bank switching. The ID-7037D is designed to be controlled by the ID-8538 Refresh Module.

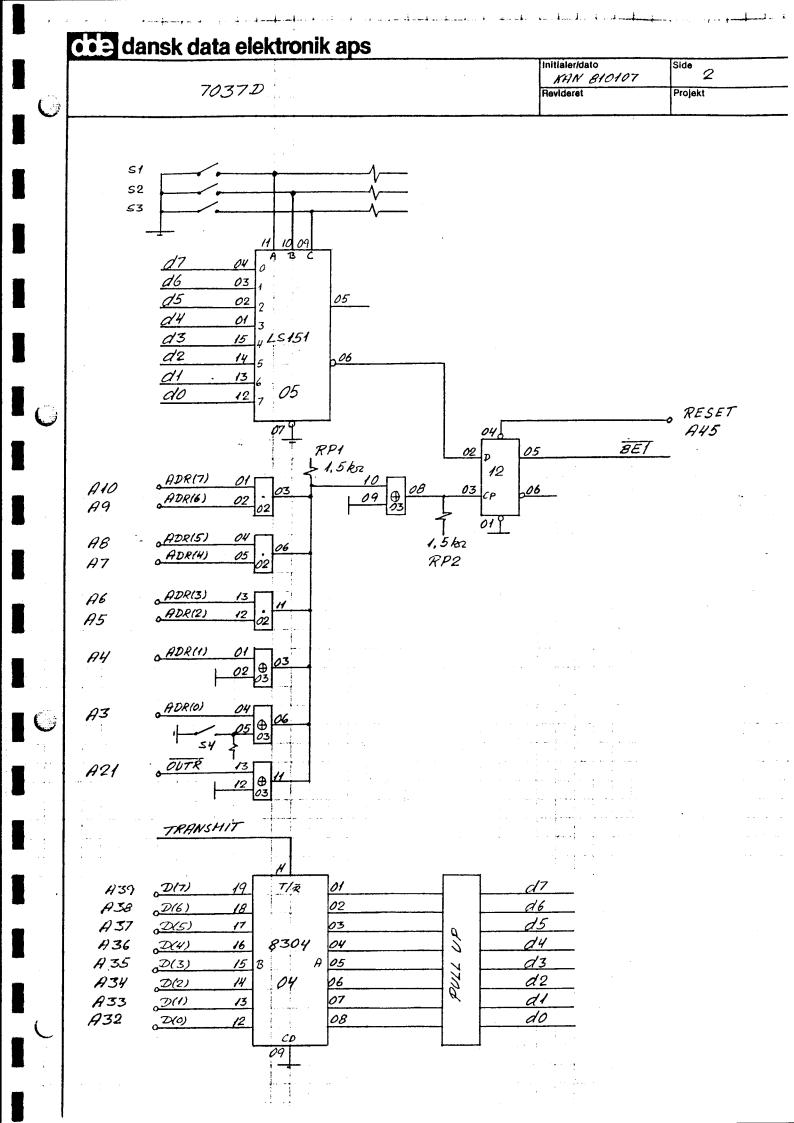

#### 2. BANK SWITCHING.

order to expand the addressing capability of 8085A the memory In module is equipped with bank switching. In a bank switched memory system a bank can be enabled or disabled. When a bank is enabled occupies space in the address space of the computer and can be it accessed by the CPU and various DMA units. When a bank is disabled does not occupy space in the address space and it cannot be it The module can be strapped to use one of two different accessed. of bank switching which are described in the implementations following text.

#### 2.1. BANK SWITCHING IMPLEMENTATION 1.

When the strap between pos. 9 and pos. 10 is placed in the upper position bank switching implementation 1 is used.

A memory bank is identified by a bank control address which is FC or FD and a bit number between 0 and 7. In this way it is possible to differentiate between 16 memory banks. A memory bank with control addres AA and bit number n is enabled when the CPU executes an OUT AA instruction and the bit number n in the data word is a one. The bank is disabled if bit number N is zero.

The control address and the bit number is called the bank address and should not be confused with the memory starting address.

## 2.2. BANK SWITCHING IMPLEMENTATION 2.

When the strap between pos. 9 and pos. 10 is placed in the lower position bank switching implementation 2 is used.

The address bus is expanded with four extra address lines from ADR(15:0) to to ADR(19:0). A memory bank is enabled when ADR(19:16) matches the bank address of the memory bank.

The extra address lines ADR(19:16) are driven by the ID-8537 Memory Register Module. This module contains one four bit register for the CPU and one four bit register for each of the seven possible DMA channels. When the CPU accesses memory the register corresponding to the CPU drives ADR(19:16). When one of the DMA channels accesses memory its corresponding register drives the extra address lines. In this way the CPU can execute a program in one memory bank while the DMA channels are transferring data to or from other memory banks. The Memory Register Module is loaded by the CPU. See the manual for this module.

#### 3. The SWITCH REGISTER.

-

In order to use the module in different memory configurations the module is equipped with a seven bits switch register S(7:1). The most significant bit of the switch register S(7) is closest to the edge connector of the module. A bit in the switch register is a logic one when the switch is on that is when the switch is closed.

The switch register is divided into an upper four bit part S(4:1) which determines the bank address of the module and a lower three bit part S(7:5) which determines the function af the module.

2

If a memory module has an eight bit switch installed instead of the usual seven bit switch S(8) is not used.

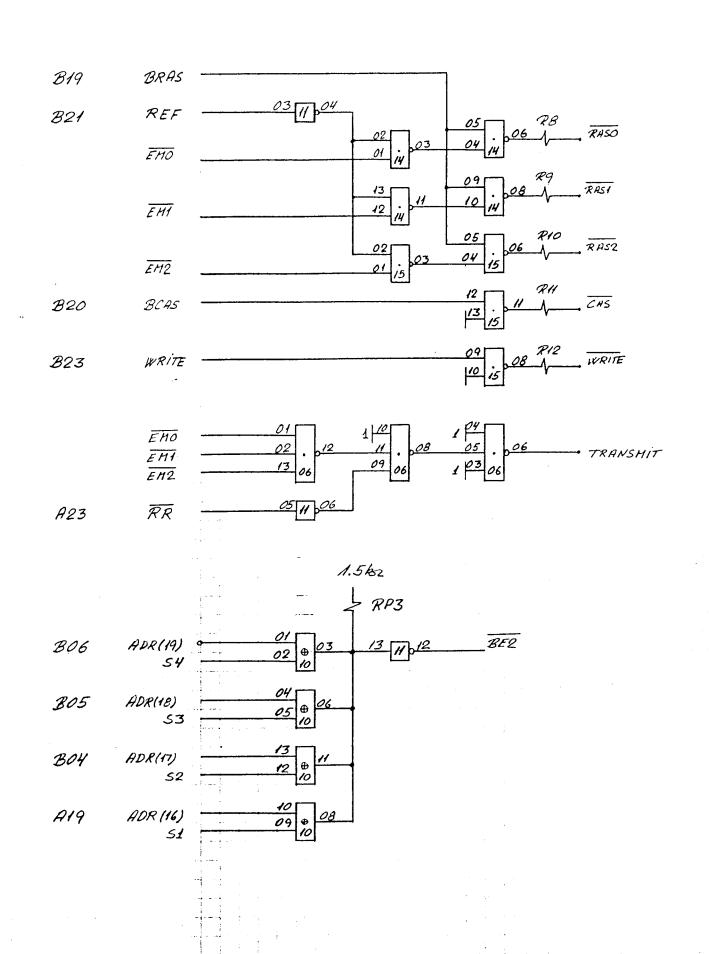

#### 3.1. THE BANK ADDRESS.

When bank switching implementation 1 is used S(4) determines wheather the bank control address is FC or FD. When S(4) is off the bank control address is FC and when S(4) is on the bank control address is FD. S(3:1) selects the bit number in the data word. When S(3:1) is off bit zero is selected. When S(3:1) is on bit seven is selected.

When bank switching implementation 2 is used S(4:1) is compared to address ADR(19:16). If there is a match the bank is enabled.

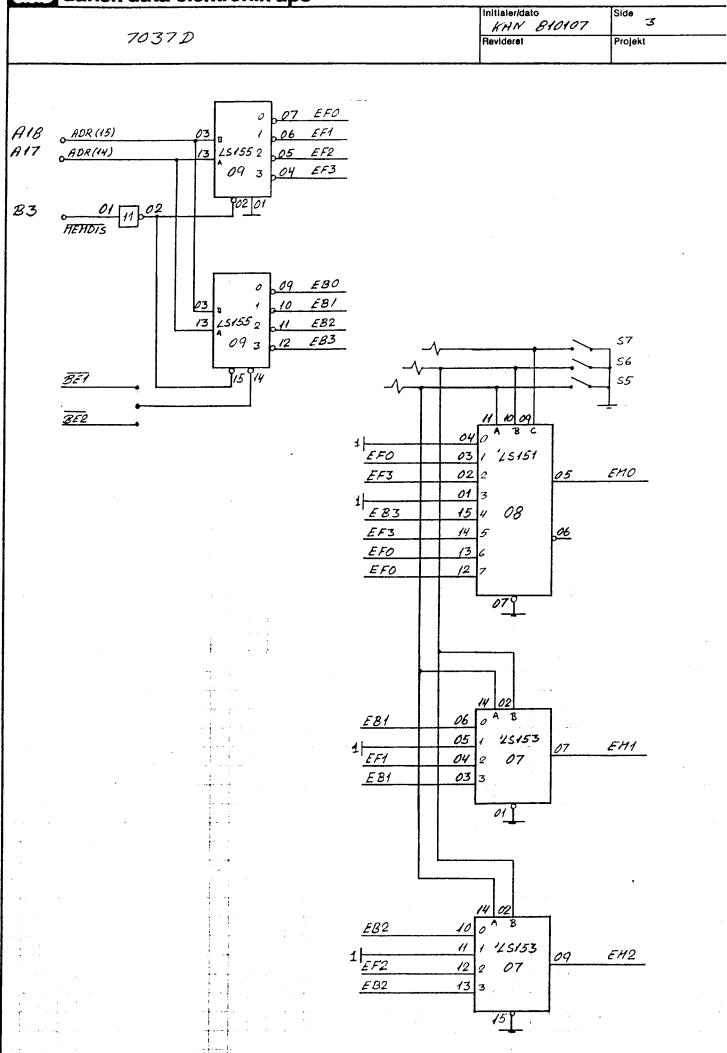

#### 3.2. THE FUNCTION.

-

S(7:5) determines how the module is configured. The different functions are listed in the table below. The functions can be divided into three different groups. These are:

| System memory with MIKADOS bank; | FCT = | 0. |    |    |    |

|----------------------------------|-------|----|----|----|----|

| Bank switched memory;            | FCT=  | 3, | 4, | 7. |    |

| Non bank switched memory;        | FCT=  | 1, | 2, | 5, | 6. |

By choosing the proper function it is possible to place a debugger program in a non bank switced memory with starting address COOO.

A multi user MIKADOS system uses one module with FCT=0 for the MIKADOS operating system and one module with FCT=3 for each user in the system. When a debugger is placed in this system the function of the user modules is changed from FCT=3 to FCT=4.

I

NOTICE: All bank switched memory is disabled after POWER UP RESET when bank switching inplementation 1 is used.

When bank switching implementation 2 is used the content of the registers on ID-8537 is unknown after POWER UP.

dde

| FUNCTION | MO |     | Ml | I   | <b>M</b> 2 |     |

|----------|----|-----|----|-----|------------|-----|

| 0:       |    | FO  |    | B1  |            | B2  |

| 1:       |    | FO  |    | F1  |            | F2  |

| 2:       |    | F3  |    | OUT |            | OUT |

| 3:       |    | Β3  |    | B1  |            | B2  |

| 4:       |    | OUI | 1  | B1  |            | B2  |

| 5:       |    | F3  |    | F1  |            | F2  |

| 6:       |    | FO  |    | OUT |            | OUT |

| 7:       |    | OUI | 1  | B1  |            | B2  |

#### EXPLANATION:

I

F0: Non bank switched memory. Starting address 0000.

F1: Non bank switched memory. Starting address 4000.

F2: Non bank switched memory. Starting address 8000.

F3: Non bank switched memory. Starting address C000.

B0: Bank switched memory. Starting address 0000.

B1: Bank switched memory. Starting address 4000.

B2: Bank switched memory. Starting address 8000.

B3: Bank switched memory. Starting address C000.

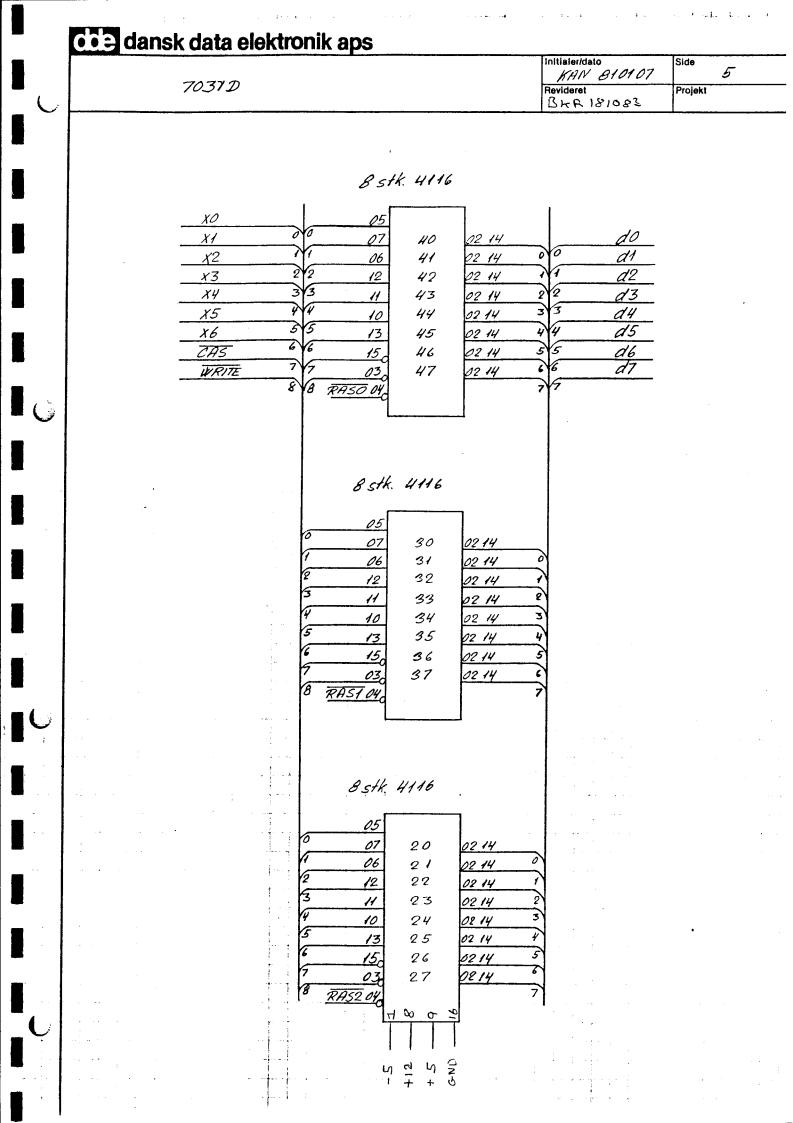

MO: 16K dynamic memory placed in the upper row on the module. M1: 16K dynamic memory placed in the middle row on the module. M2: 16K dynamic memory placed in the lower row on the module.

OUT: Disabled 16K memory bank.

# dansk data elektronik aps

ل

L

C

|       | Initialer/dato<br>KHN' 810107 | Side    |

|-------|-------------------------------|---------|

| 7037D | Revideret                     | Projekt |

| H3  | ADRIO)                                 | 09 |      |    |           |

|-----|----------------------------------------|----|------|----|-----------|

| A4  | ADR(1)                                 | 05 |      |    |           |

| A5  | ADR(2)                                 | 07 |      |    |           |

| A6  | ADRIS                                  | 21 |      |    |           |

| AT  | ADR(4)                                 | 23 |      |    |           |

| AB  | ADR(5)                                 | 25 |      |    |           |

| AN  | ADR(6)                                 | 27 |      | H  | AA RH XO  |

| AI0 | ADRA                                   | 10 |      | 13 | M R2 X1   |

| All | ADR(B)                                 | 06 |      | 12 | 1 R3 X2   |

| AI2 | HURAI                                  | 08 | 3242 | 18 | M_ R6_ X3 |

| A13 | AUR(10)                                | 20 |      | 17 | M. #5 X4  |

| A14 | AUR(H)                                 | 22 |      | 16 | NR1 X5    |

| A15 | HDR(12)                                | 24 |      | 19 | M R7 X6   |

| A16 | HOR(13)                                | 26 |      |    |           |

|     |                                        |    | 01   |    |           |

| 821 | REF                                    | 01 |      |    |           |

|     | •                                      | 02 |      |    |           |

|     | 4<br>4<br>4                            |    |      |    |           |

| B22 | ROWEN                                  | 03 |      |    |           |

| •   | •••••••••••••••••••••••••••••••••••••• |    |      |    |           |

# doe dansk data elektronik aps

# dansk data elektronik aps

|       | Initialer/dato<br>KAN 810313 | Side<br>4 |

|-------|------------------------------|-----------|

| 7037D | Revideret                    | Projekt   |

D\$9806/10-79