# dde

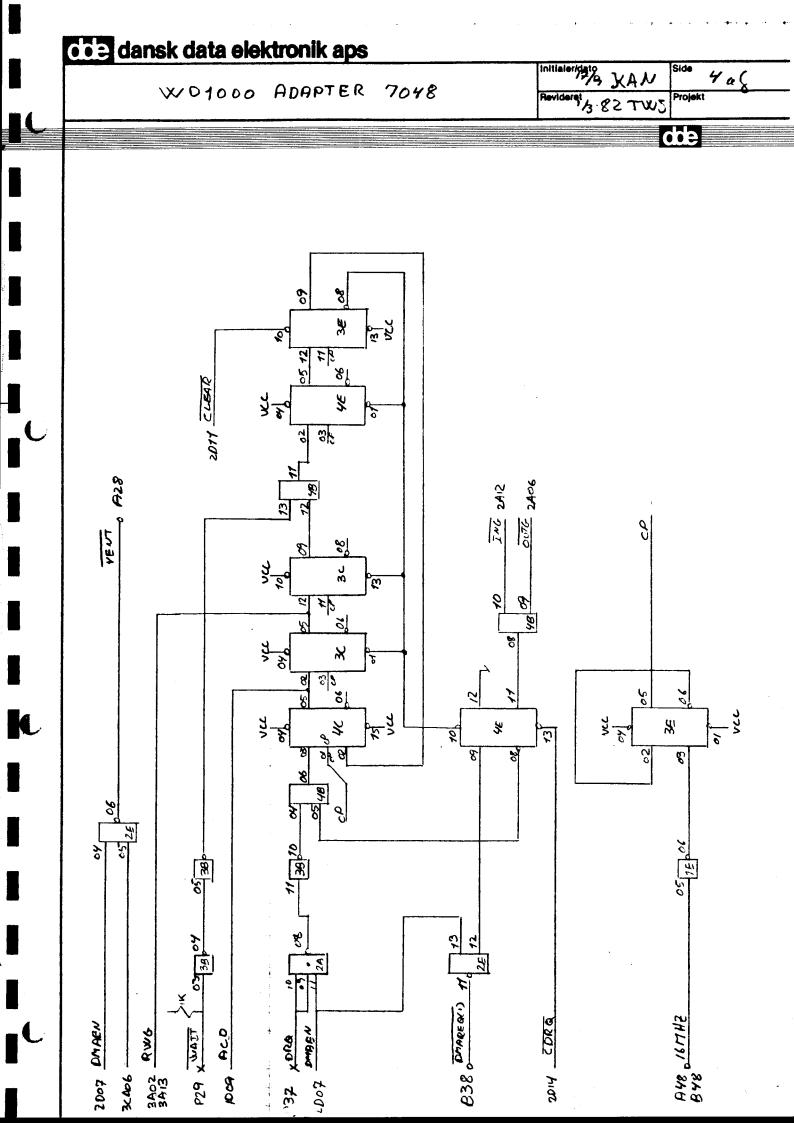

7048 ADAPTER

Dansk Data Elektronik Aps 10 august 1982

Auther: Thue Winther-Jørgensen

Copyright 1982 Dansk Data Elektronik Aps

#### PREFACE

The 7048 adapter has the purpose of interfacing the WD1000 controller to the SPC/1. The adapter can be used in a programmed mode or with the use off DNA. Other units may use the same DMA channel as the 7048, but they must not be enabled concurrently.

Basis adress is 0 to OF hex. DMA channel number 1. Interrupt level 5.

IN 00-07: Is input directly from the WD1000 controller, the meaning of the specific adresses can be seen in appendix 1.

IN 08-0F:

|   | D7 |   | D6 |   | D5 |   | D4 |   | D5 |   | D2   |   | D1     | DO   |   |

|---|----|---|----|---|----|---|----|---|----|---|------|---|--------|------|---|

| ! | Х  | ! | X  | ! | Х  | ! | Х  | ! | Х  | ! | WAIT | ! | DMAEN! | INT. | ! |

D2: Is WAIT active on the interface?D1: Is DMA enabled on the adapter?D0: Is an interrupt pending?

OUT 00-07: Is output directly to the WD1000 controller. OUT 08-0F:

|   | D'/ |   | <b>D</b> 6 |   | D5 |   | D4 |   | D3   |   | D2     | D1     | DO  |   |

|---|-----|---|------------|---|----|---|----|---|------|---|--------|--------|-----|---|

| ! | 0   | ! | 0          | ! | 0  | ! | 0  | ! | CDRQ | ! | CLEAR! | DMAEN! | W/R | ! |

D3: Sets Dmareq to one (is used in connection with writing).D2: Initialize the DMA control on the adapter.D1: Enables the DMA and interrupt logic on the adapter.D0: Sets the DMA logic too write or read.

2

dde

# WD1000 WINCHESTER DISK CONTROLLER OEM MANUAL

# PRELIMINARY

# WESTERN DIGITAL

2445 MCCABE WAY IRVINE, CALIFORNIA 92714 (714) 557-3550 TWX 910-595-1139

SPEC No. 80-031001

dde

|           | USER COMMENTS         |                                                                                                            |

|-----------|-----------------------|------------------------------------------------------------------------------------------------------------|

| FROM: NAM |                       |                                                                                                            |

| ADDF      | IE SS                 | NOTE: Use this form to communicate any err<br>suggested changes, or general commen<br>about this document. |

| CITY      |                       |                                                                                                            |

| STAT      | ZIP                   |                                                                                                            |

| DOCUMENT: | TITLE/NUMBER/REVISION |                                                                                                            |

| COMMENTS: |                       |                                                                                                            |

|           |                       |                                                                                                            |

|           |                       |                                                                                                            |

|           |                       |                                                                                                            |

|           |                       |                                                                                                            |

|           |                       |                                                                                                            |

|           |                       |                                                                                                            |

|           |                       |                                                                                                            |

|           |                       |                                                                                                            |

|           |                       |                                                                                                            |

|           |                       |                                                                                                            |

|           |                       |                                                                                                            |

|           |                       |                                                                                                            |

|           |                       |                                                                                                            |

|           |                       |                                                                                                            |

|           |                       |                                                                                                            |

FOLD, STAPLE & MAIL

SIAPLE

dde

. . .

## WD1000 Hard Disk Controller

#### \*\*\* Table of Contents \*\*\*

|                |                  | Table of Contents                     |                             | de                                     |

|----------------|------------------|---------------------------------------|-----------------------------|----------------------------------------|

|                |                  |                                       |                             |                                        |

|                |                  |                                       |                             |                                        |

| Section 1      | INTRODUCT        | ION                                   |                             |                                        |

|                | 1.1 Gener        | al Description                        |                             |                                        |

|                |                  |                                       | •••••                       | ••••• 1-1                              |

|                |                  | ares                                  | • • • • • • • • • • • • •   | ••••• 1-2                              |

|                | 1.5 Spec:        | fications                             |                             | 1-3                                    |

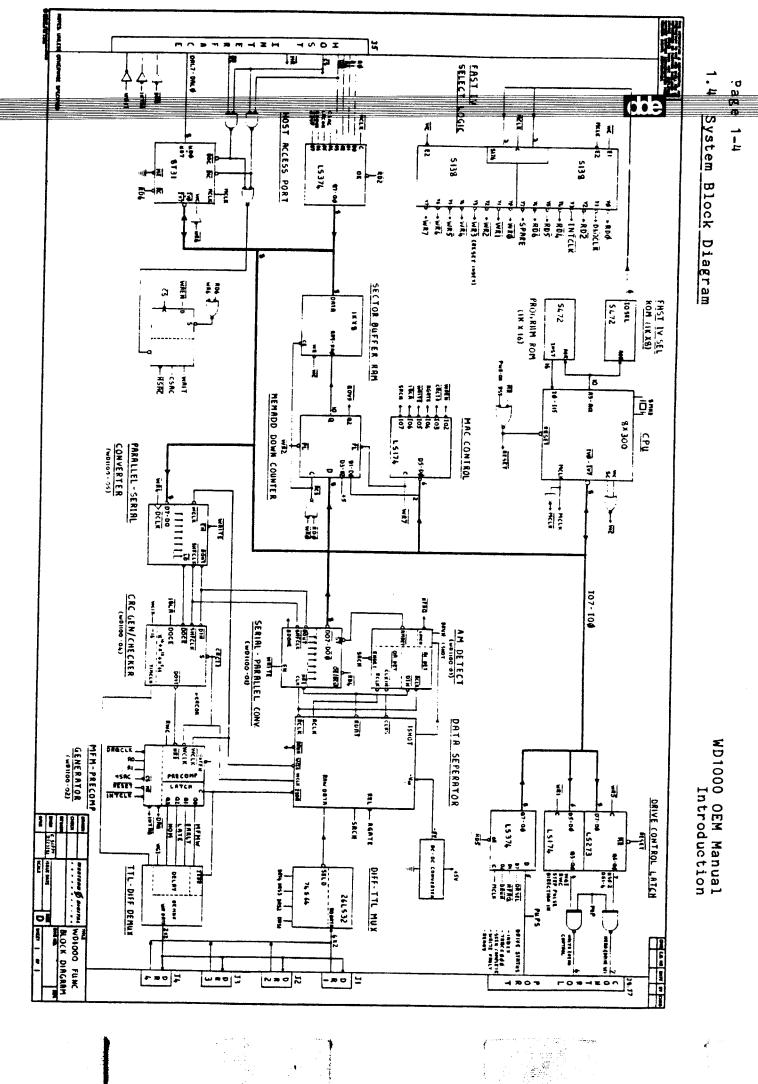

|                | 1.4 Syste        | em Block Diagram                      |                             | 1-4                                    |

| -              |                  |                                       |                             |                                        |

| Section 2      | INTERFACE        | CONNECTORS                            |                             |                                        |

|                | 2.1 Organ        | ization                               |                             | -                                      |

|                | 2.2 Host         | ization                               | • • • • • • • • • • • • •   | ••••• 2-1                              |

|                |                  | Interface Connector                   | • • • • • • • • • • • • • • | ···· 2-2                               |

|                | 2.2.1            |                                       |                             |                                        |

|                | 2.2.2            | CS                                    | • • • • • • • • • • • • • • | 2_2                                    |

|                | 2.2.3            | WE                                    |                             | ······································ |

|                | 2.2.4            | RE-                                   |                             | •••••                                  |

|                | 2.2.5            |                                       | • • • • • • • • • • • • •   | •••••••••• 2=2                         |

|                | 2.2.6            |                                       | • • • • • • • • • • • • •   | ••••• 2 <del>-</del> 2                 |

|                |                  | WAIT-                                 |                             |                                        |

|                | 2.2.7            | INTRQ                                 |                             | 2_2                                    |

|                | 2.2.8            |                                       |                             | 2_2                                    |

|                | 2.2.9            | MR                                    |                             |                                        |

|                | 2.2.1            | 0 -V                                  |                             | ······· 2-3                            |

|                | 2.2.1            |                                       | •••••                       | ••••• 2-3                              |

|                | 2.2.1            |                                       | • • • • • • • • • • • • • • | ••••••••••• 2-3                        |

|                |                  |                                       | • • • • • • • • • • • • •   | 2-3                                    |

|                | 2.2.1            |                                       | `ace Connector              |                                        |

|                | 2.3 Drive        | control Connectors .                  | • • • • • • • • • • • • •   | 2-5                                    |

|                | 2.3.1            | KWC                                   | • • • • • • • • •           | 2 5                                    |

|                | 2.3.2            | Write Gate                            |                             | ······································ |

|                | 2.3.3            | Seek Complete                         | •••••                       | ••••••••• 2=5                          |

|                | 2.3.4            | Track 000-                            | • • • • • • • • • • • • • • |                                        |

|                | 2.3.5            | Track 000-                            | •••••                       | ••••• 2-5                              |

|                | 2.3.6            | Write Fault                           | • • • • • • • • • • • • •   | ••••• 2 <del>-</del> 5                 |

|                |                  | HSO-HS2-                              | • • • • • • • • • • • • • • |                                        |

|                | 2.3.7            | index                                 | ••••••                      | 2-6                                    |

|                | 2.3.8            | Ready-                                |                             | 2-6                                    |

|                | 2.3.9            | Step-                                 |                             | 2.6                                    |

|                | 2.3.10           | DS1-DS4-                              |                             |                                        |

|                | 2.3.11           | Control Driver/Rec                    | •••••                       | ••••••••• 2-0                          |

|                | 2 3 12           | 50 Pin Drive Canta                    | erver                       | •••••••• 2-6                           |

|                | 2 2 12           | 50 Pin Drive Contro                   | of Connector                | ••••• 2-7                              |

|                | 2.4 Drive        | 34 Pin Drive Contro                   | ol Connector                | ••••• 2-8                              |

|                | CII DITTE        | Dava connector                        |                             | 2 0                                    |

|                | <b>2 • 4 • 1</b> | Differental Data Dr                   | iver/Receiver               | 2 0                                    |

|                | 2.5 Power        | Connector                             |                             | 2-10                                   |

| <b>.</b>       |                  |                                       |                             |                                        |

| Section 3      | INTERFACE T      | IMING                                 |                             |                                        |

|                | 3.1 Host I       | nterfood Timina                       |                             |                                        |

|                | 2 1 1            | nterface Timing                       | • • • • • • • • • • • • • • | •••••••• 3-1                           |

|                |                  | nust read liming                      |                             | ~ ~ ~                                  |

|                | 2+1+6            | nost write liming                     |                             | 2 2                                    |

|                |                  |                                       |                             |                                        |

|                | 3.3 Drive        | data timing                           |                             | 3_4                                    |

| <b>~</b> • • • |                  |                                       |                             |                                        |

| Section 4      | HOST INTERF      | ACING                                 |                             |                                        |

|                | 4.1 Waits        | · · · · · · · · · · · · · · · · · · · |                             |                                        |

|                | 4.1.1            | WATT timing                           | • • • • • • • • • • • • •   | •••••••• 4=1                           |

|                | 4.2 Host in      | WAIT timing                           | • • • • • • • • • • • • •   | ••••• 4-2                              |

|                | 1030 11          | iterfacing example                    | • • • • • • • • • • • • •   | 4-2                                    |

|                |                  |                                       |                             | -                                      |

|                |                  |                                       |                             |                                        |

ŧ

, · ··

. .

## WD1000 OEM Manual Table of Contents

.

1

|           |      | de                     |               |

|-----------|------|------------------------|---------------|

| Section 5 | TASK | FILE                   |               |

|           | 5.1  | Task File Basics       | 5-1           |

|           | 5.2  | Register Array         |               |

|           | 5.3  | Register Definitions   | 5-2           |

|           |      | 5.3.1 Command Register | 5-2           |

|           |      | 5.3.2 Status Register  | 5-2           |

|           |      | 5.3.3 SDH Register     | 5-3           |

|           |      | 5.3.4 Cylinder Number  | 5-4           |

|           |      | 5.3.5 Sector number    |               |

|           |      | 5.3.6 Sector Count     |               |

|           |      | 5.3.7 Error Register   |               |

|           |      | 5.3.8 Write Precomp    |               |

|           |      | 5.3.9 Data Register    |               |

|           | 5.4  | Status Registers       | 5-6           |

|           | 5.5  | Status Register Bits   | 5-6           |

|           |      | 5.5.1 Error            | 5-6           |

|           |      | 5.5.2 Data Request     |               |

|           |      | 5.5.3 Seek Complete    | 5-6           |

|           |      | 5.5.4 Write Fault      |               |

|           |      | 5.5.5 Ready            | 5-7           |

|           |      | 5.5.6 Busy             | 5-7           |

|           | 5.6  |                        | 5-8           |

|           |      |                        | 5-8           |

|           |      |                        | 5-8           |

|           |      | 5.6.3 Aborted Command  |               |

|           |      | 5.6.4 ID Not Found     |               |

|           |      | 5.6.5 CRC Error ID     |               |

|           |      | 5.6.6 CRC Error Data   |               |

|           |      | 5.6.7 Bad Block Detect | 5 <b>-8</b> · |

|           |      |                        |               |

40.000

## WD1000 OEM Manual Table of Contents

•

## Page iii

· •••• .....

| Section 6 | COM               | MANDS                                   |

|-----------|-------------------|-----------------------------------------|

|           |                   |                                         |

|           | 6.1               | Command Summary 6-2                     |

|           |                   | 6.1.1 Stepping Rates 6-2                |

|           |                   |                                         |

|           | 6.0               |                                         |

|           | 6.2               | Type I Commands 6-3                     |

|           |                   | 6.2.1 Restore 6-3                       |

|           |                   |                                         |

|           | <i>(</i> <b>)</b> |                                         |

|           | 6.3               | Type II Commands 6-4                    |

|           |                   |                                         |

|           |                   |                                         |

|           |                   |                                         |

|           |                   | 6.3.1.2 Retries                         |

|           |                   | 6.3.1.3 Auto Restore                    |

|           |                   |                                         |

|           |                   |                                         |

|           |                   | 6.3.1.5 Error Severity Levels 6-5       |

|           |                   | 6.3.1.6 Normal Completion               |

|           | 6.4               |                                         |

|           |                   | 6.4.1 Write Sector                      |

|           |                   |                                         |

|           |                   | 6.4.1.1 Implied Seek                    |

|           |                   | 6.4.1.2 Retries                         |

|           |                   |                                         |

|           |                   |                                         |

|           |                   | 6.4.1.4 Hard Errors                     |

|           |                   | 6.4.2 Format Track 6-8                  |

|           |                   | 6.4.2.1 Implied Seek 6-8                |

|           |                   |                                         |

|           |                   | 6.4.2.2 Track Format                    |

| Dechier 7 |                   |                                         |

| Section 7 | PROG.             | RAMMING                                 |

|           | 7.1               | Setting up Task Files                   |

|           | -                 | 7.1.1 Cylinders and Tracks              |

|           | 72                |                                         |

|           | 1.• 6             | Type I Command Programming 7-3          |

|           |                   | 7.2.1 Use of Busy bit 7-3               |

|           |                   | 7.2.2 Use of Interrupts                 |

|           |                   |                                         |

|           | 7 7               |                                         |

|           | 7.3               | Type II Command Programming 7-5         |

|           |                   | 7.3.1 DMA Mode                          |

|           |                   | 7 7 7 Plook Nover                       |

|           |                   |                                         |

|           |                   |                                         |

|           |                   | 1.3.3.1 Partial Sector Transfers        |

|           |                   | 7.3.3.2 Interrupt Source Selection 7-6  |

|           |                   |                                         |

|           |                   |                                         |

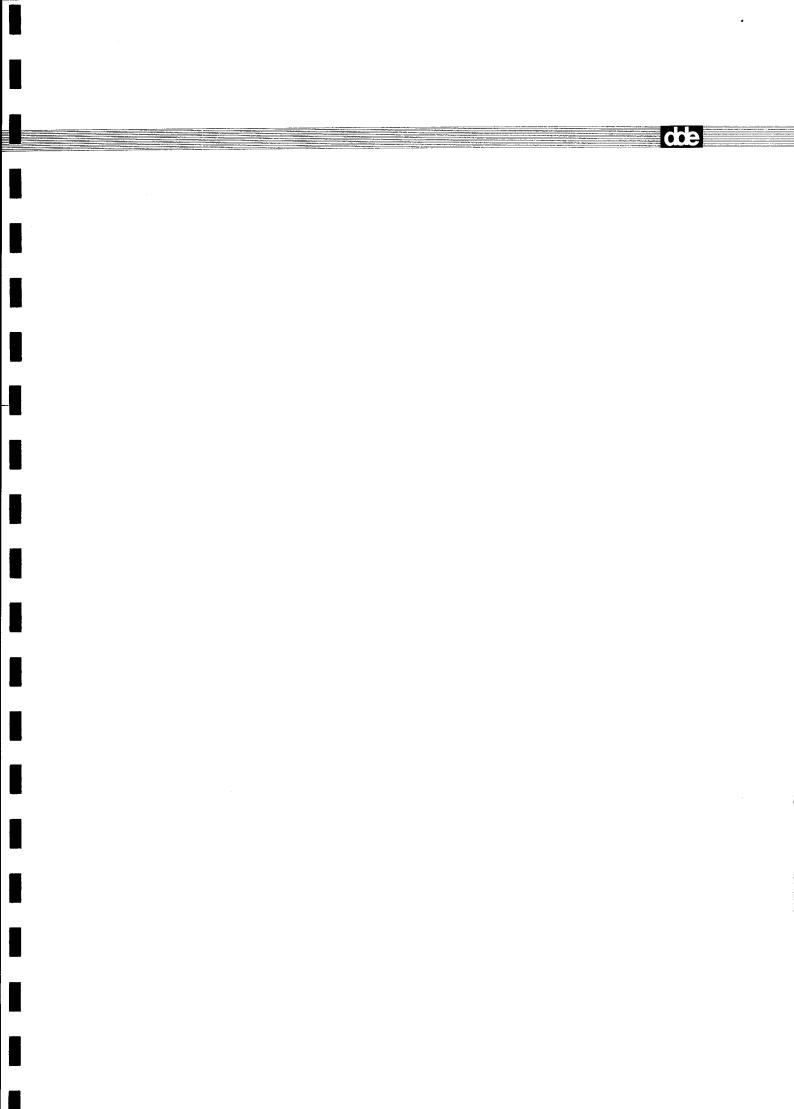

|           |                   | 7.3.3.4 Interrupt Selection Circuit 7-7 |

|           |                   | 7.3.4 Simulated Completions             |

|           | 7.4               | Type III Command Programming            |

|           |                   | 7.4.1 Formatting                        |

|           |                   |                                         |

|           |                   | 7.4.2 Interleaving 7-10                 |

|           | 7.5               | Bad Block Mapping                       |

|           |                   | 7.5.1 Sector Pre-allocation             |

|           |                   | 7.5.2 Alternate Tracks                  |

|           |                   |                                         |

|           |                   |                                         |

|           |                   | 7.5.4 Bad Block Bit 7-13                |

|           |                   |                                         |

ş

Page iv

Ì

ÿ

WD1000 OEM Manual Table Copplents

.

| Section 8 | THEORY OF OPERATION                                      |

|-----------|----------------------------------------------------------|

|           | 8.1 General                                              |

|           | 8.2 Processor Functions                                  |

|           | 8.2.1 Fast IO Select 8-2                                 |

|           | 8.2.2 Internal Bus Control 8-3                           |

|           | 8.2.3 Reset Circuit 8-3                                  |

|           | 8.2.4 Processor Power Supply                             |

|           |                                                          |

|           |                                                          |

|           | 8.2.6.1 RAM Addressing                                   |

|           | 8.2.6.3 RAM Accessing                                    |

|           | 8.2.6.4 Scratchpad Operations                            |

|           | 8.2.7 MAC Control Port 8-5                               |

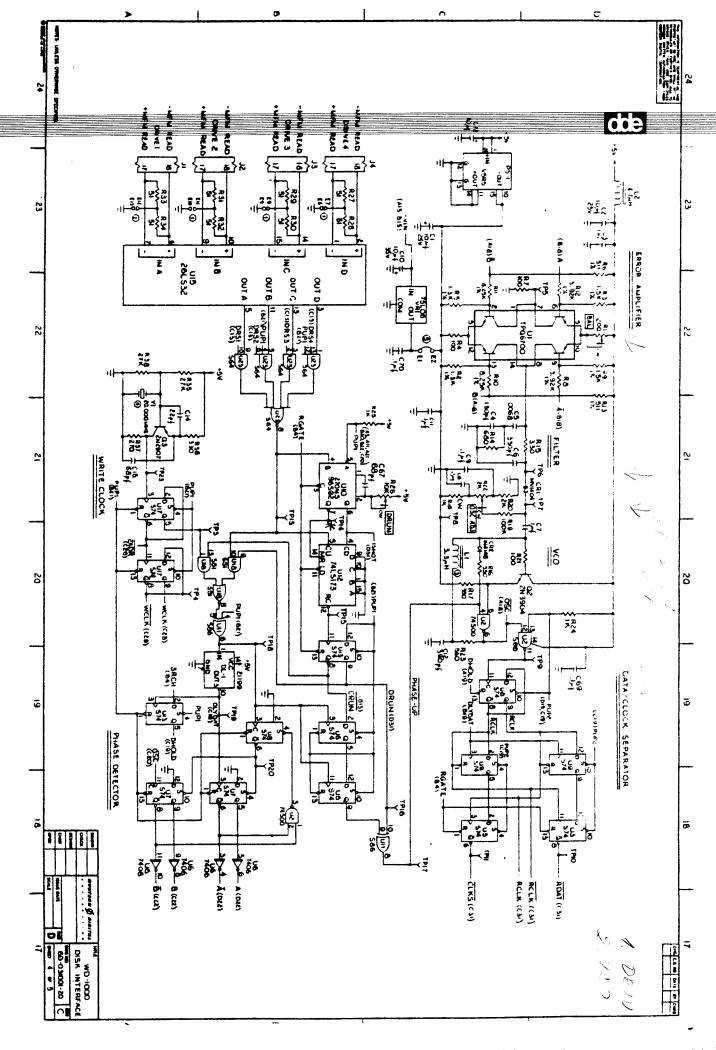

|           | 8.3 Serial Data Separation                               |

|           | 8.3.1 Incoming Data Selection                            |

|           | 8.3.2 Reference Clock                                    |

|           | 8.3.3 Clock Gating 8-7                                   |

|           | 8.3.4 High Frequency Detector                            |

|           |                                                          |

|           | 8.3.6 Error Amplifier                                    |

|           | 8.3.8 Window Extension                                   |

|           | 8.3.9 Clock Detection                                    |

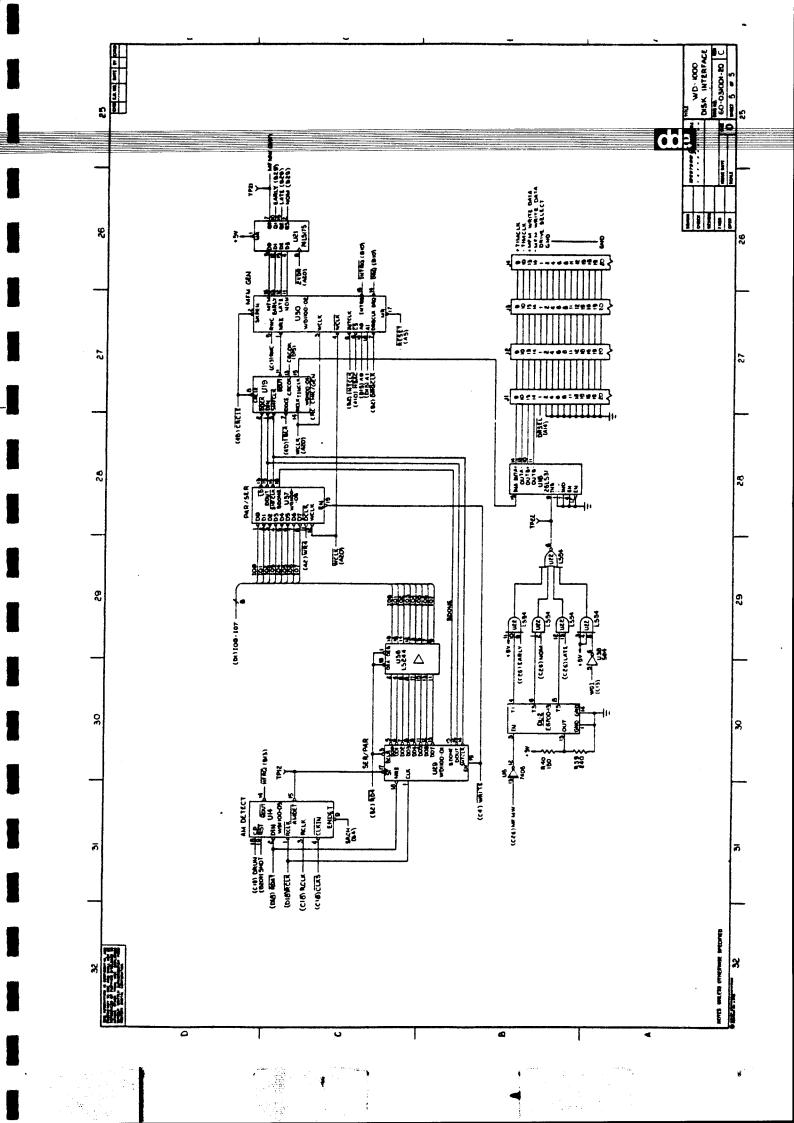

|           | 8.4 Data Conversion and Checking                         |

|           | 8.4.1 AM Detection                                       |

|           | 8.4.2 Serial to Parallel Conversion                      |

|           | 8.4.3 CRC Checking Circuit                               |

|           | 8.5 Serial Data Generation                               |

|           | 8.5.1 Parallel to Serial Conversion                      |

|           | 8.5.2 CRC Generation                                     |

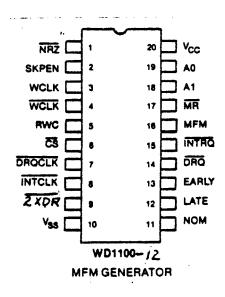

|           | 8.5.3 MFM Generation                                     |

|           | 8.5.3.1 Write Precompensation 8-19<br>8.6 Host Interface |

|           | 8.6 Host Interface                                       |

|           | 8.6.2 Bus Gating                                         |

|           | 8.6.3 Register Selection                                 |

|           | 8.6.4 Interrupts and DRQs                                |

|           |                                                          |

| Section 9 | MAINTAINENCE                                             |

|           | 9.1 VCO Adjustmments 9-2                                 |

|           | 9.2 Error Amplifier Adjustments (Static) 9-3             |

|           | 9.3 Error Amplifier Adjustments (Dynamic) 9-3            |

|           | 9.4 DRUN Adjustments                                     |

|           |                                                          |

.

| WD1000 OEM Ma<br>Table of Cont | tents                                    | Page v        |

|--------------------------------|------------------------------------------|---------------|

|                                | dde                                      |               |

| Appendix A                     | DISK DRIVER EXAMPLES                     | • •           |

|                                | A.1 Polled Status Driver                 |               |

|                                | A.1.1 Initialization                     |               |

|                                | A.1.2 Read Sector                        |               |

|                                | A.1.3 Write Sector                       |               |

|                                | A.1.4 Task File Updating                 | A-6           |

|                                | A.2 Interrupt Driven Driver              | A-7           |

|                                | A.2.1 Initialization                     |               |

|                                | A.2.2 Read Sector                        |               |

|                                | A.2.3 Write Sector                       | A-10          |

|                                | A.2.4 Task File Updating                 |               |

|                                | A.2.5 Interrupt Service routine          | A-12          |

| Appendix B                     | INTERLEAVE CALCULATING UTILITY           |               |

|                                | B.1 BASIC Interleave Calculating Program | B-2           |

|                                |                                          | 0 2           |

| Appendix C                     | PROGRAMMER'S QUICK REFERENCE             |               |

| ••                             | C.1 Task File                            | C-1           |

|                                | C.2 Valid Commands                       |               |

|                                | C.3 SDH Register Format                  |               |

|                                | C.4 Status and Error Register Bits       |               |

|                                |                                          | 0-2           |

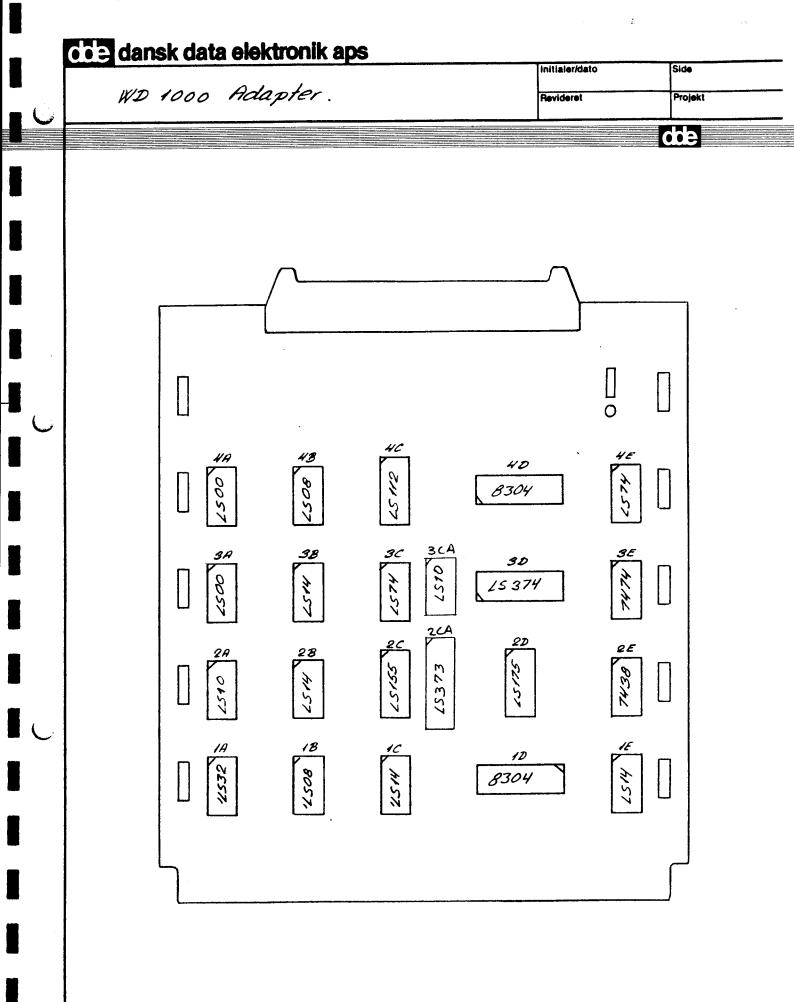

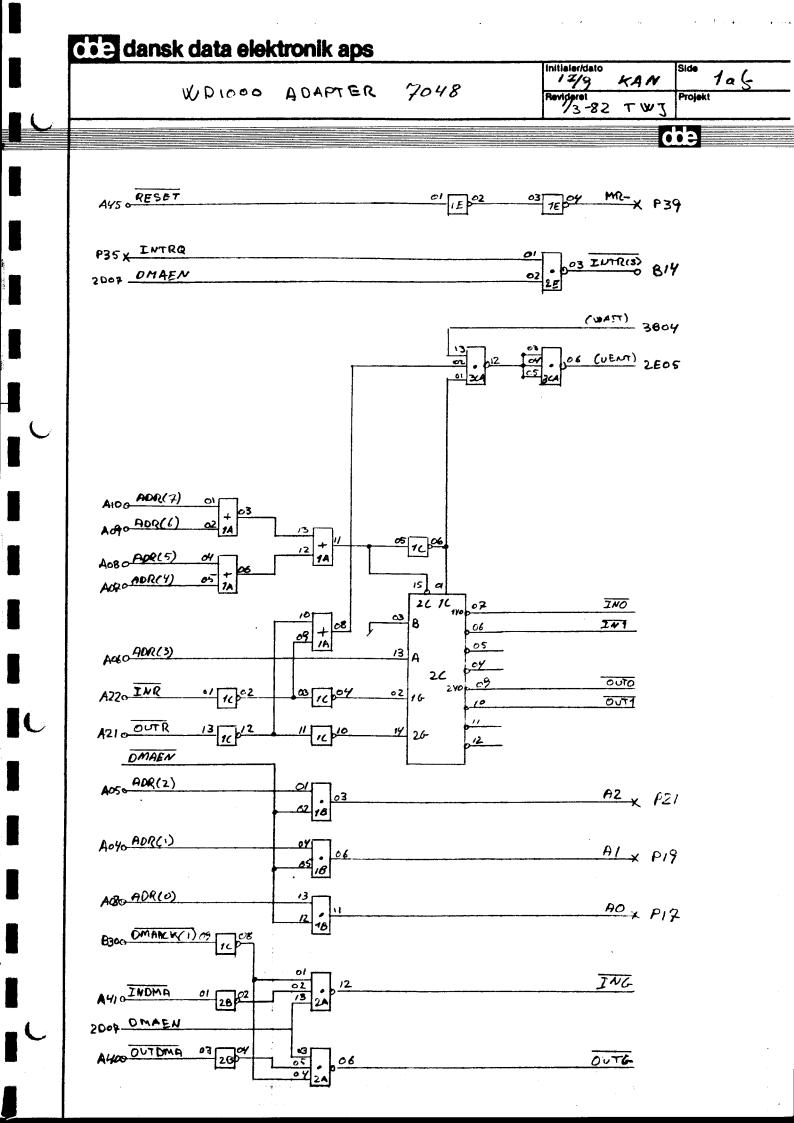

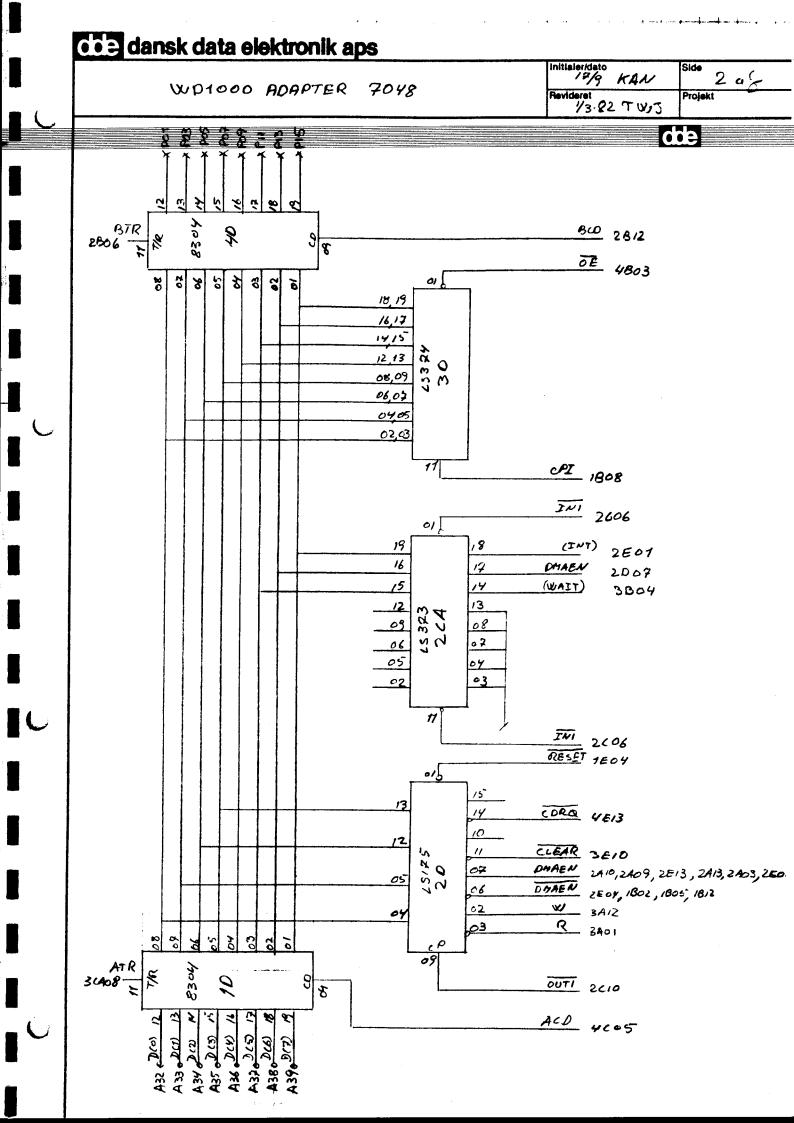

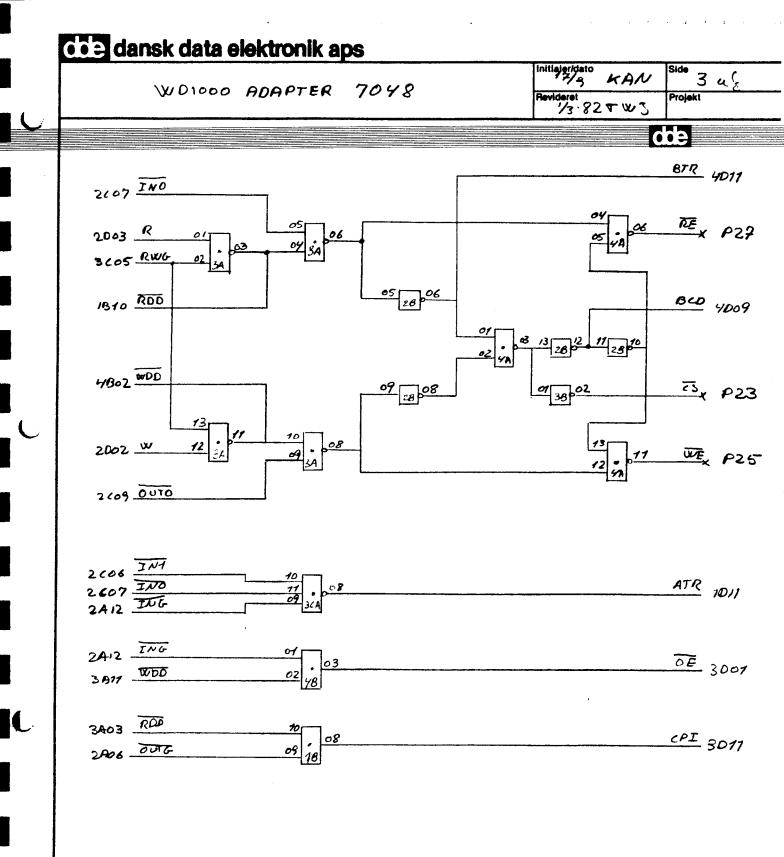

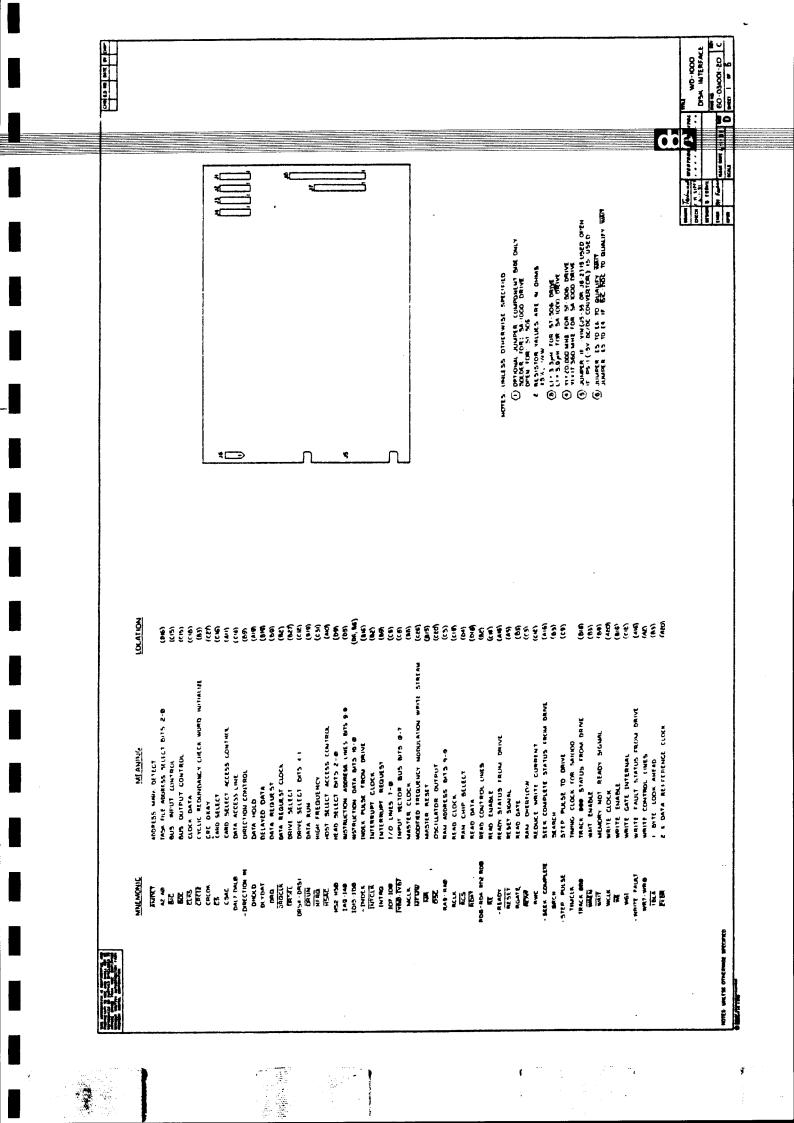

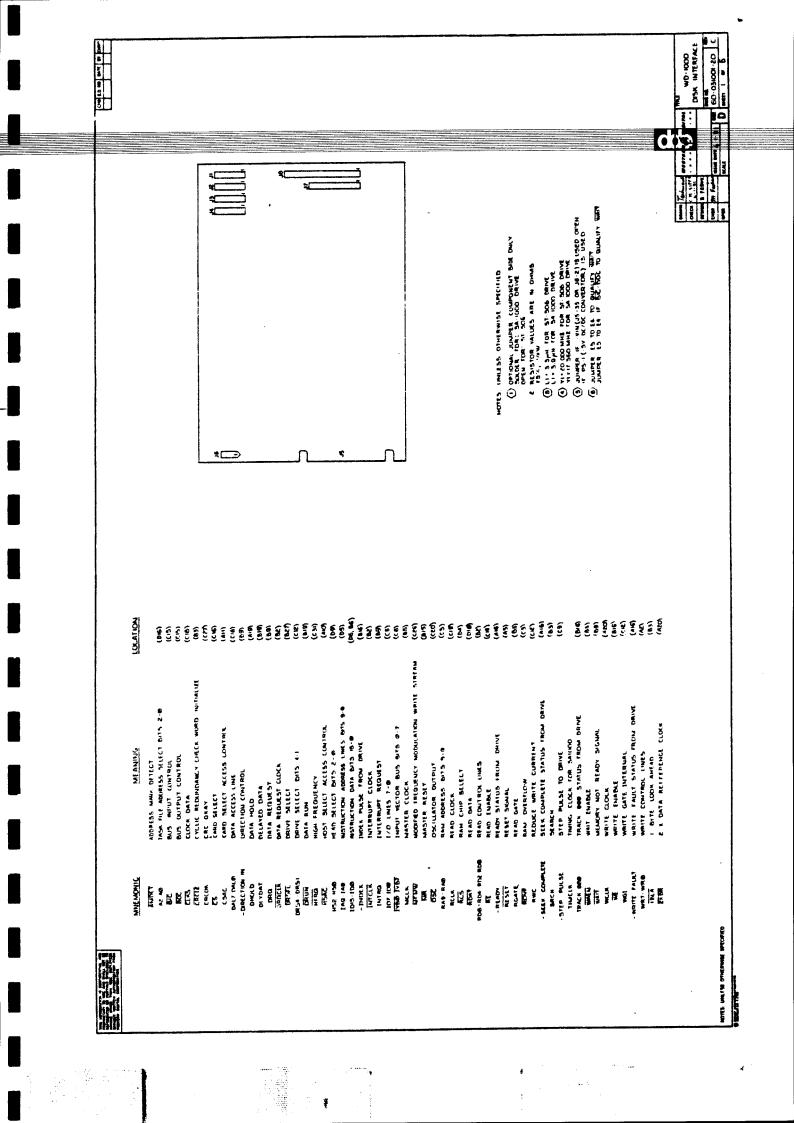

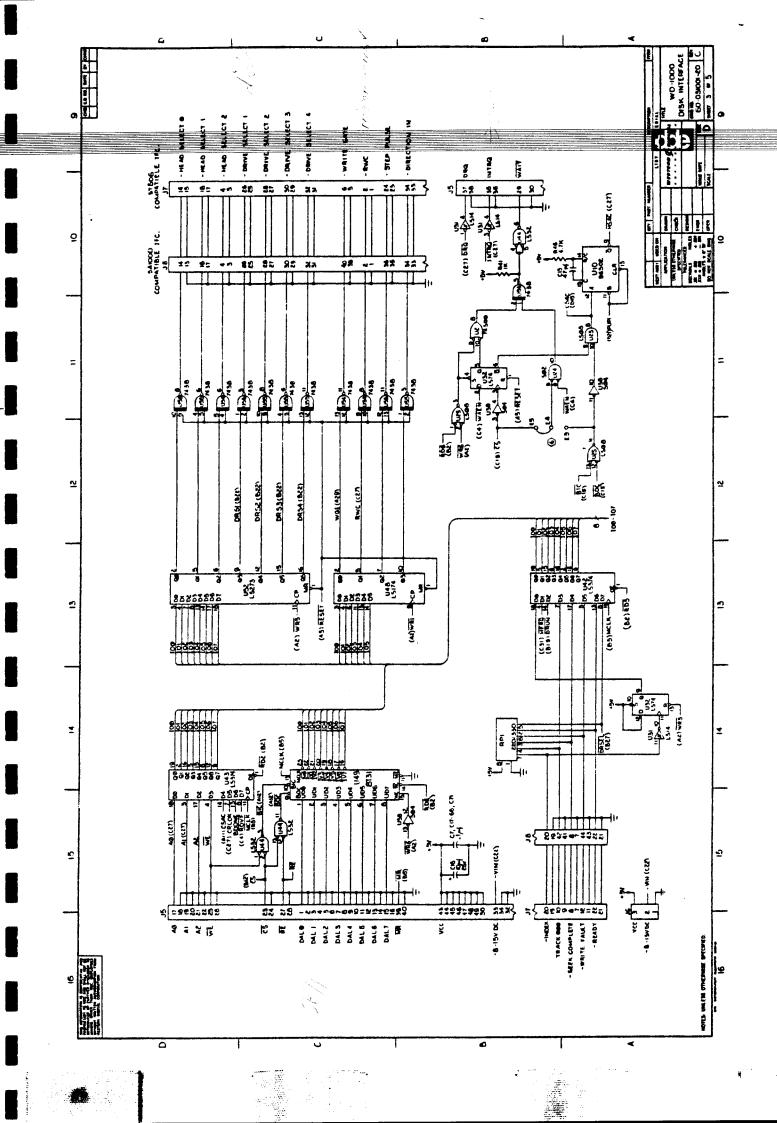

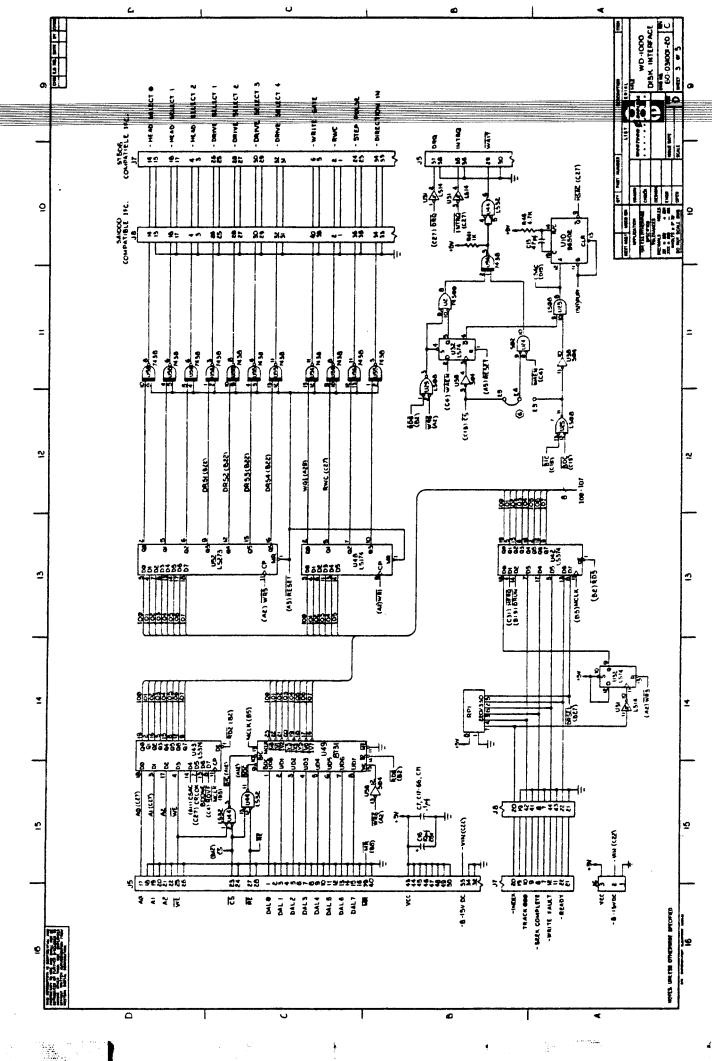

| Appendix D                     | DRAWINGS                                 |               |

|                                | D.1 Component Placement                  | . D <b>-1</b> |

|                                | D 2 Schematic                            |               |

| <i>D</i> •1 | compon |                                |   |

|-------------|--------|--------------------------------|---|

| D.2         | Schema | ticD-2                         | 1 |

|             | D.2.1  | MicrocontrollerD-3             | , |

|             |        | Bus Interface/Drive ControlD-4 |   |

|             |        | Data SeperatorD-5              |   |

|             |        | Serial Data Interface          |   |

<u>م</u>

WD1000 OEM Manual Introduction

de

#### Section 1

#### Introduction

#### 1.1 General Description

The WD1000 is a stand-alone, general purpose Winchester Controller board designed to interface up to four Winchester disk drives to a host processor. The drive signals are based upon the floppy look-alike interface available on the Shugart Associates' SA1000, the Seagate Technology ST506, the Quantum Q2000, and other compatible drives. All necessary buffers and receivers/drivers are included on the board to allow direct connection to the drive. Both 34 pin (5-1/4" drive) and 50 pin (8" drive) connectors are provided, as well as four 20 pin data connectors.

Communications to and from the host computer are made via a seperate computer access port. This port consists mainly of an 8 bit bi-directional bus and appropriate control signals. All data to be written to or read from the disk, status information, and macro commands are transferred via this 8 bit bus. An on board sector buffer allows data transfers to the host computer independent of the actual data transfer rate of the drive.

The WD1000 is based upon a propriety chip set called the WD1100, specifically designed for Winchester Control.

WD1000 OEM Manual Introduction

dde

### 1.2 Features

¥ Built-in Data Seperator ¥ Built-in Write Precompensation Logic ¥ Data rates up to 5 Mbits/sec Control for up to 4 drives # ¥ Control for up to 8 R/W heads Ħ 1024 Cylinder Addressing Range ¥ 256 Sector Addressing Range CRC Generation/Verification Automatic Formatting 128, 256, or 512 Bytes per sector (ROM selectable) Unlimited Sector Interleave Capability # Overlap Seek capability # Implied Seek on all commands Automatic Retries on all errors Automatic Restore and Re-seek on seek error ¥ 8 Bit Host Interface

#### WD1000 OEM Manual Introduction

#### Specifications 1.3

Encoding method: Cylinders per Head: Sectors per Track: Heads: Drive Selects: Step rate: Data Transfer Rate:

Write Precomp Time: Sectoring: Host Interface: Drive Capability: Drive Cable Length: Host Cable Length: Power Requirements:

Relative Humidity: MTBF: MTTR: Length: Width: Height: Mounting Centers:

Up to 1024 Up to 256 (512 byte sec) 8 4 10 uS to 7.5 mS (0.5 mS increments) 4.34 Mbits/sec (SA1000, Q2000) 5.000 Mbits/sec (ST506) 10 nanoseconds Soft 8 Bit bi-directional Bus 10 "LS" Loads 10 ft. (3 M) max 3 ft. (1 M) max. +5V +-5%, 3.0A Max (2.5A typ.) Ambient Temperature Operating: 0 C to 50 C (32 F to 122 F) 20% to 80% 10,000 POH 30 minutes 9.9 in. (24.9 cm) 6.8 in. (17.1 cm) 0.75 in. (1.9 cm)

MFM

6.375 X 9.375 in. (16 X 23.6 cm)

dde

WD1000 OEM Manual Interface Connectors

Page 2-1

de

## Section 2

## Interface Connectors

#### 2.1 Organization

The WD1000 has eight on board connectors. These connectors consist of a power connector, host interface connector, two drive control connnectors, and four high speed data cables.

The drive control cable is daisy-chained to each of the four drives. Although there are two drive control connectors, only one would normally be used for any particular configuration.

The drive data connectors carry differential signals and are radially connected. Up to four drives can be accomodated by the WD1000.

The host interface connector provides interface signals that are compatible with most microprocessors and many mini-computers with very little interfacing effort. Page 2-2

WD1000 OEM Manual Interface Connectors

dde

2.2 Host Interface Connector

The Host Interface connector (J5) consists of an eight bit bi-directional bus, three bit address bus, and seven control lines. All commands, status, and data are transferred over this bus. The control signals are as follows:

2.2.1 DALO-DAL7

2.2.6 WAIT-

8 bit bi-directional Data Access Lines. These lines remain in a high-impedance state whenever the CS- line is inactive.

- 2.2.2 CS-When Card Select- is active along with REor WE-, Data is read or written via the DAL bus. CS- must make a transition for each byte read from or written to the task file.

- 2.2.3 WE-When Write Enable- is active along with CS-, the host may write data to a selected register of the WD1000.

- 2.2.4 RE-When Read Enable- is active along with CS-, the host may read data from a selected register of the WD1000.

- 2.2.5 A2-A0 These three Address Lines are used to select one of eight registers in the Task File. They must remain stable during all read and write operations.

Upon receipt of a CS-, the WAIT- line may go active. It returns to the inactive state when the DAL lines are valid on a read, or data has been accepted on a write.

2.2.7 INTRQ The INTerrupt ReQuest Line is activated whenever a command has been completed. It is reset to the inactive state when the Status Register is read, or a new command is loaded via the DAL lines.

| WD1000 OEM Manual    | Pa  | ge 2-3 |

|----------------------|-----|--------|

| Interface Connectors | dde |        |

.

| 2.2.8 DRQ         | The Data ReQuest line is activated whenever<br>the sector buffer contains data to be read<br>by the host, or is awaiting data to be<br>loaded by the host. This line is reset<br>whenever the Data Register is read from or<br>written to. The DRQ line will continue to<br>toggle until the buffer is exausted or until<br>a write or read is performed on the<br>Cylinder Low register. |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.2.9 MR-         | The Master Reset line initializes all<br>internal logic on the WD1000. Sector Number,<br>Cylinder Number and SDH are cleared,<br>stepping rate is set to 7.5 mS, Write<br>Precomp is set to cylinder 128, and Sector<br>Count is set to 1. The DRQ and INTRQ lines<br>are undefined.                                                                                                      |

| 2.2.10 -V         | Optional -V input from the host supplies -8<br>to -15 to the on-board -5 volt regulator<br>(VR1). This power input is also available on<br>J6, pin 2.                                                                                                                                                                                                                                     |

| 2.2.11 GND        | All even numberd pins on this connecter are<br>to be used as signal grounds. Power grounds<br>are available on J6, pin 1.                                                                                                                                                                                                                                                                 |

| 2.2.12 <b>+5V</b> | 8 power pins for regulated +5 volts. This power input is also available on J6, pin 3.                                                                                                                                                                                                                                                                                                     |

ŧ

Page 2-4

WD1000 OEM Manual Interface Connectors

dde

## 2.2.13 50 Pin Host Interface Connector

The host interface connector (J5) is a 50 pin card edge connector on tenth-inch centers that mates with Burndy #FRE 50 B-3. The cable used should be flat ribbon cable or twisted pair with a length of less than three feet. The connector pin-outs are as follows:

| Signal Ground                                                                                                         | Signal Pin                                                                                          | Signal Name                                                                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal Ground<br>2<br>4<br>6<br>8<br>10<br>12<br>14<br>16<br>18<br>20<br>22<br>24<br>26<br>28<br>30<br>32<br>34<br>36 | 1<br>3<br>5<br>7<br>9<br>11<br>13<br>15<br>17<br>19<br>21<br>23<br>25<br>27<br>29<br>31<br>33<br>35 | DALO<br>DAL1<br>DAL2<br>DAL3<br>DAL3<br>DAL5<br>DAL5<br>DAL6<br>DAL7<br>A0<br>A1<br>A2<br>CS-<br>WE-<br>RE-<br>WAIT-<br>Not Connected<br>-V<br>INTRQ |

| 38<br>40                                                                                                              | 37<br>39<br>41<br>42<br>43 <b>-</b> 50                                                              | DRQ<br>MR-<br>Not Connected<br>Not Connected<br>+5V                                                                                                  |

WD1000 OEM Manual Interface Connectors Page 2-5

cde

## 2.3 Drive Control Connectors

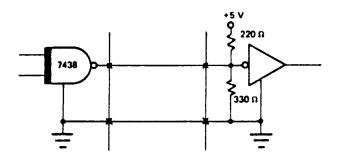

The drive control connector is a (relatively) low speed bus that is daisy chain connected to each of the drives (up to four) in the system. To properly terminate each TTL level output signal from the WD1000, the last drive in the daisy chain should have a 220/330 ohm line termination resistor pack installed. All other drives should have no termination. Drive control signals are as follows:

2.3.1 RWC-

When the Reduce Write Current line is activated with write gate, a lower write current is used to compensate for greater bit packing density on the inner cylinders. The RWC line is activated when the cylinder number is greater than or equal to four times the contents of the Write Precomp Register. This output is valid only during Write and Format Commands.

2.3.2 Write Gate-

This output signal allows data to be written on the disk.

2.3.3 Seek Complete-Informs the WD1000 that the head of the selected drive has reached the desired cylinder and has stabilized. Seek Complete is not checked after a SEEK command, thus allowing overlapped seeks.

2.3.4 Track 000-Indicates that the R/W heads are positioned on the outermost cylinder. This line is sampled immediately before each step is issued.

2.3.5 Write Fault-Informs the WD1000 that some fault has occured on the selected drive. The WD1000 will not execute commands when this signal is true.

2.3.6 HSO-HS2-Head Select lines are used by the WD1000 to select a specific R/W head on the selected drive. Page 2-6

WD1000 OEM Manual Interface Connectors

dde

2.3.7 Index-Is used to indicate the index point for synchronization during formatting and as a time out mechanism for retries. This signal should pulse once each rotation of the disk.

- 2.3.8 **Ready-**Informs the WD1000 that the desired drive is selected and that its motor is up to speed. The WD1000 will not execute commands unless this line is true.

- 2.3.9 Step-This line is pulsed once for each cylinder to be stepped. The direction of the step will be determined by the DIRECTION line. The step pulse period is determined by the internal stepping rate register during implied seek operations or explicitly during Seek and Restore commands. During auto restore, the step pulse period is determined by the SEEK COMPLETE time from the drive.

- 2.3.10 Direction Determines the direction of motion of the R/W head when the step line is pulsed. A high on this line defines the direction as out and a low defines direction as in.

- 2.3.11 DS1-DS4-These four Drive Select lines are used to select one of four possible drives.

2.3.12 Control Driver/Receiver The control lines have the following electrical specifications:

True=0.0 V to 0.4 V at  $I_{in}$  = 40 ma.(max) False=2.5 V to 5.25 V at  $I_{in}$  =  $^{\circ}$ 0 ma.(open)

#### WD1000 OEM Manual Interface Connectors

#### 2.3.13 50 Pin Drive Control Connector

This drive control connector (J8) is a 50 pin vertical header on tenth-inch centers that mates with Burndy #FRS50BS. The cable used should be flat ribbon cable or twisted pair with a length of less than 10 feet. The cable pin-outs are as follows:

| Signal Ground | Signal Pin | I/0        | Signal Name          |

|---------------|------------|------------|----------------------|

| +             | 2          | +<br>  0   | +<br>  _RWC          |

|               | 4          | 0          | -Head Select 2       |

| 3             | 6          | <br>I<br>I | NC I                 |

| 7             | 8          | I          | -Seek Complete       |

| 9             | 10         | 1          | NC                   |

| 11            | 12         |            | NC                   |

| 13            | 14         | 0          | -Head Select 0       |

| 15            | 16         |            | NC<br>-Head Select 1 |

| 17            | 18         | 0<br>I     | -Index               |

| 19            | 20<br>22   |            | -Ready               |

| 21            | 24         |            | NC                   |

| 25            | 26         | 0          | -Drive Select 1      |

| 27            | 28         | ŏ          | -Drive Select 2      |

| 29            | 30         | Ō          | -Drive Select 3      |

| 31            | 32         | 0          | -Drive Select 4      |

| 33            | 34         | 0          | -Direction In        |

| 35            | 36         | 0          | -Step                |

| 37            | 38         |            | NC                   |

| 39            | 40         | 0          | -Write Gate          |

| 41            | 42         | I          | -TR000               |

| 43            | 44         | I          | -Write Fault         |

| 45            | 46         |            | NC                   |

| 47            | 48         |            | NC<br>NC             |

| 49            | 50         |            |                      |

Page 2-7

dde

WD1000 OEM Manual Interface Connectors

**dd**e

#### Page 2-8

### 2.3.14 34 Pin Drive Control Connector

This drive control connector (J7) is a 34 pin vertical header on tenth-inch centers that mates with Burndy #FRS34BS. The cable used should be flat ribbon cable or twisted pair with a length of less than 10 feet. The cable pin-outs are as follows:

| Signal Ground                                                                                       | Signal Pin                                                                                           | 1/0                                                                               | Signal Name                                                                                                                                                                                                                                                    |                                         |

|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| 1<br>3<br>5<br>7<br>9<br>11<br>13<br>15<br>17<br>19<br>21<br>23<br>25<br>27<br>29<br>31<br>33<br>35 | 2<br>4<br>6<br>8<br>10<br>12<br>14<br>16<br>18<br>20<br>22<br>24<br>26<br>28<br>30<br>32<br>34<br>36 | 0<br>0<br>1<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | -RWC<br>-Head Select 2<br>-Write Gate<br>-Seek Complete<br>-TR000<br>-Write Fault<br>-Head Select 0<br>NC<br>-Head Select 1<br>-Index<br>-Ready<br>-Step<br>-Drive Select 1<br>-Drive Select 2<br>-Drive Select 3<br>-Drive Select 4<br>-Direction In<br>-Step | • • • • • • • • • • • • • • • • • • • • |

Page 2-10

WD1000 OEM Manual Interface Connectors

dde

1.

¢

ş

#### 2.5 Power Connector

A three pin molex connector (J6) is provided for power input to the board. The customer supplied mating connector housing is Molex 03-09-1032. The pin-outs are as follows:

| +- | Pin         | Signal Name                                         |

|----|-------------|-----------------------------------------------------|

| +- | 1<br>2<br>3 | GROUND<br>-8 to -15 V unregulated<br>+5 V regulated |

Page 3-2

1.2

WD1000 OEM Manual Interface Timing

dde

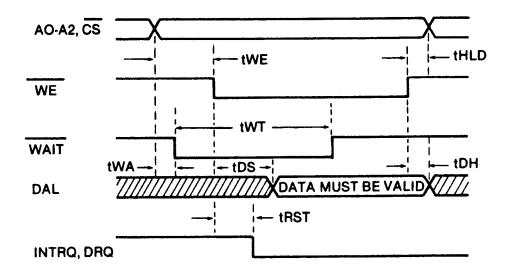

## 3.1.2 Host Write Timing

.

| SYMBOL                              | CHARACTERISTIC                                     | MIN | MAX        | UNITS    |

|-------------------------------------|----------------------------------------------------|-----|------------|----------|

| <br>twe                             | WE- active from A0-2, CS-                          | 0   |            | nS       |

| tWA                                 | WAIT- active from CS-<br>INTRQ, DRQ reset from WE- |     | 100<br>100 | nS<br>nS |

| trst<br>t <sub>DS</sub><br>thd      | Data valid delay from WE-<br>Data Hold from WE-    | 20  | 100        | nS<br>nS |

| t <sub>WT</sub><br>t <sub>HLD</sub> | Wait active period<br>Hold time AO-2, CS-          | 0   | 6          | uS       |

| чнгр                                | from WE-                                           | 0   |            |          |

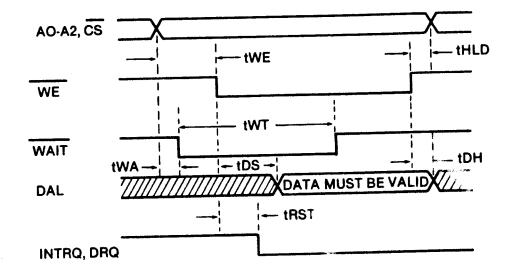

## WD1000 OEM Manual Interface Timing

Page 3-2

| SYMECL                             | CHARACTERISTIC                                         | MIN | MAX        | UNITS    |

|------------------------------------|--------------------------------------------------------|-----|------------|----------|

|                                    | WE- active from A0-2, CS-                              | 0   |            | nS       |

| twe<br>twa                         | WATT- active from CS-                                  |     | 100<br>100 | nS<br>nS |

| tRST                               | INTRQ, DRQ reset from WE-<br>Data valid delay from WE- |     | 100        | nS       |

| tDS                                | Data Hold from WE-                                     | 20  |            | nS       |

| t <sub>HD</sub><br>t <sub>WT</sub> | Wait active period                                     | 0   | 6          | uS       |

|                                    | Hold time A0-2, CS-<br>from WE-                        | 0   |            |          |

#### WD1000 OEM Manual Interface Timing

#### Page 3-3

de

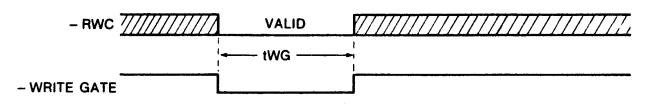

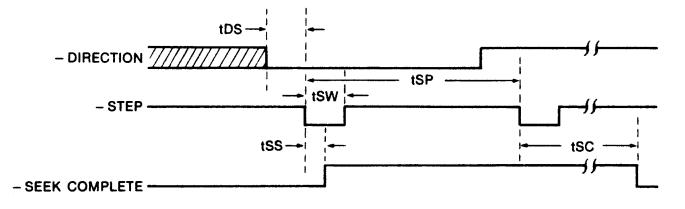

3.2 Drive Control Timing

| SYMBOL          | CHARACTERISTIC               | MIN    | MAX     | UNITS |

|-----------------|------------------------------|--------|---------|-------|

| t <sub>WG</sub> | Write gate pulse width 1     | sector | 2 rotal | tion  |

| t <sub>DS</sub> | Direction to step delay      | 250    |         | nS    |

| tsw             | Step pulse width             | 5 (ty  | pical)  | uS    |

|                 | Programmed Step pulse period | 0.01   | 7.5     | uS    |

| tss             | Step to Seek Complete false  |        | 9       | uS    |

| t <sub>SC</sub> | Last Step to Seek Complete   |        | 128     | Index |

| - 50            |                              |        |         | times |

Notes:

- 1. Write gate pulse width will vary depending on the sector size and the rotation rate of the disk.

- 2. Step pulse period will be equal to seek complete time during auto restore.

- DR SEL, HD SEL

## Page 3-4

WD1000 OEM Manual Interface Timing

dde

•

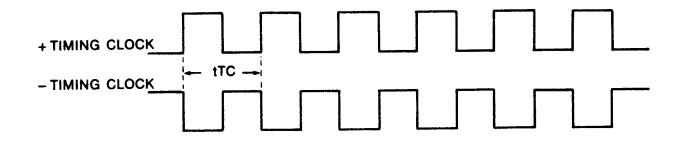

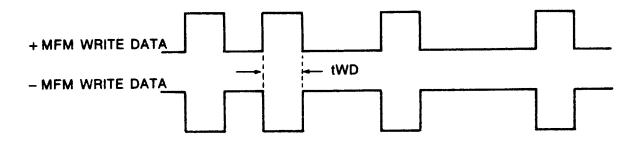

## 3.3 Drive data timing

| +- | SYMBOL                                                | CHARACTERISTIC                                                         | MIN                 | MAX             | UNITS         |

|----|-------------------------------------------------------|------------------------------------------------------------------------|---------------------|-----------------|---------------|

| ł  | t <sub>TC</sub><br>t <sub>WD</sub><br>t <sub>RD</sub> | Timing clock period<br>Write data pulse width<br>Read data pulse width | WCLK/16<br>60<br>25 | (typica)<br>120 | )<br>nS<br>nS |

WD1000 OEM Manual Host Interfacing

dde

#### Section 4

#### Host Interfacing

The WD1000 is designed to easily interface to most micro-computers and many mini-computers. All interfacing is done through the Host Interface Connector (J5). The interface is very similar to Western Digital's family of LSI peripheral chips. There's only one exception: the inclusion of a WAIT line.

4.1 Waits

The WAIT- control line goes true whenever either of the following are true:

- o The WD1000 is accessing data internally to send to the host during a read operation

- o The WD1000 has not accepted the data from the host during a write operation.

The definition of the WAIT- line is very similar to the WAIT signal found on many Intel and Zilog products. WAIT- is also similar to the REPLY signal on Western Digital and DEC processors.

Wait will not neccessarily make a transition for each access to the WD1000. When the WD1000 can return the requested data within 100 nS, there will not be any transition of the WAIT- line. This should be interpreted as an instant REPLY on Western Digital Processors.

If the WD1000 cannot return the requested data within 100 nS, it will assert its WAIT- line. The period of the WAIT- signal will vary from 750 nS to 6 uS with 1.25 uS being about average. The period of WAIT- only approaches 6 uS during a read or write which happens immediately <u>after</u> a command is written to the command register. This means that longer waits may be encountered during the first read or write to any WD1000 register if that first read or write happens within approximately 6 uS of a command being issued.

During the time that WAIT- is asserted, the host system must hold all of its strobe and address lines stable. On write operations, the DAL lines

| Page 4-2 | WD1000 OEM Ma | nual |

|----------|---------------|------|

| 1450     | Host          |      |

must also be held stable.

#### 4.1.1 WAIT timing

The user can modify the timing of the wait signal by selecting a jumper. The WD1000 is shipped with a jumper (or trace) between E4 and E5. This enables waits as soon as the CS- signal is asserted. This timing is a requirement for some processors and compatible with most. If the host system requires the WAIT- signal to be asserted only when RE- or WE- are asserted in conjunction with CS-, the trace at E4 and E5 should be cut and a jumper should be installed between E4 and E3.

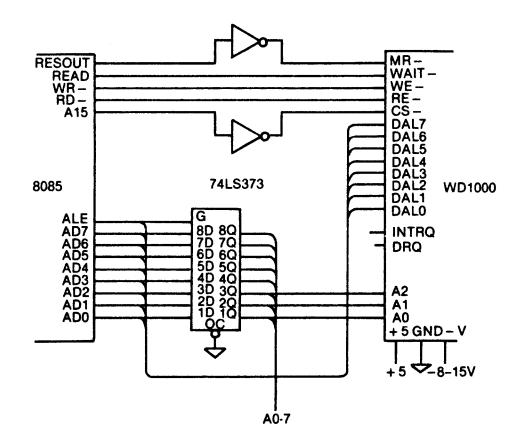

#### 4.2 Host interfacing example

The example below illustrates the absolute minimum of hardware required to interface to a small 8085 microcomputer system. In this example, we are not using buffers or completely decoding the I/O. In a real system, the user would probably want to completely decode the I/O to minimize the amount of I/O or memory space required to interface the WD1000. If the interface cable length is kept to a few inches, it is often permissible to interface it directly to a microcomputer's <u>buffered</u> bus.

.

1 <del>1</del>.7

WD1000 OEM Manual Task File Page 5-1

dde

## Section 5

## **Task File**

5.1 <u>Task File Basics</u> The WD1000 performs all disk functions through a set of registers called the Task File. These registers are loaded with parameters such as Sector Number, Cylinder Number, etc., prior to issuing a command. Individual registers are selected via AO-2. The following registers are available:

#### 5.2 Register Array

| CS-                                  | <br>A2                               |  | A 1                                  | -+- | AO                                        | +                                                                  | RE-                                                                                                                                                   | • • • • • • • • • | WE-                                                                                                                                                   | -+<br> <br> |

|--------------------------------------|--------------------------------------|--|--------------------------------------|-----|-------------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 1<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | X<br>0<br>0<br>0<br>1<br>1<br>1<br>1 |  | X<br>0<br>1<br>1<br>0<br>0<br>1<br>1 |     | X<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1 | *<br>*<br>*<br>*<br>*<br>*<br>*<br>*<br>*<br>*<br>*<br>*<br>*<br>* | Deselected<br>Data Register<br>Error Register<br>Sector Count<br>Sector Number<br>Cylinder Low<br>Cylinder High<br>Size/Drive/Head<br>Status Register |                   | Deselected<br>Data Register<br>Write Precomp<br>Sector Count<br>Sector Number<br>Cylinder Low<br>Cylinder High<br>Size/Drive/Head<br>Command Register |             |

Page 5-2

WD1000 OEM Manual Task File

dde

#### 5.3 Register Definitions

#### 5.3.1 Command Register

All commands are loaded into this register after the task registers have been set. Writing to this register will cause the INTRQ Line to be reset. The Command Register is a write-only register.

#### 5.3.2 Status Register

After execution of a command, the Status Register is internally loaded with status information pertaining to the command executed. The Host must read this register to determine successful execution of the command. The Status Register is a read-only register; it cannot be written to by the host. If the busy bit is set, no other bits in this register are valid. Accessing this register will cause the INTRQ line to be reset. WD1000 OEM Manual Task File

•

| .3.3        | SDH R       | egister                                   | Drive :                              | select,<br>sister                         | contai<br>and Hea<br>is a R/W                 | ad sel                                 | lect b       |                                          |

|-------------|-------------|-------------------------------------------|--------------------------------------|-------------------------------------------|-----------------------------------------------|----------------------------------------|--------------|------------------------------------------|

|             |             | Bit<br>Function                           | ++-                                  | Sec                                       | 43<br>Drive<br>Select                         | Hea                                    | +<br>ad      |                                          |

| Bit<br>6    | Bit<br>5    | Sect                                      | or Size                              | -+                                        | +<br>  Bit<br>  4                             | Bit<br>3                               | Drive        | Selected                                 |

| 0<br>0<br>1 | 0<br>1<br>1 | 512                                       | Bytes<br>Bytes<br>Bytes              | -+<br> <br> <br>                          | 0<br>0<br>1<br>1                              |                                        | Driv<br>Driv | e Sel 0<br>e Sel 1<br>e Sel 2<br>e Sel 3 |

|             |             | Bit<br>2                                  | Bit<br>1                             | Bit<br>O                                  | Head Se                                       | lected                                 | ·-+<br> <br> |                                          |

|             |             | 0<br>0<br>0<br>1<br>0<br>1<br>1<br>1<br>1 | 0<br>0<br>1<br>1<br>0<br>0<br>1<br>1 | 0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0 | Hea<br>Hea<br>Hea<br>Hea<br>Hea<br>Hea<br>Hea | d 1<br>d 2<br>d 3<br>d 4<br>d 5<br>d 6 |              |                                          |

| Page 5-4 | WD1000 | OEM. | Manua] |

|----------|--------|------|--------|

|          |        |      | e File |

#### 5.3.4 Cylinder Number

These two registers form the cylinder number where the head is to be positioned on a Seek, Read, or Write command. Internally, a separate set of Cylinder register values are maintained for each drive. The two least significant bits of the Cylinder High register form the most significant bits of the cylinder number as illustated below:

|                | Cylinder High             | Cylinder Low              |

|----------------|---------------------------|---------------------------|

| Register bits: | 17 16 15 14 13 12 11 10 1 | 7 6 5 4 3 2 1 0           |

| Cylinder bits: | A 9                       | 17 16 15 14 13 12 11 10 1 |

### 5.3.5 Sector number

This register is loaded with the desired sector number prior to a Read or Write command. The Sector Number register is a R/W register and may be read or written to by the host.

### 5.3.6 Sector Count

This register is loaded with the number of sectors to be formatted during a Format command. During the Format command, this register is decremented to zero and must be re-loaded for each format operation.

### 5.3.7 Error Register

This Register contains specific fault information pertaining to the last command executed. This register is valid only if the Error bit in the Status register is set. The Error Register is read only.

dbe

#### 5.3.8 Write Precomp The Write Precompensation Register holds the cylinder number where the RWC line will be asserted and Write Precompensation logic is to be turned on. This write-only register is loaded with the cylinder number divided-by-4 to achieve a range of 1024 write example, if For cylinders. precompensation is desired for cylinder 128 (80 Hex) and higher, this register must The Write with 32 (20 Hex). be loaded is fixed at 10 Pre-compensation delay nanoseconds from nominal.

### 5.3.9 Data Register

This register is the user's window to the on-board full sector buffer. It contains the next byte of data to be written to or read from the internal sector buffer. The Data Register is accessed once for each When the DRQ (Data byte in the sector. Request) line is asserted, the sector buffer contains data in a read command, or is awaiting data to be written during a write command into the Data Register. If the WD1000 is interfaced using programmed I/O, data transfers to this register can be implemented using block moves. This register may not be read from or written to except in the context of a valid command.

WD1000 OEM Manual Task File

dde

### 5.4 Status Registers

There are two registers in the WD1000 that are used to monitor the execution of commands. They are the Status Register and the Error Register. Each bit of these registers is used to define a particular type of status or error condition:

|   | Bit | ł   | Status Register | Error Register         |

|---|-----|-----|-----------------|------------------------|

| - | 7   | -+- | Busy            | Bad Block Detect       |

|   | 6   | Ì   | Ready           | CRC Error - Data Field |

|   | 5   | Ì   | Write Fault     | CRC Error - ID Field   |

|   | 4   |     | Seek Complete   | ID Not Found           |

|   | 3   | Ì   | Data Request    | -                      |

|   | 2   | Ì   |                 | Aborted Command        |

|   | 1   | 1   | -               | TROOO Error            |

|   | 0   | 1   | Error           | DAM not found          |

- 5.5 Status Register Bits

- 5.5.1 Error

When set, indicates that one or more bits are set in the Error Register. It provides an efficient means of checking for an error condition by the host. This bit is reset on receipt of a new command.

5.5.2 Data Request

Functions identically to the DRQ line. When set, it indicates that the sector buffer is ready to accept data or contains data to be read out by the host. The data request bit is reset when the sector buffer has been fully read from or written to. Normally, the host need not consult this bit to determine if a byte should be transferred.

### 5.5.3 Seek Complete

Indicates the condition of the seek complete line on the selected drive.

#### 5.5.4 Write Fault

Indicates the condition of the Write Fault Line on a selected drive. The WD1000 will not execute any command if this bit is set. •

|       | Peedu | dde                                                  |

|-------|-------|------------------------------------------------------|

| 2.2.2 | Ready | Indicates the condition of the READY line            |

|       |       | of the selected drive. The WD1000 will not           |

|       |       | execute any commands unless the ready bit<br>is set. |

| 5.5.6 | Busy  |                                                      |

|       | -     | After issuing a command, this bit will               |

|       |       | be set indicating that the WD1000 is busy            |

|       |       | executing a command. No other bits or                |

|       |       | registers are valid when this bit is set.            |

.

Page 5-8

WD1000 OEM Manual Task File

dde

### 5.6 Error Register Bits

5.6.1 DAM not found Will be set during a Read Sector command if, after successfully identifying the ID field, the Data Address mark was not detected within 16 bytes of ID field.

5.6.2 TROOD Error Will be set during a Restore command if, after issuing 1023 stepping pulses, TRACK 000 line was not asserted by the drive.

#### 5.6.3 Aborted Command

Indicates that a valid command has been received that cannot be executed based on status information from the drive. For example, if a write sector command has been issued while the Write Fault line is set, the Aborted command bit will be set. Interrogation of the Status and/or Error Registers by the host must be performed to determine the cause of failure.

#### 5.6.4 ID Not Found

When set, this bit indicates that an ID field containing a specified cylinder, head, sector number or sector size was not found.

### 5.6.5 CRC Error ID Indicates that a CRC error was encountered in an ID field.

5.6.6 CRC Error Data

Indicates that a CRC error was encountered in a data field during a Read Sector Command.

#### 5.6.7 Bad Block Detect

Indicates that a Bad Block mark has been detected in the specified ID field. If the command issued was a write sector command, no writing will be performed. If generated from a read sector command, the data field will not be read. Note that bad block will not be detected if the flaw is in the ID field. WD1000 OEM Manual Commands

dde

# Section 6

## Commands

The WD1000 executes five easy to use macro commands. Most commands feature automatic 'implied' seek, which means the host system need not tell the WD1000 where the R/W heads of each drive are or when to move them. The controller automatically performs all needed retries on all errors encountered including data CRC errors. If the R/W head mis-positions, the WD1000 will automatically perform a restore and a re-seek. If the error is completely unrecoverable, the WD1000 will simulate a normal completion to simplify the host system's software.

Commands are executed by loading the command byte into the Command Register while the controller is not busy. (Controller will not be busy if it has completed the previous command.) The task file must be loaded prior to issuing a command. No command will execute if the Seek Complete or Ready lines are false or if the Write Fault line is true. Normally it is not necessary to poll these signals before issuing a command. If the WD1000 receives a command that is not defined in the following table, undefined results will occur. Page 6-2

WD1000 OEM Manual Commands

6.1 Command Summary

For ease of discussion, commands are divided into three types which are summarized in the following table:

| TYPE | COMMAND      | +<br> <br> | 7 | 6 |   | BIT: | -  | 2              | 1              | 0              |

|------|--------------|------------|---|---|---|------|----|----------------|----------------|----------------|

| i I  | Restore      |            | 0 | 0 | 0 | 1    | r3 | r <sub>2</sub> | r <sub>1</sub> | r <sub>0</sub> |

| I    | Seek         | 1          | 0 | 1 | 1 | 1    | r3 | r <sub>2</sub> | r <sub>1</sub> | r <sub>0</sub> |

| II   | Read Sector  |            | 0 | 0 | 1 | 0    | D  | 0              | 0              | 0              |

|      | Write Sector | +          | 0 | 0 | 1 | 1    | 0  | 0              | 0              | 0              |

| III  | Format Track |            | 0 | 1 | 0 | 1    | 0  | 0              | 0              | 0              |

### 6.1.1 Stepping Rates

$r_3-r_0$  - Stepping Rate

| <b>.</b> |        |       | ·····        |

|----------|--------|-------|--------------|

| +-       | 0000 = | 10uS  | 1000 = 4.0mS |

| Ĺ        | 0001 = | 0.5mS | 1001 = 4.5mS |

| 1        | 0010 = | 1.0mS | 1010 = 5.0mS |

| 1        | 0011 = | 1.5mS | 1011 = 5.5mS |

| 1        | 0100 = | 2.0mS | 1100 = 6.0mS |

| 1        | 0101 = | 2.5mS | 1101 = 6.5mS |

| 1        | 0110 = | 3.0mS | 1110 = 7.0mS |

| Ì        | 0111 = | 3.5mS | 1111 = 7.5ms |

| +-       |        |       | +~~~~~~      |

6.1.2 DMA Read

<u>D - DMA Read Mode</u> 0 = Programmed I/O Mode 1 = DMA Mode

The DMA bit is used to position INTRQ in relation to DRQs during the read sector command. If the DMA bit is reset (D=0), the interrupt will occur before the first DRQ. This allows the programmed I/O host to intervene and transfer the data from the sector buffer. If the DMA bit is set (D=1), then the interrupt will occur only after the system DMA controller has transferred the entire buffer of data.

WD1000 OEM Manual Commands

dde

6.2 Type I Commands

These commands simply position the R/W heads of the selected drive. Both commands have explicit stepping rate fields. The lower four bits of these commands form the stepping rate.

### 6.2.1 Restore

The Restore command is used to calibrate the position of the R/W head on each drive by stepping the head outward until the TROOO line goes true. Upon receipt of the Restore command, the Busy bit in the Status Register is set. Cylinder High and Cylinder Low Registers are cleared. The lower four bits of the command byte are stored in the stepping rate register for subsequent implied seeks. The state of Seek Complete, Ready and Write Fault are sampled, and if an error condition exists, the Aborted command bit in the Error Register is set, the Error bit in the Status Register is set, an interrupt is generated, and the Busy bit is reset.

If no errors are encountered thus far, the internal head position register for the selected drive is cleared. The TROOO line is sampled. If TROOO is true, an interrupt is generated and the Busy bit is reset. If TROOO is not true, stepping pulses at a rate determined by the stepping rate field are issued until the TROOO line is activated. When TROOO is activated, the Busy bit is reset and and interrupt is issued. If the TROOO line is not activated within 1023 stepping pulses, the TROOO Error bit in the Error Register and the Error bit in the Status Register are set, the Busy bit is reset, and an interrupt is issued.

#### 6.2.2 Seek

The Seek command positions the R/W head to a certain cylinder. It is primarily used to start two or more concurrent seeks on drives that support buffered stepping. Upon receipt of the Seek command, the Busy bit in the Status Register is set. The lower four bits of the command byte are stored in the stepping rate register for subsequent implied seeks. The state of Seek Complete, Ready and Write Fault are sampled, and if an error condition exists, the Aborted command bit in the Error Register is set, the Error bit in the Status Register is set, an interrupt is generated, and the Busy bit is reset.

If no errors are encountered thus far, the internal head position register for the selected drive is updated, the direction line is set to the proper direction and a step pulse is issued for each cylinder to be stepped. When all stepping pulses have been issued, the Busy bit is reset and an interrupt is issued. Note that the Seek Complete line is not sampled after the Seek command, allowing multiple seek operations to be started using drives with buffered seek capability. Page 6-4

dde

### 6.3 Type II Commands

This type of command is characterized by a transfer of a block of data from the WD1000 buffer to the host. This command has an implicit stepping rate as set by the last Restore or Seek command.

#### 6.3.1 Read Sector

The Read Sector command is used to read a sector of data from the disk to the host computer. Upon receipt of the Read command, the Busy bit in the Status register is set. The state of Seek Complete, Ready and Write Fault are sampled, and if an error condition exists, the Aborted Command bit in the Error Register is set, the Error bit in the Status Register is set, and a normal completion is simulated.

#### 6.3.1.1 Implied Seek

If no errors are encountered so far, a Seek command is executed. The Seek Complete line is sampled. If the Seek Complete line does not go true within 128 Index pulses, then the Aborted command bit in the Error Register is set, the Error bit in the Status Register is set, and a normal completion is simulated.

### 6.3.1.2 **Retries**

Once the head has settled over the desired cylinder, the WD1000 will attempt to read the sector. The WD1000 performs all retries necessary to recover the data during the read command. The controller attempts to read the desired sector up to 16 times. It will attempt a retry if it does not find an ID, if the ID of that sector has a bad CRC, if the Data Address Mark (DAM) couldn't be found, or even if the data was actually read from the disk but incurred a data CRC error.

#### 6.3.1.3 Auto Restore

Every time the controller encounters an error, it records the occurance of that error in an internal register. If, after 16 retries, the controller was not able to get a match on the ID field, it assumes that the head was possibly mis-positioned and executes an auto-restore. During the auto-restore, the stepping rate is implied to be equal to the Seek Complete period. After the auto-restore has been successfully completed, the controller re-seeks and attempts to read the sector once again. An auto-restore will be performed only once per read or write sector command.

### 6.3.1.4 Hard Errors

If the controller encounters a non-recoverable error, the controller examines its internal error history register. It then sets the bit in the Error Register of the highest severity error incurred. If the Data CRC Error bit is set, the data that last produced that error will be available in the sector buffer. The Error bit in the Status Register is set and a normal completion is simulated. WD1000 OEM Manual Commands Page 6-5

6.3.1.5 Error Severity Levels Although the WD1000 might encounter any number of errors in the course of executing a command, it only reports the most severe error. Errors are ranked from most severe to least severe as follows:

- Aborted Command

TR000 Error

Bad Block \*

Data CRC Error

Data Address Mark Not Found

ID CRC Error

- 7. ID Not Found

- \* Bad block will only be detected if there is no ID CRC Error or ID Not Found Error.

6.3.1.6 Normal Completion If the WD1000 encountered no errors, it is considered a normal completion. The busy bit is reset. The status of the DMA bit in the command byte is examined. If this bit is reset (D=0; programmed I/O mode) then an interrupt is issued at this time. DRQs are then generated for each byte to be read from the buffer. (Note: It is recommended that programmed I/O transfers should take place as a block move without consulting the DRQ bit in the Status Register.) After all the data has been moved from the buffer, the DMA bit in the command byte is consulted again. If this bit is set (D=1; DMA mode) then an interrupt will be issued. Page 6-6

**G**De

## 6.4 Type III Commands

This type of command is characterized by a transfer of a block of data from the host to the WD1000 buffer. These commands have implicit stepping rates as set by the last Restore or Seek command.

#### 6.4.1 Write Sector

The Write Sector command is used to write a sector of data from the host computer to the disk. Upon receipt of the Write command, the controller generates DRQs for each byte to be written to the buffer. (Note: It is recommended that programmed I/O transfers should take place as a block move without consulting the DRQ bit in the Status Register.)

After all data has been sent to the sector buffer, the Busy bit in the Status Register is set. The state of Seek Complete, Ready and Write Fault are sampled, and if an error condition exists, the Aborted command bit in the Error Register is set, the Error bit in the Status Register is set, an Interrupt is generated, and the Busy bit is reset.

#### 6.4.1.1 Implied Seek

If no errors are encountered so far, a Seek command is executed. The Seek Complete line is sampled. If the Seek Complete line doesn't go true within 128 Index pulses, then the Aborted command bit in the Error Register is set, the Error bit in the Status Register is set, an Interrupt is generated and the Busy bit is reset.

#### 6.4.1.2 Retries

Once the head has settled over the desired cylinder, it will attempt to read the ID of the sector. The WD1000 performs all retries necessary to recover the ID during the write command. The controller attempts to read the ID of the desired sector up to 16 times. It will attempt a retry if it doesn't find an ID or if the ID of that sector has a bad CRC.

### 6.4.1.3 Auto Restore

Every time the controller encounters an error, it records the occurrence of that error in an internal register. If, after 16 retries, the controller was not able to get a match on the ID field, it assumes that the head was possibly mis-positioned and executes an auto-restore. During the auto-restore, the stepping rate is implied to be equal to the Seek Complete period. After the auto-restore has been successfully completed, the controller re-seeks and attempts to write the sector once again. WD1000 OEM Manual Commands

|             |  | , . |  |  |

|-------------|--|-----|--|--|

| Hard Errors |  |     |  |  |

If the controller encounters a non-recoverable error, the controller examines its internal error history register. It then sets the bit in the Error Register of the highest severity error incurred. The Error bit in the Status Register is set, an Interrupt is generated and the Busy bit is reset.

If the proper sector is located, the sector buffer is written to the disk, an interrupt is generated and the Busy bit is reset.

Page 6-7

### Page 6-8

WD1000 OEM Manual Commands

**dde**

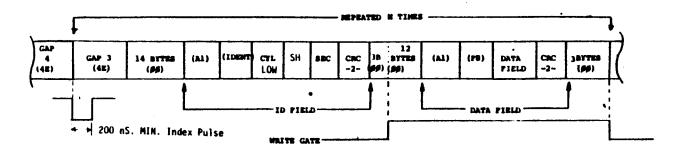

### 6.4.2 Format Track

The Format command is used for initializing the ID and data fields on a particular disk. Upon receipt of the Format command, the controller generates DRQs for each byte of the interleave table to be written to the buffer. Information on setting up an interleave table can be found in Section 7. In all cases, the number of bytes transferred to the buffer must correspond to the current sector size.

After all data has been sent to the buffer, the Busy bit in the Status Register is set. The state of Seek Complete, Ready and Write Fault lines are sampled. If an error condition exists, the Aborted command bit in the Error Register is set, the Error bit in the Status Register is set, an interrupt is generated and the Busy bit is reset.

#### 6.4.2.1 Implied Seek