Programming Training Manual

CONTROL DATA 1604 COMPUTER

| Record of Revisions |                                                    |  |  |  |  |

|---------------------|----------------------------------------------------|--|--|--|--|

| REVISION            | NOTES                                              |  |  |  |  |

| A                   | Minor corrections only; does not obsolete previous |  |  |  |  |

| (11-1-61)           | editions.                                          |  |  |  |  |

|                     |                                                    |  |  |  |  |

|                     |                                                    |  |  |  |  |

|                     |                                                    |  |  |  |  |

|                     |                                                    |  |  |  |  |

|                     |                                                    |  |  |  |  |

|                     |                                                    |  |  |  |  |

|                     |                                                    |  |  |  |  |

|                     |                                                    |  |  |  |  |

|                     |                                                    |  |  |  |  |

|                     |                                                    |  |  |  |  |

|                     |                                                    |  |  |  |  |

|                     |                                                    |  |  |  |  |

|                     |                                                    |  |  |  |  |

|                     |                                                    |  |  |  |  |

|                     |                                                    |  |  |  |  |

|                     |                                                    |  |  |  |  |

|                     |                                                    |  |  |  |  |

|                     |                                                    |  |  |  |  |

|                     |                                                    |  |  |  |  |

Address comments concerning this manual to:

Control Data Corporation

Technical Publications Department

4201 North Lexington Avenue

St. Paul, Minnesota 55112

or use Comment Sheet located in the back of this manual.

# PREFACE

This manual applies to the 1604-C in all respects. It is applicable to the 1604-A and 1604-B except for some details in Input/Output.

# TABLE OF CONTENTS

|                                          | Page |

|------------------------------------------|------|

| Chapter I PRELIMINARY INFORMATION        | 1-1  |

| Introduction                             | 1-1  |

| Basic Peripheral Equipment               | 1-1  |

| Optional Peripheral Equipment            | 1-2  |

| Summary of Characteristics               | 1-2  |

| Internal Storage                         | 1-3  |

| Address System                           | 1-4  |

| 1604 Program Step                        | 1-4  |

| 1604 Instruction Word                    | 1-5  |

| Operational Registers                    | 1-7  |

| Secondary Registers                      | 1-10 |

| CDC 1604 Basic Instruction List          | 1-12 |

| Review Tcst (Chapter I)                  | 1-14 |

| Chapter II FIRST GROUP OF INSTRUCTIONS   | 2-1  |

| First Instructions                       | 2-1  |

| A Right Shift                            | 2-1  |

| A Left Shift                             | 2-1  |

| Q Right Shift                            | 2-2  |

| Q Left Shift                             | 2-2  |

| Load A                                   | 2-6  |

| Load Q                                   | 2-6  |

| Store A                                  | 2-6  |

| Store Q                                  | 2-6  |

| Add                                      | 2-11 |

| Subtract                                 | 2-11 |

| A Jump                                   | 2-11 |

| Q Jump                                   | 2-11 |

| Review Test (Chapter II)                 | 2-18 |

| Chapter III SECOND GROUP OF INSTRUCTIONS | 3-1  |

| Second Group of Instructions             | 3-1  |

| Long Right Shift                         | 3-1  |

| Long Left Shift                          | 3-1  |

| Enter A                                  | 3-2  |

| Enter Q                                  | 3-3  |

| Load A                                   | 3-3  |

| Load Q                                   | 3-3  |

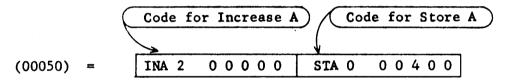

| Increase A                               | 3-10 |

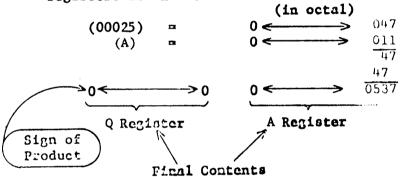

| Multiply Integer                         | 3-11 |

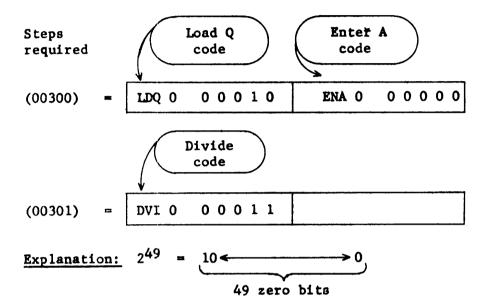

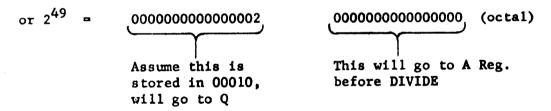

| Divide Integer                           | 3-12 |

| Selective Jump                           | 3-16 |

| Substitute Address (Upper)               | 3-16 |

| Substitute Address (Lower)               | 3-18 |

| Review Test (Chapter III)                | 3-21 |

| Chapter IV           | THIRD GROUP OF INSTRUCTIONS  | 4-1          |

|----------------------|------------------------------|--------------|

| Third Grou           | p of Instructions            | 4-1          |

| Storage              | Skip                         | 4-1<br>4-1   |

| Storage              | Shift                        | 4-2          |

| Index S              | kip                          | 4-2          |

| Index J              |                              | 4-3          |

| Load Lo              |                              | 4-7          |

| Add Log              |                              | 4-7          |

|                      | t Logical                    | 4-7          |

| Store L              |                              | 4-7          |

| Enter I              |                              | 4-12         |

|                      | o Nothing)                   | 4-12         |

| Increase             |                              | 4-12         |

|                      | dex (Upper)                  | 4-12         |

|                      | dex (Lower)                  | 4-13         |

|                      | ndex (Upper)                 | 4-13         |

|                      | ndex (Lower)                 | 4-13         |

| Review Test (        | (Chapter IV)                 | 4-17         |

| Chapter V            | FOURTH GROUP OF INSTRUCTIONS | 5-1          |

|                      |                              | 5-1          |

| Fourth Grou          | p of Instructions            | 5 <b>-</b> 1 |

| Multiply             | Fractional                   | 5-1          |

|                      | ractional                    | 5-2          |

| Selectiv             |                              | 5-3          |

| Selectiv             |                              | 5-4          |

| Selectiv             |                              | <b>5-</b> 5  |

|                      | e Complement                 | 5-5          |

|                      | e Substitute                 | <b>5-</b> 5  |

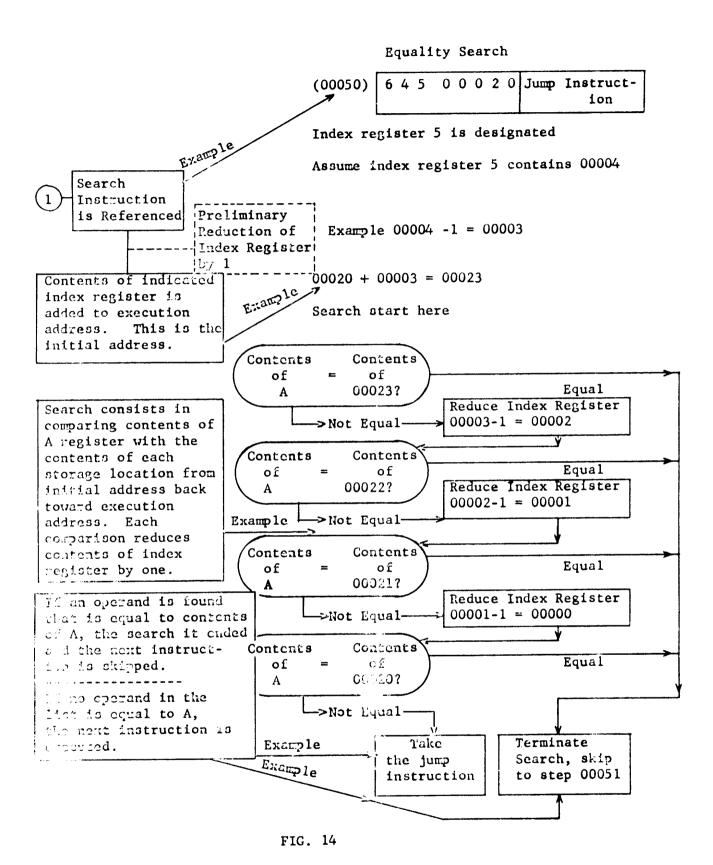

| Equality<br>Threshol |                              | 5-11         |

| Masked E             |                              | 5-13         |

| Masked T             |                              | 5-13         |

| Replace A            |                              | 5-14         |

| Replace S            |                              | 5-21         |

| Replace A            |                              | <b>5-</b> 21 |

|                      | Subtract One                 | 5-21         |

| Review Test (        |                              | 5-21         |

| 1002 (               | Shapter V)                   | 5-26         |

| Chapter VI F         | TIFTH GROUP OF INSTRUCTIONS  | 6-1          |

| Rifth Carr           | of Inghmedian                |              |

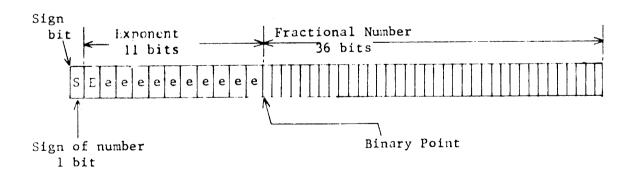

| Floating Poi         | of Instructions              | 6-1          |

| Floating Pol         |                              | 6-1          |

| Floating             |                              | 6-5          |

| Floating             |                              | <b>6-</b> 5  |

| Floating             |                              | 6-5          |

| Scale A              | DIAIGE                       | 6-6          |

| Scale AQ             |                              | 6-7          |

| peare MY             |                              | 6-8          |

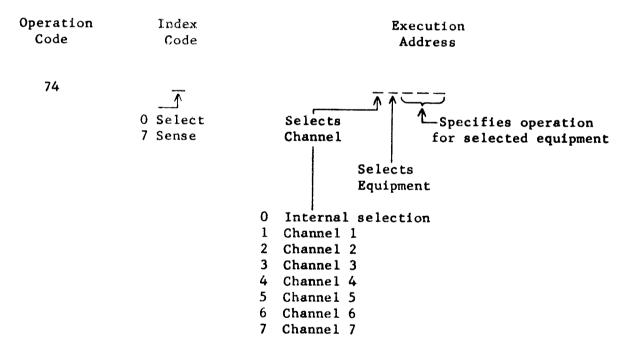

| Cha | PTET VII SIXTH GROUP OF INSTRUCTIONS                                                                | 7-1                             |

|-----|-----------------------------------------------------------------------------------------------------|---------------------------------|

| S   | ixth Group of Instructions External Function Input Transfer Output Transfer External Function Codes | 7-1<br>7-3<br>7-6<br>7-7<br>7-9 |

|     | APPENDIXES                                                                                          |                                 |

| Α.  | Results of Exercises                                                                                | A-1                             |

| В.  | Review Test Answers                                                                                 | B-1                             |

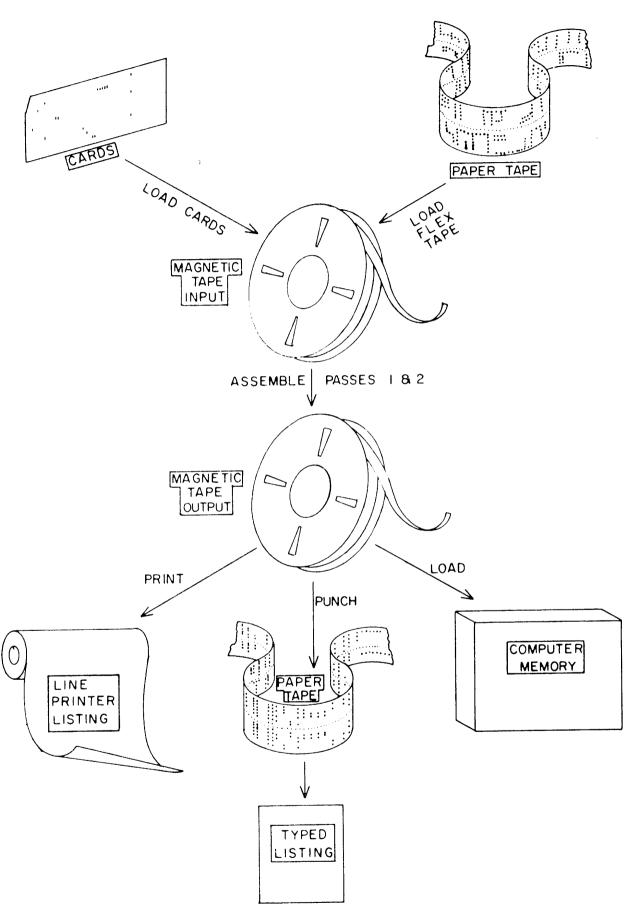

| c.  | 1604 Assembly Program                                                                               | C-1                             |

| D.  | Load and Dump Routines                                                                              | D-1                             |

| Ε.  | Trace Program                                                                                       | E-1                             |

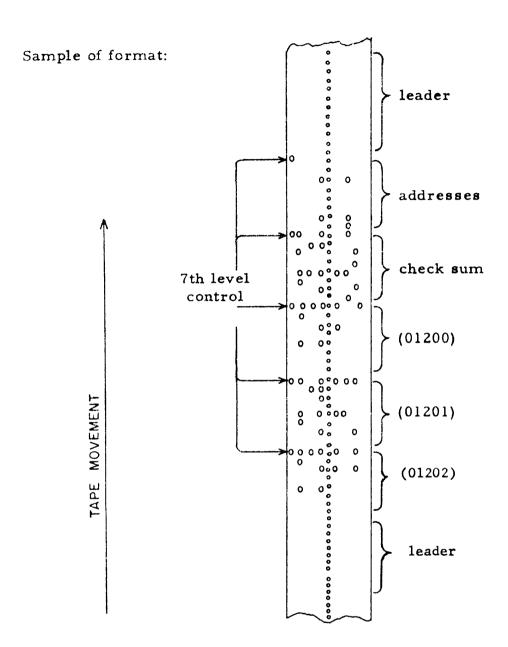

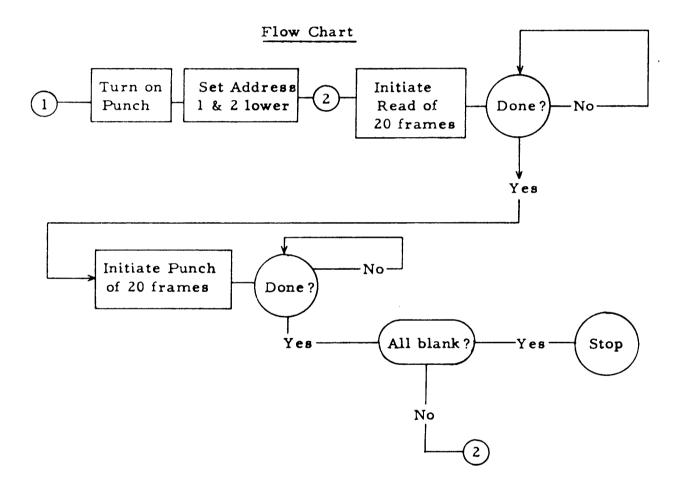

| F.  | Program for Duplicating Punched Tape                                                                | F-1                             |

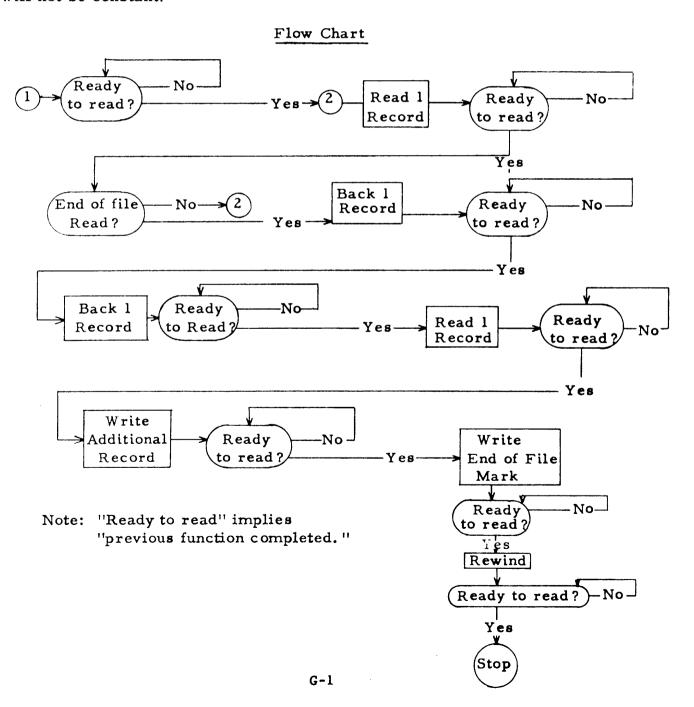

| G.  | Program for Adding One Record to File                                                               | G-1                             |

#### CHAPTER I

#### PRELIMINARY INFORMATION

#### INTRODUCTION

The 1604 is a general-purpose, parallel, digital computer designed for large scale scientific problems or for large-volume data processing. It features the following general characteristics:

- 1. Equipment is low-power, solid-state throughout.

- 2. Physical size is such that it can be used in a semi-permanent office environment.

- 3. Several of the peripheral equipments can communicate directly with computer storage through independent access-channels. This permits reading and writing on magnetic tapes without external buffering devices.

- 4. Internal storage contains two magnetic core units operating together to form a single storage system of 1.6 million bits capacity; storage cycle time is 6.4 microseconds.

- 5. Real time inputs and outputs may be processed with peak rates up to 15 million bits per second.

- 6. Fixed and floating binary point arithmetic operations are possible with an average instruction time of 10 microseconds and a basic addition time of 1.2 microseconds.

- 7. The full use of index registers along with the regular instruction repertoire makes it possible to use almost 500 types of instructions in programming.

# Basic Peripheral Equipment

- a. Magnetic Tape provides the principal input-output medium. Recording on tape is in IBM coded or binary format. One magnetic tape cabinet is provided with the basic unit. Additional cabinets are available optionally.

- b. Paper Tape equipment consists of a Control Data 350 Reader and a Teletype BRPE Punch.

c. Typewriter monitoring information, with keyboard entry, is provided by a modified IBM typewriter.

# Optional Peripheral Equipment

a. A Model 1605 Adaptor converts character information from IBM equipments to 48 bit words. This adaptor communicates directly with 1604 storage through a separate input-output channel. This makes possible the use of the following additional peripheral equipments:

IBM 714 Card Reader

IBM 722 Card Punch

IBM 717 Line Printer

IBM 727 Magnetic Tape Transports

## Summary of Characteristics

General Type -Word Length -Storage -Storage Cycle Time -Instruction Type -Index Registers -Average Instruction Time -Arithmetic Operations -Pasic Add Time -Circuits -Clock -Buffered Communication Channels -Buffer Processing Time -Block Transfer Channels -Block Transfer Time -Power -Minimum Floor Space -

Parallel

48 Bits

32,768 words, two phase core

6.4 microseconds

Single address (two per word)

Six

10 microseconds

Fixed & floating binary point

1.2 microseconds

Transistor-diode, direct-coupled

Two phase, 5 mc rate

Six 48-bit channels

16 microseconds per word

Two 48-bit channels

3.2 microseconds per word

4KW (central computer)

400 sq. ft.

### Internal Storage

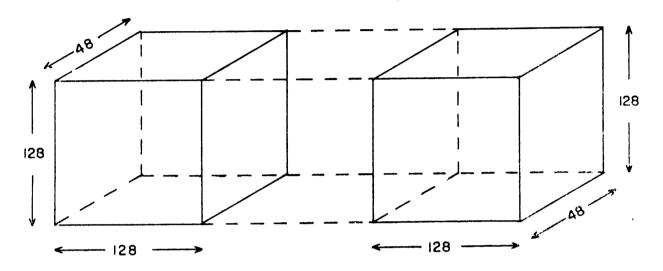

The storage section contains two independent magnetic core storage units each with a capacity of 16,384 words of data 48 bits in length. These units operate together during execution of a program and can be considered as one 32,768 word storage system. FIG. 1 indicates the cores.

FIG. 1

## Two Magnetic Core Units Each 16,384 Words

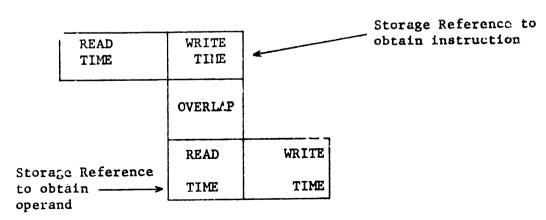

All odd storage addresses reference one of the above units; all even storage addresses reference the other unit. Each unit has a storage cycle time of 6.4 microseconds. Actually the cycles of the two units overlap one another in the execution of a program. For example, if a person thinks of a storage reference consisting of a "read" and "write" time; while one reference is engaged in "writing" the next instruction can be using up the "read" time (see FIG.2). This results in an effective cycle time considerably less than the nominal 6.4 microseconds.

FIG. 2

Overlap of two Storage References

#### Address System

The model 1604 is a single-address computer. This means that each instruction can contain but one address. As previously mentioned, even addresses make one of the core units (16,384 locations) available; odd addresses make the other unit (16,384 locations) available. Thus a total of 32,768 locations are available for addresses. Since 15 bits are set aside for address designation, the total address range (in octal) is

# 00000 to 7777

In this range, addresses 00000, 00002, 00004 - - - 77776 (even) refer to one storage unit; whereas addresses 00001, 00003, 00005 - - - 77777 (odd) refer to the other storage unit.

# Even Addresses Odd Addresses 00000 00002 00004 00005 00001 00003 00005 → Storage Unit 2 77776 77777

Certain storage locations in the memory are used for control and reference functions. These storage locations may be addressed as operands as well as being addressed implicitly by certain control functions. The address assignments for these functions are listed below and will be explained in detail later.

| Special Address                                             | Function or Purpose                                                                                                                                                                                  |

|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00000<br>00001<br>00002<br>00003<br>00004<br>00005<br>00006 | Real Time Clock (1/60 <sup>th</sup> of a second steps) Channel 1 control Channel 2 control Channel 3 control Channel 4 control Channel 5 control Channel 6 control Interrupt program (exit-entrance) |

# 1604 Program Step

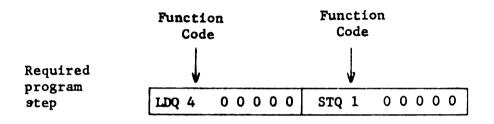

Each program step is a 40-bit word in storage which usually contains two single-address instructions. Each instruction is made up of 24 bits. If a program step contains a single instruction it is necessary that the other instruction be a "do nothing" instruction. This "do-nothing" instruction will be referred to in this manual as the "PASS INSTRUCTION". It has a special code and is described in detail in Chapter IV.

The two instructions in a program step can be considered as logically separate entities in a program sequence. As a practical matter in programming coding, however, the pair is an entity similar to a two-address instruction. The two single address instructions are not separable in the sense that one may not be executed without the other.

FIG. 3 indicates the possibilities of the general composition of a program step.

| 24 Bits<br>Upper Instruction | 24 Bits Lower Instruction |

|------------------------------|---------------------------|

| 24 Bits                      | 24 Bits                   |

| Upper Instruction            | With the Pass Code        |

| 24 Bits                      | 24 Bits                   |

| With the Pass Code           | Lower Instruction         |

FIG. 3

Possible Word Formats

## 1604 Instruction

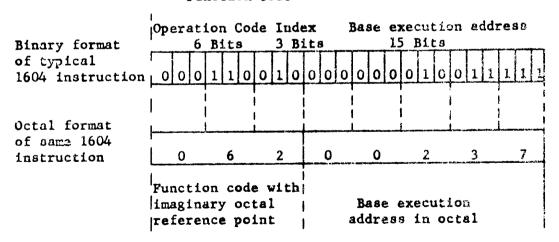

Each instruction is a 24-bit quantity specifying a certain operational entity in the execution of a stored program. The instruction format is shown below in FIG. 4.

#### Function Code

FIG. 4

Binary and Octal Formats of a Typical 1604 Instruction Examining FIG. 4, it can be seen that a 1604 instruction contains 24 bits or 8 octal digits. Of this total, 9 bits or 3 octal digits make up the complete FUNCTION CODE. Actually, the operation code (first 6 bits) determines the specific instruction but there are eight different variations of most instructions, dependent upon the index designator. For this reason, it is probably better for the programmer to think of the complete FUNCTION CODE as containing both an operation code and an index designator (b).

The two operation codes which are not used (00 and 77) are not valid codes but can be used as fault designators which will stop computation and indicate malfunction when interpreted as operation codes.

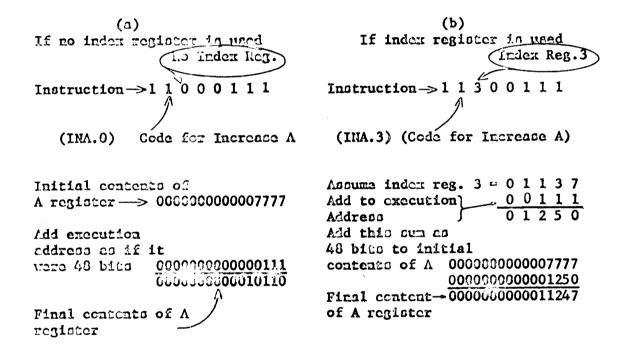

Since index registers play such an important part in programming the 1604, it is necessary to define some of their general characteristics at this time. Six index registers are available for address modification of the base execution address. These index registers are numbered 1 through 6 and are selected by the corresponding octal number (1 through 6) placed in the index designator of the instruction. These index registers perform two different types of functions in the 1604 as defined below.

- 1. As address modifiers, the content of the designated index register is added to the base execution address before the computer interprets the specific instruction. (Addition is modulus 215 minus one, one's complement)

- 2. As jump conditioners.

For programming facility, let us assume the operation code of 6 bits is separated from the index designator by an octal reference point as shown below.

06.0 Each one of these contains the same operation code (06) but a different index 06.1 designator. Each index designator 06.2 designates a different functional operation 06.3 of the basic code (06). For this reason it 06.4 is customary to think of these as eight 06.5 variations of the same instruction or simply 06.6 as eight different instructions. 06.7

The operation code of six bits specifies the general character of the operation to be performed by the instruction. The index designator of three bits completes the function code so that the computer carries out a specific operational procedure. Of the possible 64 operation codes (six bits can hold 64 different codes), the 1604 uses 62 for general instructions. Since there are eight possible index designators (three bits can hold eight different codes 0 to 7), there are approximately 500 (8 x 62) different variations available.

It is important to note that regardless of the particular function they may serve, the use of index registers involves the contents of the index register which is designated except in the case of instructions 22, 23, 74, 75, and 76.

In addition to the codes I through 6, the index designator can also indicate 0 or 7. A zero index designation indicates that no index register is involved. (Exception: In some instructions, a designation of 0 may refer to a certain condition being fulfilled before a jump occurs.) An index designation of 7 will indicate that indirect addressing is to be used except in an instruction where the index designation defines a necessary condition for a jump and in the external function sense condition. (Indirect addressing is a means for expanding the reference capabilities of the instruction execution address. In indirect addressing, the instruction execution address specifies a storage location in which is located the operand address.)

Of particular significance to programmers with respect to the use of index registers is the fact that when the contents of the index register is added to the execution address, the addition is performed in a ones complement accumulator, modulus 215 minus one. Use of index registers along with indirect addressing (for index 7) will be explained in detail for the individual instructions.

## Operational Registers

The operational registers of the 1604 computer are defined as those registers which are capable of storing data from one instruction to another; the contents of those registers are displayed on the control console. These registers do not have special addresses (as is necessary in two or three address logic) but are referenced implicitly by the execution of the different instructions. However, it is important that the programmer know of these registers and of their functional use in the instructions.

Altogether ten different internal registers are available for auxiliary functions. Two of these are arithmetic registers, six are index registers, and two perform control functions. The ten are listed and described below:

| Arithmetic<br>Registers | A Register 48 bits Q Register 48 bits                                                      |

|-------------------------|--------------------------------------------------------------------------------------------|

|                         | Index 1 15 bits Index 2 15 bits Index 3 15 bits                                            |

|                         | Index 2 15 bits                                                                            |

| Index                   | Index 3 15 bits                                                                            |

| Registers               | 7 Index 4 15 bits                                                                          |

|                         | Index 5 15 bits                                                                            |

|                         | Index 5 15 bits Index 6 15 bits                                                            |

| Control Registers       | Program Control Register (U <sup>1</sup> upper)24 bits Program Address Register (P)15 bits |

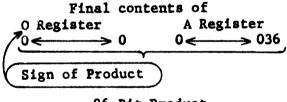

The A register, or accumulator, operates as a 48-bit subtractive accumulator during most of the arithmetic operations. Normal arithmetic operations are performed modulus (2<sup>48</sup>-1). This register also has shifting capabilities which are explained under "shifting".

The Q register assists the A register in performing the more extensive arithmetic operations. For example, multiply, divide, and floating point instructions involve both the A and Q registers. The Q register serves as a "mask" during the logical operations and it also has shifting capabilities which are explained under "Shifting".

On some instructions the A and Q registers operate as one large register. For example, it is possible to shift A and Q as one register of 96 bits.

Six index registers are available for modification of execution addresses. In program loops, two approaches are possible in using these index registers for looping:

- The contents of an index register may be advanced each pass through a loop and the exit is initiated when the contents of the index register attain a given threshold.

- 2. The contents of an index register may be preset to a certain amount and then reduced by one count each pass through the program loop until an exit is initiated upon the index register contents reading zero.

The two control registers are used to control the internal sequencing of instructions. The Program Control Register ( $\mathbf{U}^1$ ) holds the current instruction and interprets this instruction so that the proper execution can begin.

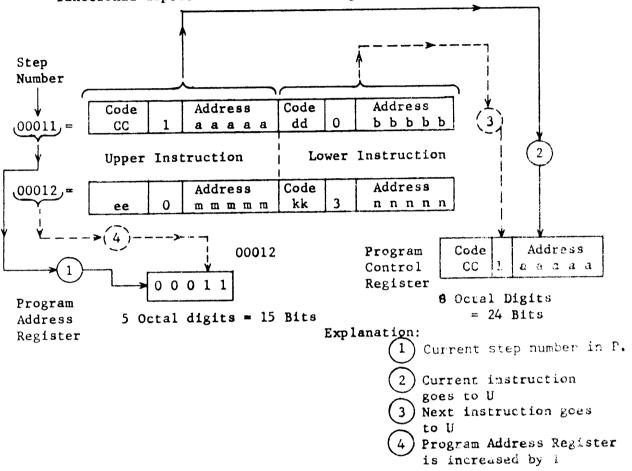

The Program Address Register (P) holds the storage location of the current program step during the interpretation and execution of an instruction contained in that program step. Upon completion of a step in the program, the program address is advanced one count to specify the location of the next step. FIG. 5 indicates the functional aspects of the U and P registers.

FIG. 5

Sequencing of P and U

#### Secondary Registers

In addition to the operational registers there is a group of twelve registers, not displayed on the control console, which also perform a vital function in machine operation. These are the secondary registers. Ordinarily they may be thought of as transfer registers, acting as intermediate storage for computer instructions or operands as they are manipulated during the execution of an instruction. The twelve registers include

| Auxiliary program control register U <sup>2</sup> | •  | • | • | • | 15 | bits |

|---------------------------------------------------|----|---|---|---|----|------|

| Storage address register S <sup>1</sup>           | •  | • | • | • | 14 | bits |

| Storage address register S <sup>2</sup>           | •  | • | • | • | 14 | bits |

| Storage restoration register z1                   | •  | • | • | • | 48 | bits |

| Storage restoration register $z^2$                | •  | • | • | • | 48 | bits |

| Address buffer register R                         | •  | • | • | • | 15 | bits |

| Exchange register X                               | •  | • | • | • | 48 | bits |

| Function register 00                              | •  | • | • | • | 15 | bits |

| Output (four provided) registers 01,2;            | 3, | 4 | • | • | 48 | bits |

The auxiliary program control register, U<sup>2</sup>, is an accumulator used in the modification of the execution address of the current instruction by the addition of the contents of an index register.

The even and odd 16,384 word memory units each has a storage address register,  $S^1$  and  $S^2$  respectively. These registers receive addresses of instructions from the address register, P, and addresses of operands from  $U^2$ .

Each even and odd memory unit also has a storage restoration register,  $Z^1$  and  $Z^2$  respectively, which holds the 48-bit word which is to be written in a given storage location.

The R register acts as an exchange register for transmissions involving the index registers. It is used for advancing or reducing the count in a given index register. During several instructions it is used to count repetitive operations. Floating-point instructions use R in performing arithmetic operations on the exponent or characteristic.

The X register is an exchange and auxiliary arithmetic register. All input and output data pass through the X register.

The external function register,  $0^0$ , is used for exchanging control information with imput-output equipment.

Four output registers,  $0^1$ ,  $0^2$ ,  $0^3$ , and  $0^4$ , are provided.  $0^1$ ,  $0^2$  and  $0^3$  are used for output buffer operations where the data are transmitted at the speed of the input-output equipment. Output register  $0^4$  handles all high-speed output transfer operations where the data are transferred at the internal speed of the computer.

CONTROL DATA MODEL 1604 BASIC INSTRUCTION LIST (omitting the eight possible variations of each instruction due to index designations 0 through 7)

| ZRO                                                                              | 00                                                                         | (not used)                                                                                                                                                            | SST                                                  | 40                                                                   | Selective Set                                                                                                                                                                                        |

|----------------------------------------------------------------------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ARS                                                                              |                                                                            | A Right Shift                                                                                                                                                         | SCL                                                  | 41                                                                   | Selective Clear                                                                                                                                                                                      |

| QRS                                                                              |                                                                            | Q Right Shift                                                                                                                                                         | SCM                                                  | 42                                                                   | Selective Complement                                                                                                                                                                                 |

| LRS                                                                              |                                                                            | Long Right Shift                                                                                                                                                      | SSU                                                  | 43                                                                   | Selective Substitute                                                                                                                                                                                 |

| ENQ                                                                              |                                                                            | Enter Q                                                                                                                                                               | LDL                                                  | 44                                                                   | Load Logical                                                                                                                                                                                         |

| ALS                                                                              |                                                                            | A Left Shift                                                                                                                                                          | ADL                                                  | 45                                                                   | Add Logical                                                                                                                                                                                          |

| QLS                                                                              |                                                                            | Q Left Shift                                                                                                                                                          | SBL                                                  | 46                                                                   | Subtract Logical                                                                                                                                                                                     |

| LLS                                                                              |                                                                            | Long Left Shift                                                                                                                                                       | STL                                                  | 47                                                                   | Store Logical                                                                                                                                                                                        |

|                                                                                  | •                                                                          |                                                                                                                                                                       |                                                      |                                                                      | _                                                                                                                                                                                                    |

| ENA                                                                              | 10                                                                         | Enter A                                                                                                                                                               | ENI                                                  | 50                                                                   | Enter Index                                                                                                                                                                                          |

| INA                                                                              |                                                                            | Increase A                                                                                                                                                            | INI                                                  | 51                                                                   | Increase Index                                                                                                                                                                                       |

| LDA                                                                              |                                                                            | Load A                                                                                                                                                                | LIU                                                  | 52                                                                   | Load Index (upper)                                                                                                                                                                                   |

| LAC                                                                              |                                                                            | Load A, Complement                                                                                                                                                    | LIL                                                  | 53                                                                   | Load Index (lower)                                                                                                                                                                                   |

| ADD                                                                              |                                                                            | AĞU                                                                                                                                                                   | ISK                                                  | 54                                                                   | Index Skip                                                                                                                                                                                           |

| SUB                                                                              |                                                                            | Subtract                                                                                                                                                              | IJP                                                  | 55                                                                   | Index Jump                                                                                                                                                                                           |

|                                                                                  |                                                                            | Load Q                                                                                                                                                                | SIU                                                  | 56                                                                   | Store Index (upper)                                                                                                                                                                                  |

| LQC                                                                              |                                                                            | Load Q, Complement                                                                                                                                                    | SIL                                                  | 57                                                                   | Store Index (lower)                                                                                                                                                                                  |

| _,,                                                                              | -•                                                                         | _                                                                                                                                                                     |                                                      |                                                                      |                                                                                                                                                                                                      |

| STA                                                                              | 20                                                                         | Store A                                                                                                                                                               | SAU                                                  | 60                                                                   | Substitute Address (upper)                                                                                                                                                                           |

| STQ                                                                              |                                                                            | Store Q                                                                                                                                                               | SAL                                                  | 61                                                                   | Substitute Address (lower)                                                                                                                                                                           |

|                                                                                  | 41                                                                         |                                                                                                                                                                       |                                                      |                                                                      |                                                                                                                                                                                                      |

|                                                                                  |                                                                            | •                                                                                                                                                                     | INT                                                  | 62                                                                   | Input Transfer                                                                                                                                                                                       |

| AJP                                                                              | 22                                                                         | A Jump                                                                                                                                                                |                                                      | 62<br>63                                                             | Input Transfer<br>Output Transfer                                                                                                                                                                    |

| AJP<br>QJP                                                                       | 22<br>23                                                                   | A Jump<br>Q Jump                                                                                                                                                      | INT                                                  |                                                                      |                                                                                                                                                                                                      |

| AJP<br>QJP<br>MUI                                                                | 22<br>23<br>24                                                             | A Jump                                                                                                                                                                | INT<br>OUT                                           | 63                                                                   | Output Transfer                                                                                                                                                                                      |

| AJP<br>QJP<br>MUI<br>DVI                                                         | 22<br>23<br>24<br>25                                                       | A Jump<br>Q Jump<br>Multiply Integer<br>Divide Integer                                                                                                                | INT<br>OUT<br>EQS<br>THS                             | 63<br>64                                                             | Output Transfer<br>Equality Search                                                                                                                                                                   |

| AJP<br>QJP<br>MUI                                                                | 22<br>23<br>24<br>25<br>26                                                 | A Jump<br>Q Jump<br>Multiply Integer                                                                                                                                  | INT<br>OUT<br>EQS<br>THS                             | 63<br>64<br>65                                                       | Output Transfer<br>Equality Search<br>Threshold Search                                                                                                                                               |

| AJP<br>QJP<br>MUI<br>DVI<br>MUF                                                  | 22<br>23<br>24<br>25<br>26                                                 | A Jump<br>Q Jump<br>Multiply Integer<br>Divide Integer<br>Multiply Fractional                                                                                         | INT<br>OUT<br>EQS<br>THS<br>MEQ                      | 63<br>64<br>65<br>66                                                 | Output Transfer Equality Search Threshold Search Masked Equality                                                                                                                                     |

| AJP<br>QJP<br>MUI<br>DVI<br>MUF                                                  | 22<br>23<br>24<br>25<br>26<br>27                                           | A Jump<br>Q Jump<br>Multiply Integer<br>Divide Integer<br>Multiply Fractional                                                                                         | INT<br>OUT<br>EQS<br>THS<br>MEQ                      | 63<br>64<br>65<br>66<br>67                                           | Output Transfer Equality Search Threshold Search Masked Equality Masked Threshold Replace Add                                                                                                        |

| AJP<br>QJP<br>MUI<br>DVI<br>MUF<br>DVF                                           | 22<br>23<br>24<br>25<br>26<br>27                                           | A Jump Q Jump Multiply Integer Divide Integer Multiply Fractional Divide Fractional                                                                                   | OUT<br>EQS<br>THS<br>MEQ<br>MTH                      | 63<br>64<br>65<br>66<br>67<br>70<br>71                               | Output Transfer Equality Search Threshold Search Masked Equality Masked Threshold Replace Add Replace Subtract                                                                                       |

| AJP<br>QJP<br>MUI<br>DVI<br>MUF<br>DVF                                           | 22<br>23<br>24<br>25<br>26<br>27<br>30<br>31                               | A Jump Q Jump Multiply Integer Divide Integer Multiply Fractional Divide Fractional Floating Add                                                                      | INT<br>OUT<br>EQS<br>THS<br>MEQ<br>MTH               | 63<br>64<br>65<br>66<br>67                                           | Output Transfer Equality Search Threshold Search Masked Equality Masked Threshold Replace Add Replace Subtract Replace Add One                                                                       |

| AJP<br>QJP<br>MUI<br>DVI<br>MUF<br>DVF<br>FAD<br>FSB<br>FMU                      | 22<br>23<br>24<br>25<br>26<br>27<br>30<br>31                               | A Jump Q Jump Multiply Integer Divide Integer Multiply Fractional Divide Fractional Floating Add Floating Subtract                                                    | INT<br>OUT<br>EQS<br>THS<br>MEQ<br>MTH<br>RAD<br>RSB | 63<br>64<br>65<br>66<br>67<br>70<br>71<br>72<br>73                   | Output Transfer Equality Search Threshold Search Masked Equality Masked Threshold  Replace Add Replace Subtract Replace Add One Replace Subtract One                                                 |

| AJP<br>QJP<br>MUI<br>DVI<br>MUF<br>DVF<br>FAD<br>FSB<br>FMU<br>FDV               | 22<br>23<br>24<br>25<br>26<br>27<br>30<br>31<br>32                         | A Jump Q Jump Multiply Integer Divide Integer Multiply Fractional Divide Fractional Floating Add Floating Subtract Floating Multiply                                  | INT OUT EQS THS MEQ MTH RAD RSB RAO                  | 63<br>64<br>65<br>66<br>67<br>70<br>71<br>72<br>73<br>74             | Output Transfer Equality Search Threshold Search Masked Equality Masked Threshold  Replace Add Replace Subtract Replace Add One Replace Subtract One External Function                               |

| AJP<br>QJP<br>MUI<br>DVI<br>MUF<br>DVF<br>FAD<br>FSB<br>FMU<br>FDV<br>SCA        | 22<br>23<br>24<br>25<br>26<br>27<br>30<br>31<br>32<br>33                   | A Jump Q Jump Multiply Integer Divide Integer Multiply Fractional Divide Fractional Floating Add Floating Subtract Floating Multiply Floating Divide                  | INT OUT EQS THS MEQ MTH RAD RSB RAO RSO              | 63<br>64<br>65<br>66<br>67<br>70<br>71<br>72<br>73<br>74<br>75       | Output Transfer Equality Search Threshold Search Masked Equality Masked Threshold  Replace Add Replace Subtract Replace Subtract Replace Subtract One External Function Selective Jump               |

| AJP<br>QJP<br>MUI<br>DVI<br>MUF<br>DVF<br>FAD<br>FSB<br>FMU<br>FDV<br>SCA<br>SCQ | 22<br>23<br>24<br>25<br>26<br>27<br>30<br>31<br>32<br>33<br>34             | A Jump Q Jump Multiply Integer Divide Integer Multiply Fractional Divide Fractional Floating Add Floating Subtract Floating Multiply Floating Divide Scale A          | INT OUT EQS THS MEQ MTH RAD RSB RAO RSO EXF          | 63<br>64<br>65<br>66<br>67<br>70<br>71<br>72<br>73<br>74<br>75<br>76 | Output Transfer Equality Search Threshold Search Masked Equality Masked Threshold  Replace Add Replace Subtract Replace Add One Replace Subtract One External Function Selective Jump Selective Stop |

| AJP<br>QJP<br>MUI<br>DVI<br>MUF<br>DVF<br>FAD<br>FSB<br>FMU<br>FDV<br>SCA<br>SCQ | 22<br>23<br>24<br>25<br>26<br>27<br>30<br>31<br>32<br>33<br>34<br>35<br>36 | A Jump Q Jump Multiply Integer Divide Integer Multiply Fractional Divide Fractional Floating Add Floating Subtract Floating Multiply Floating Divide Scale A Scale AQ | INT OUT EQS THS MEQ MTH RAD RSB RAO RSO EXF SLJ      | 63<br>64<br>65<br>66<br>67<br>70<br>71<br>72<br>73<br>74<br>75       | Output Transfer Equality Search Threshold Search Masked Equality Masked Threshold  Replace Add Replace Subtract Replace Subtract Replace Subtract One External Function Selective Jump               |

Instructions are probably easier to learn if a few at one time are mastered along with an opportunity to use these in various short examples. This manual will follow this philosophy in the pages which follow. In addition, all floating-point instructions will be described under the chapter dealing with this topic (see Chapter on Floating Point).

It is also important to note that instructions will be presented with mnemonic codes as well as numeric codes. The mnemonic codes are for the convenience of the programmer and grast be converted to the numeric codes when the final draft of a program is written.

Following each set of instructions, examples and exercises are presented and at the end of each chapter a general review test in presented. Solutions to these exercises and tests are present in the appendixes.

# CHAPTER I Review Test

The following questions review the preliminary information presented in this chapter. Write the answers in the space provided and then check your solutions with those presented in Appendix B.

|                  | y bits does each internal storage location                      |                 |

|------------------|-----------------------------------------------------------------|-----------------|

|                  | the total number of internal storage lo                         |                 |

| The mod          | el 1604 computer is a two-address machine                       | e. (True-False  |

| What is          | the total range of addresses available                          | for programmin  |

| Sketch<br>number | a 1604 instruction, showing the importan of bits for each part. | t parts and the |

|                  | of pits for each part.                                          |                 |

|                  |                                                                 |                 |

| Describ          |                                                                 | a steps.        |

| Describ          | e or sketch the possible types of progra                        | a steps.        |

| Describ          | e or sketch the possible types of progra                        | a steps.        |

| Tastruc compute  | e or sketch the possible types of progra                        | r input to the  |

| 10. | How many index registers are available?                                                                                     |

|-----|-----------------------------------------------------------------------------------------------------------------------------|

| 11. | Name two operational registers other than the index registers.                                                              |

| 12. | Which register holds the address only of the current instruction?                                                           |

| 13. | Which register holds the current instruction?                                                                               |

| 14. | Which registers have shifting capabilities?                                                                                 |

| 15. | Are floating-point instructions available? (Yes or No)                                                                      |

| 16. | Without considering the variations possible through index register designations, how many basic instructions are available? |

| 17. | What is the approximate minimum floor space required for the standard 1604 installation?                                    |

| 18. | What are the standard input-output peripheral equipments used by the computer?                                              |

|     |                                                                                                                             |

| 19. | Since the computer contains transistors instead of electronic tubes, the power requirements are less. (True-False)          |

| 20. | In some instructions it is possible to operate on 96 bits as though they made up the contents of one register. (True-False) |

#### CHAPTER II

# FIRST GROUP OF INSTRUCTIONS

FIRST INSTRUCTIONS (With Mnemonic and Numeric Codes) (where "b" represents the index designator which can be any number 0 through 7)

| A RIGHT SHIFT A LEFT SHIFT Q RIGHT SHIFT Q LEFT SHIFT LOAD A LOAD Q | (ALS.b)<br>(QRS.b) | (01.b)<br>(05.b)<br>(02.b)<br>(06.b)<br>(12.b)<br>(16.b) | STORE A STORE Q ADD SUBTRACT A JUMP Q JUMP | (STA.b)<br>(STO.b)<br>(ADD.b)<br>(SUB.b)<br>(AJP.b)<br>(OJP.b) | (20.b)<br>(21.b)<br>(14.b)<br>(15.b)<br>(22.b)<br>(23.b) |

|---------------------------------------------------------------------|--------------------|----------------------------------------------------------|--------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------|

|---------------------------------------------------------------------|--------------------|----------------------------------------------------------|--------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------|

The first four instructions are SHIFT instructions. These are not the only shift instructions - others will be described later. On the 1604 both end-around and end-off shifts are available. The term end-around indicates a shift in one direction (left on 1604) with bits coming out of one end of the register (left end) and being carried around to the other end (right) of the same register. No bits are discarded in an end-around shift. End-off shifts are shifts in one direction (right on 1604) with the bits being discarded as they come off one end (right) of the register. On the 1604 computer LEFT SHIFTS are end-around; RIGHT SHIFTS are end-off.

# A RIGHT (ARSb) (01.b) (where b may be 0 through 7)

This instruction shifts the contents of the A register to the right the prescribed number of bit positions indicated by the sum of the execution address and the contents of the index register designated. The sign bit is extended (repeated) as the bits shift right. The lowest order bits are discarded as they are shifted out of the register. Shift counts greater than 127 (decimal) are treated as shift faults which may be sensed by the external function instruction. Shift faults do not stop the computer.

# A LEFT (ALSb) (05.b) (where b may be 0 through 7)

This instruction shifts the contents of the A register circularly end-around to the left the prescribed number of bit positions indicated by the sum of the execution address and the contents of the index register designated. The lowest order bit positions, being vacated, are filled by the highest order bits as the shifting proceeds. No bits are discarded; those shifting out of the left end of the register are carried around to the right end. Shift counts greater than 127 (decimal) are shift faults which may be sensed by the external function instruction.

# Q RIGHT (QRSb) (02.b) (where b may be 0 through 7)

This instruction shifts the contents of the Q register "end-off" to the right the prescribed number of bit positions indicated by the sum of the execution address and the contents of the index register designated. The sign bit is extended (to the right) as the bits shift right. Low order bits being shifted out of the register are discarded. A maximum shift count of 127 (decimal) results in a shift fault which may be sensed by the external function instruction.

# Q LEFT (QLSb) (06.b) (where b may be 0 through 7)

This instruction shifts the contents of the Q register circularly "end-around" to the left the prescribed number of bit positions indicated by the sum of the execution address and the contents of the index register designated. The lowest order bit positions (being vacated) are filled with the higher order bits as the shifting proceeds. No bits are discarded - those shifting out of the left end of the register are carried around to the right end. Shift counts greater than 127 (decimal) cause a shift fault which may be sensed by the external function instruction.

The following examples should facilitate learning these four shift instructions. (Each student is advised to work out the examples and check the given solutions.)

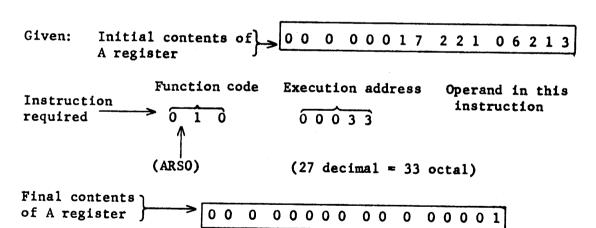

EXAMPLE I. Assume the A register contains the octal quantity shown below. Show the instruction and the final octal contents of the A register after shifting 27<sub>10</sub> bit positions to the right.

Explanation: A shift of 27 bit positions is equivalent to 9 octal places since 3 shifts (3 bits) equals 1 octal position. Since right shifts are "end-off", the 9 low order octal digits are discarded and the sign bits (in this case zeros) are extended. Also note that the index register designated in the above instruction is zero. Any combination of execution address and contents of index register whose sum is 33 (octal) would be correct. For example, an alternative solution to the above instruction might be 0 1 6 0 0 0 3 1 where Index Register 6 contains 0 0 0 0 2.

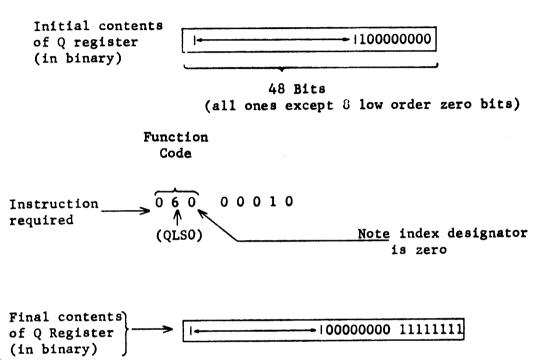

EXAMPLE 2. Assume a programmer wants to shift the initial contents of the Q register (given below in binary form) right  $40_{10}$  bit positions without discarding any of the given bits. Show the instruction needed and the final contents of the Q register after shifting.

#### Given:

Explanation: Since no bits are to be discarded, a left shift instruction is required. However, the programmer wishes to shift right. Fortunately, for every desired right end-around shift there is an equivalent left end-around shift. The rule is to subtract the desired right shifts from 48 and the result is the equivalent number of left shifts. In this case 48-40=8. Then a left end-around of  $8_{10}$  bit position gives the desires result. (3 decimal = 10 octal)

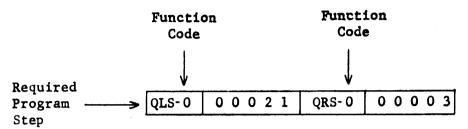

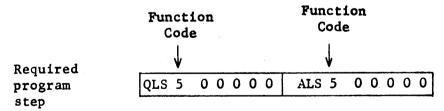

EXAMPLE 3. A programmer wishes to shift the contents of the Q register 17<sub>10</sub> bit positions left, end-around, and then shift the resulting Q register contents 3 places right, end-off. Show the program step in octal to do this.

Explanation: The left shift instruction is programmed on the left side of the word since the left shift is desired first. The right shift instruction then follows on the right side of the word. Seventeen (decimal) = 21 (octal). Also note that other combinations could be used if the index designations are not zero. For example, an alternative solution might appear as:

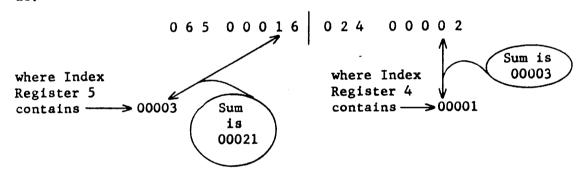

EXAMPLE 4. A count is being generated in index register 5. At certain times within the program it is necessary to shift both the Q and A register left by the count in this index register. Show the program step which will do this.

Explanation: Since the number of bit positions to be shifted is contained in index register 5, the index designator above becomes 5 and the execution address portion is zero. Thus the sum of the execution address and the contents of the index register is equivalent to the contents of the index register.

The following exercises are provided for practice on the four shift instructions presented on the previous pages. Work out the required solutions and check the answers against those shown in Appendix A. The number of correct answers will indicate the approximate mastery of these instructions by cross checking the Rating Table below.

# Rating Table 1

If you have 4 or 5 correct answers . . . . . . Excellent

If you have 3 correct answers . . . . . . . . . . . . Good

If you have 1 or 2 correct answers . . . . . . . . . . . Fair (Review)

If you have 0 correct answers . . . . . . . . . . . . Poor (Restart)

#### EXERCISE 1.

- a. Write a 1604 instruction to shift Q  $14_{10}$  bit positions right.

- b. The A register contains 0 0 0 0 2 1 7 0 0 0 0 0 1 1 0 0. After shifting  $\Lambda$  left end-around 22<sub>10</sub> bit positions, what will A contain? (Show answer in octal format.)

- c. Write a program step which will first shift Q right 7 bits and then shift the new result in Q left by 12<sub>10</sub> bit positions.

- d. Write a 1604 instruction to shift A right by 5 bits without discarding any bits.

- e. Would a right end off shift of 6 bits equal a left end-around shift of 42<sub>10</sub> bit positions? Explain.

With a single address computer transferring data from one storage location to another is usually accomplished by loading a particular register and storing the contents of this register somewhere else. The next four instructions indicate the basic transfer instructions on the model 1604 computer. More powerful transfer instructions will be presented later.

LOAD A (LDA.b) (12.b) (where b may be 0 through 7)

This instruction replaces the A register contents with an operand whose location is specified by the sum of the execution address and the contents of the designated index register. A storage reference is made to obtain the 48-bit quantity at the location indicated by the sum of the execution address, and the contents of the designated index register. A is cleared, the 48-bit quantity is then loaded into the A register. The memory location remains unchanged.

LOAD Q (LDQ.b) (16.b) (where b may by 0 through 7)

This instruction replaces the Q register contents with an operand whose location is specified by the sum of the execution address and the contents of the designated index register. A storage reference is made to obtain the 48-bit quantity indicated by the sum of the execution address and the contents of the designated index register. Q is cleared, the 48-bit quantity is then loaded into the Q register. The memory location remains unchanged.

STORE A (STA.b) (20.b) (where b may be 0 through 7)

This instruction stores the contents of the A register at the storage location specified by the sum of the execution address and the contents of the designated index register. The A register contents are not modified by this instruction - that is, A still holds its initial contents upon the completion of the instruction.

STORE Q (STO.b) (21.b) (where b may be 0 through 7)

This instruction stores the contents of the Q register at the storage location specified by the sum of the execution address and the contents of the designated index register. The Q register contents are not modified by this instruction - that is, Q still holds its initial contents upon the completion of the instruction.

The following examples should facilitate learning these basic transfer instructions. (Each student is advised to work out the examples and check the given solutions.)

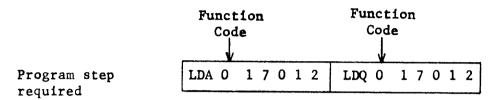

EXAMPLE 5. Assume zeros are contained at storage location 17012. Show the program step which will load these zeros into the A and Q registers.

Explanation: In each instruction above, the computer will reference the storage (17012) given in the execution address and load the contents of 17012 into the A or Q register depending upon the Code 12 or 16. Note that the index designators are zeros above. This is not a necessary condition. An index designation other than zero is satisfactory if the contents of the designated index register plus the execution address equals 17012 above. For example, 12 3 17000 is equivalent to the left instruction above if the contents of index register 3 are 00012.

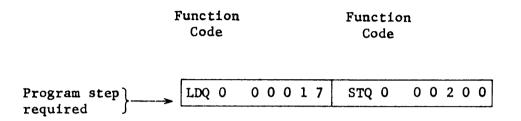

EXAMPLE 6. At storage location 00017 is the constant 1. The programmer desires to transfer this constant to storage location 00200. He does not want to disturb the present contents of the A register. Show the program step which will do this.

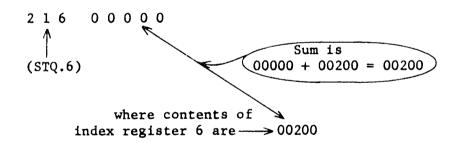

Explanation: The upper instruction loads the contents of 00017 into the Q register. The lower instruction then stores the contents of Q (which now contains the contents of 00017) into 00200, completing the transfer. Note the index designators are both zero. This is not a necessary condition. For example, if index register 6 contains 00200, the lower instruction above could be:

EXAMPLE 7. An address is being generated in index register 4. Another address is being generated at index register 1. A programmer wants to store the contents of the generated address of index register 4 in the generated address of index register 1. He does not want to disturb the A register while doing this. Show the program step required.

Explanation: Since A is not to be disturbed, the Q register instructions are used. The upper instruction loads Q with the contents of the generated address of index register 4. The lower instruction then stores the contents of Q into the generated address which is the contents of index register 1.

Did the contents of index registers 4 and 1 change because of this program step? What did change?

The following exercises are provided for practice on the four basic transfer instructions presented in this chapter. Work out the solutions and check the answers against those in Appendix A. The following Table indicates your approximate progress in learning to program these instructions.

# Rating Table 2

#### EXERCISES 2.

- a. Given, index register 3 contains 00005. What will the instruction, 12300010 accomplish?

- b. Write a program step which will transfer the contents of storage location 01000 to location 01001 without disturbing the A register.

- c. Index register 2 contains 77767.

What will instruction 20200020 accomplish?

- d. What is the difference in effect upon the initial contents of A or Q when LOAD and STORE instructions are programmed?

The last four instructions of this chapter include two arithmetic and two jumps. The arithmetics are the basic ADD and SUBTRACT instructions. The jumps are the A-JUMP and Q-JUMP instructions. Several other instructions similar to both these types are available in the 1604 instruction repertoire. These will be presented in later chapters.

### ADD (ADDb) (14.b) (where b may be any number 0 through 7)

This instruction adds a 48-bit operand to the previous contents of the A register. A storage reference is made to obtain the 48 bit quantity at the location specified by the sum of the execution address and the contents of the designated index register. The operand at this location is then added to the previous contents of the A register. An overflow fault results when the sum of two quantities exceeds the capacity of A.

#### SUBTRACT (SUBb) (15.b) (where b may be any number 0 through 7)

This instruction subtracts a 48-bit operand from the previous contents of the A register. A storage reference is made to obtain the 48-bit quantity at the location specified by the sum of the execution address and the contents of the designated index register. The operand at this location is then subtracted from the previous contents of the A register. An overflow fault results when the difference of two quantities exceeds the capacity of A.

#### A-JUMP (AJPb) (22.b) (where b may be any number 0 through 7)

This is the first instruction, to this point, in which the index registers are not used to modify the execution address. In this instruction, the 3-bit index register designator specifies the particular condition of the A register which will cause a jump in the program address. The conditions for the different possible index designations are as follows:

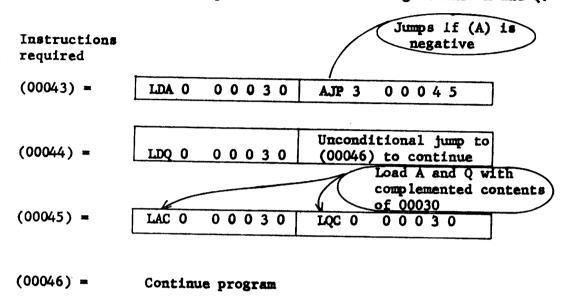

#### If Index register designation is:

- O Jump will occur if content of A is zero

- 1 Jump will occur if content of A is not zero

- 2 Jump will occur if content of A is positive

- 3 Jump will occur if content of A is negative

- 4 Return Jump will occur if content of A is zero

- 5 Return Jump will occur if content of A is not zero

- 6 Return Jump will occur if content of A is positive

- 7 Return Jump will occur if content of A is negative

#### Q-JUMP (QJPb) (23.b) (where b may be any number 0 through 7)

This is the same as the A-Jump except the jump occurs if the Q register is in a certain condition. The index register designator specifies the condition which will cause the jump. The various index designations with the corresponding conditions are listed below:

## If the Index register designation is:

- O Jump occurs if Q register content is zero

- 1 Jump occurs if Q register content is not zero

- 2 Jump occurs if Q register content is positive

- 3 Jump occurs if Q register content is negative

- 4 Return Jump occurs if Q register content is zero

- 5 Return Jump occurs if Q register content is not zero

- 6 Return Jump occurs if Q register content is positive

- 7 Return Jump occurs if Q register content is negative

Before trying examples of these last four instructions, some of the general characteristics of jump instructions should be considered. A jump instruction causes the termination of a current program sequence and the initiation of a new sequence at a different location in storage. The program address register (P) provides the continuity between program steps. This register always contains the storage location of the program step currently being executed. Normally, the address in this register is increased by one count at the end of each program step in order to indicate to the machine the location of the next step. When a jump instruction is given, the program address register is cleared, and a new address is entered from the jump instruction. In all jump instructions the base execution address specifies the beginning address of the new program sequence.

Some of the jump instructions are conditional upon a register containing a specific value or upon the position of an operator key on the console. If the criterion is satisfied, the jump takes place to the location specified by the execution address. If the criterion is not satisfied, the program proceeds in its regular sequential order to the next instruction.

A jump instruction may appear in either position in a program step. If the jump instruction appears in the first (upper) part of the program step, and the jump is taken, the second (lower) part of that program step is never executed. If the jump instruction appears in the second (lower) part of the program step, the first (upper) part of that step is executed in the normal manner.

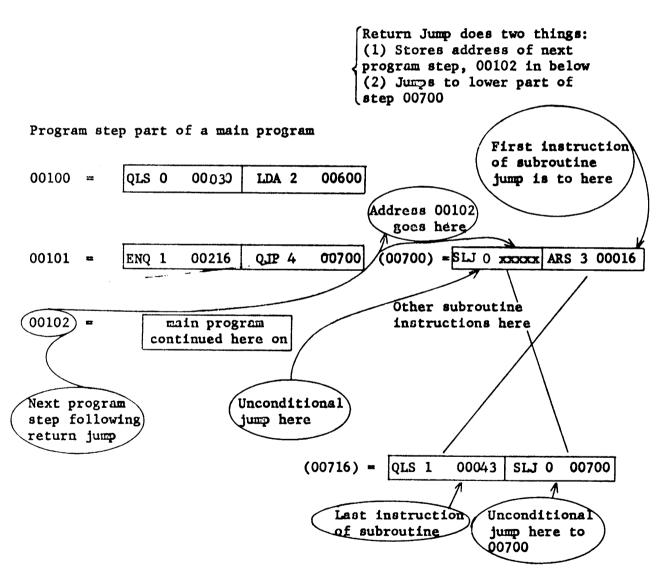

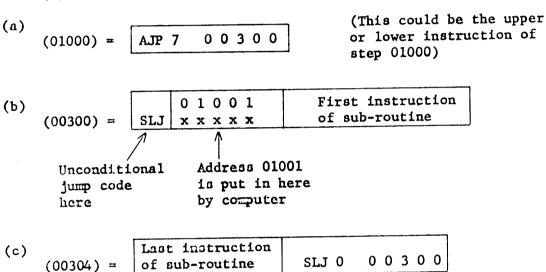

Return Jumps are different from normal jumps in that provision is made to "return" to the location following the place where the return jump was initiated. This operation is important in programming since one often wishes to exit from the main program to some routine and then return to continue the main program. In all such situations there must be some way for the computer to "remember" where the Return Jump originated.

On the 1604, a return jump begins a new program sequence at the second (lower) part of the program step to which the jump is made; that is, the jump is always to the lower part of the program step specified in the Return Jump instruction. At the same time the base execution address in the upper part of this same program step is replaced with the address of the location of the return jump instruction plus one. This allows the new program sequence to return to the step following the return jump instruction and resume the original program at a later time. FIG. 6 indicates the return jump sequence.

FIG. 6

Return Jump Operation

The following examples are provided to afford practice on the last four instructions of this Chapter (Add, Subtract, A-Jump, and Q-Jump). (Each student is advised to work out the examples and check the given solutions.)

EXAMPLE 8. Assume the initial contents of the A register are 000 00000 021 00600.

A programmer wishes to add the contents of storage location 00200 to the contents of A. Show the instruction required if (a) no index register is to be used (b) if index register 3 (which holds 00171) is to be used.

(a) (b)

Instruction required ADD 0 0 0 2 0 0 required ADD 3 0 0 0 0 7

Explanation: (a) One uses the ADD instruction (code 14.x) with the index designation equal to zero. This adds the contents of the location specified by the execution address (00200) to the A register as the problem required.

- (b) If an index register is used the contents of this designated index register is added to the base execution address and this sum specifies the location of the operand which is to be added to the A register. In this case since the sum must be 00200, and since index register 3 contains 00171, it is necessary to make the execution address be 00007. (00007 + 00171 = 00200 .)

- EXAMPLE 9. Assume the A register contains 203 00600 060 00400. Assume address 00300 contains 000 00000 020 00300. After the completion of instruction 150 00300 show the contents of (a) the A register (b) storage location 00300.

- (a) The given instruction subtracts the contents of 00300 from the initial contents of the A register as shown below:

(b) Final contents of 00300 is 000 00000 020 00300.

Explanation: (a) The A register is changed during the execution of the instruction since the arithmetic process (subtraction) takes place and the result (the difference) is left there.

(b) The subtraction does not change the quantity being subtracted from the A register. Thus the final contents of address 00300 is the same as its initial contents.

EXAMPLE 10. A programmer is generating a quantity in the Q register. At program step 00100, he wants to test the contents of Q for two conditions: (1) if the content of Q is zero, he wishes to jump to step 00600, and (2) if the content of Q is negative, he wishes to jump to step 00700. Show the instructions required to do this.

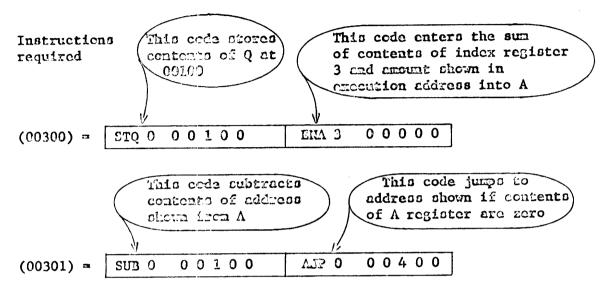

Instructions required

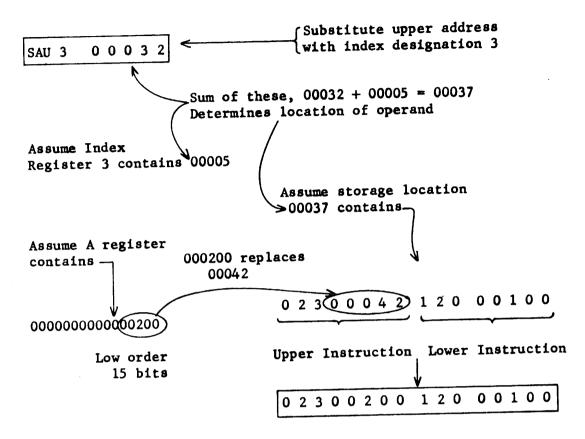

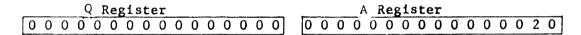

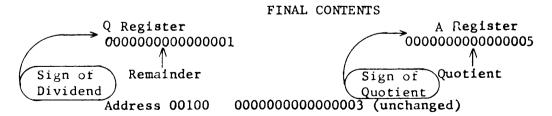

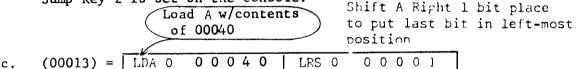

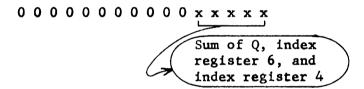

(00100) QJP 0 0 0 6 0 0 QJP 3 0 0 7 0 0