# THE CR8/16 MICROCOMPUTER USER REFERENCE MANUAL

CHRISTIAN ROYSING A/S

Cophenhagen Denmark

THE STATE

ಎನ್ ಶಿಕ್ಷ**್**

L. Thereson

36,77,77

್ರೀಕ್ಷಾಣ್ ಕ್ರಮಿಸಿಕ್ಕಾರ್

1975 To 14

Betalit H

;

A CONTRACTOR OF THE STATE OF TH

# THE SCOPE OF THIS DOCUMENT

This User Guide is intended to answer <u>most</u> of the questions that a potential user of the CR8/16 microcomputer might ask. It aims at breadth rather than depth of coverage - in other words it is considered more important to provide the user with a "Bible" to give at least some guidance about any CR8 topic, rather than to supply every detail on some topics and omit others altogether. In particular, the sections on the CP/M and MP/M operating systems are an overview rather than a comprehensive guide since these operating systems are very widely used in the computing industry and many books have already been written about them.

Incidentally, the same thing applies to the Z80 and 8088 microprocessors which play host to those operating systems.

It is intended that the amount of technical knowledge required to understand this manual will gradually increase as one reads through it. For instance someone with a bare minimum of computer knowledge should be able to understand section 1, whereas section 5 is aimed at people who want to interface their own hardware or system software to the CR8.

The questions that this document attempts to answer are outlined below. Note that the numbering of the questions corresponds to the numbering of the sections that supply the answers. (See contents.)

- 1. What is it?

- 2. Why should I choose a CR8?

- 3. How do I start it up & make it go?

- 4. How do I run my application programs and manage my data and programs?

- 5. How does it work?

Please note that the name "CR8" mentioned throughout this document is an abbreviation for "CR8/16 Microcomputer".

#### **Trademarks**

MDBS III

The following names referred to in this document are the trademarks of the companies mentioned below:

CP/M Digital Research

MP/M Digital Research

Z80A Zilog

18088 Intel® 5 17 5 2

Multibus Intel

Multi Module Intel Intel

M.D.B.S.

dBASE II Ashton-Tate

CBASIC, CBASIC-86 Digital Research

CB, CB-86 Digital Research

PASCAL MT+, SPP Digital Research

RM/COBOL Ryan McFarland Corporation

COGEN Bytek

Document Reference: : CSD-MIC/001/USM/0010

1st Edition : April, 1983

Published by : CHRISTIAN ROVSING A/S

2, Lautrupvang

DK-2750 Ballerup

Copyright © 1983, Christian Rovsing A/S, Copenhagen. All rights reserved. Printed in Denmark. No part of this publication may be reproduced, stored in retrieval system, or transmitted, in any form or by any means electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of Christian Rovsing A/S. Christian Rovsing A/S makes no representation that the interconnection of its product in the manner described herein will not infringe on existing or future patent rights, nor do the herein contained descriptions imply the granting of license or other, to make, use or sell equipment constructed in accordance with these descriptions. Christian Rovsing A/S reserves the right to make changes at any time to improve design and supply the best product possible. Although great efforts have been put into ensuring that information is accurate and up to date, Christian Rovsing A/S assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

# 3.4 Disks, Floppy and Hard 3-8

3.4.1 Use of Floppy Diskettes 3-8

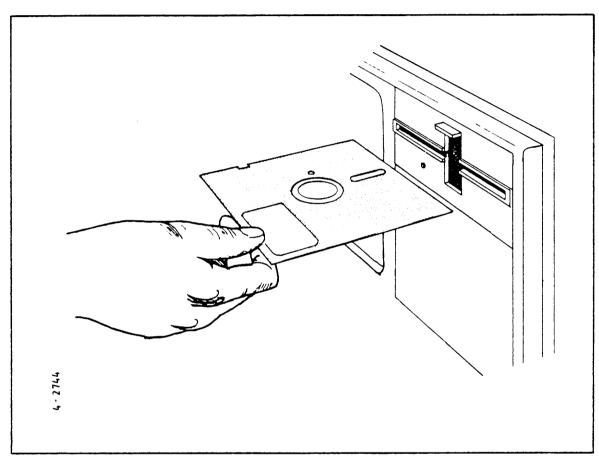

Inserting a Diskette 3-9

Care and Storage of Diskettes 3-10

3.4.2 Disk Formatting 3-10

When 3-11

How 3-11

3.4.3 Copying Disks 3-12

Copying a Complete Floppy Disk on the Dual System 3-12 Copying Single or Multiple Files 3-12

# 3.5 Running Programs 3-13

3.5.1 System Reset 3-13

Integrated Workstation Models 3-13 Cabinet Models 3-13 Selecting the Boot Source 3-14

#### 4. OPERATING SYSTEMS 4-1..16

- 4.1 Disk Files 4-1

- 4.2 The System Prompt 4-2

- 4.3 The Command Line 4-3

- 4.4 Editing the Command Line 4-4

- 4.5 File Specification 4-4

- 4.6 Some System Commands and Utilities 4-8

- 4.7 Special CR8 Commands 4-10

Setting the Baud Rate 4-10

Switching between Danish and English Characters 4-10

System Generation on Floppy-only Systems 4-11

System Generation on Winchester/floppy System 4-11

# 4.8 Disk Access Error Codes 4-12

Floppy 4-12

Winchester 4-13

# 5. CR8 TECHNICAL OVERVIEW 5-1..229

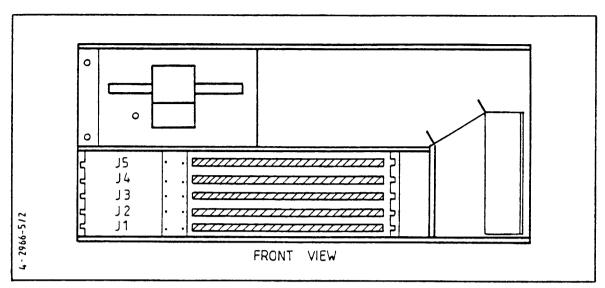

# 5.1 The CR8 Cabinet 5-1 and the contract of

- 5.1.1 Physical Layout 5-2

- 5.1.2 Installation of Multibus Modules 5-3

- 5.1.3 Mother Board 5-4

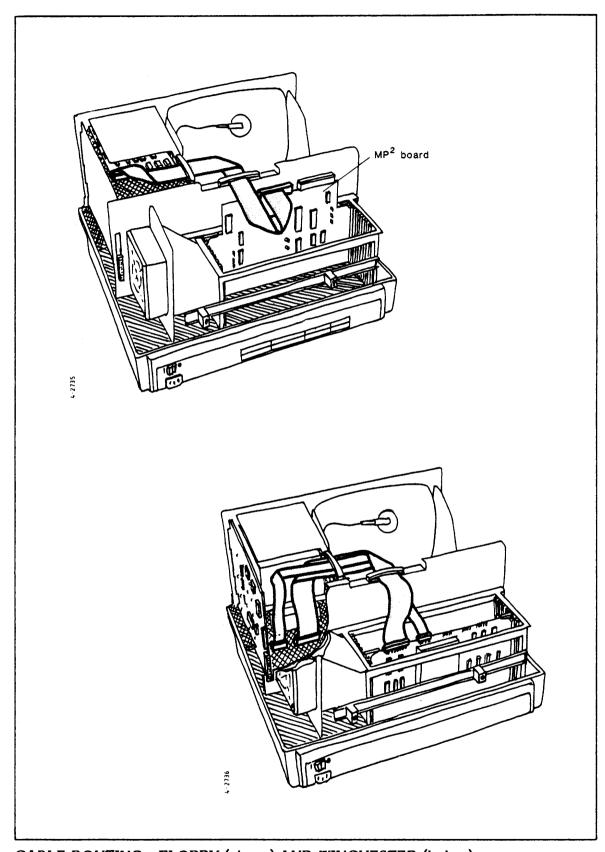

- 5.1.4. Cabling (Cabinet to MP<sup>2</sup>) 5-6

- 5.1.5 Installation of Disk Drives 5-6

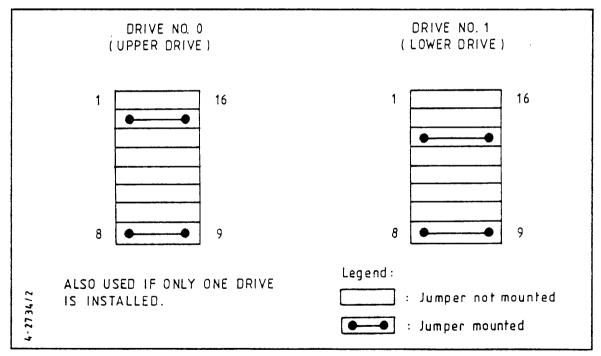

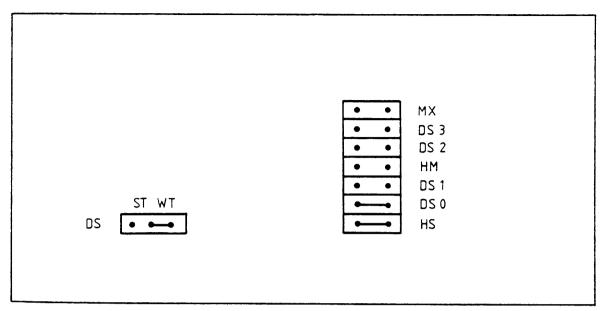

- 5.1.5.1 Jumper Settings 5-7

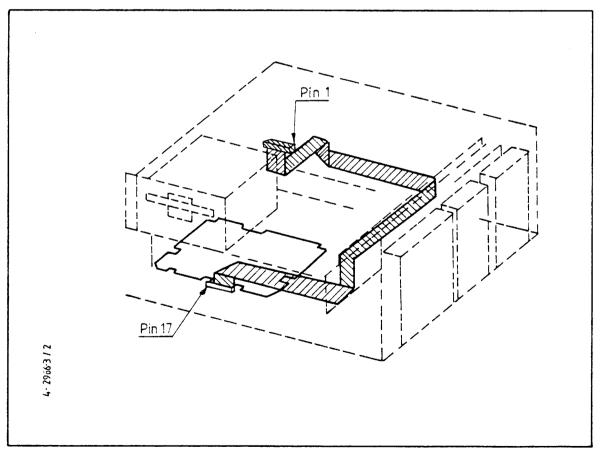

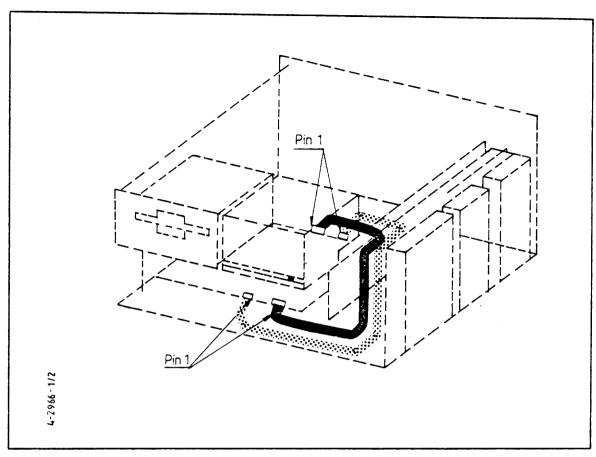

- 5.1.5.2 Cabling 5-8

- 5.1.6 Power Supply 5-10

#### 5.2 CR8 Workstation 5-12

- 5.2.1 Features 5-12

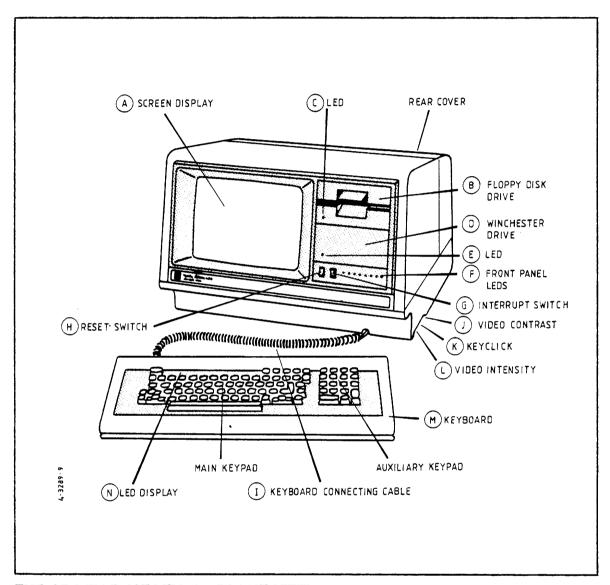

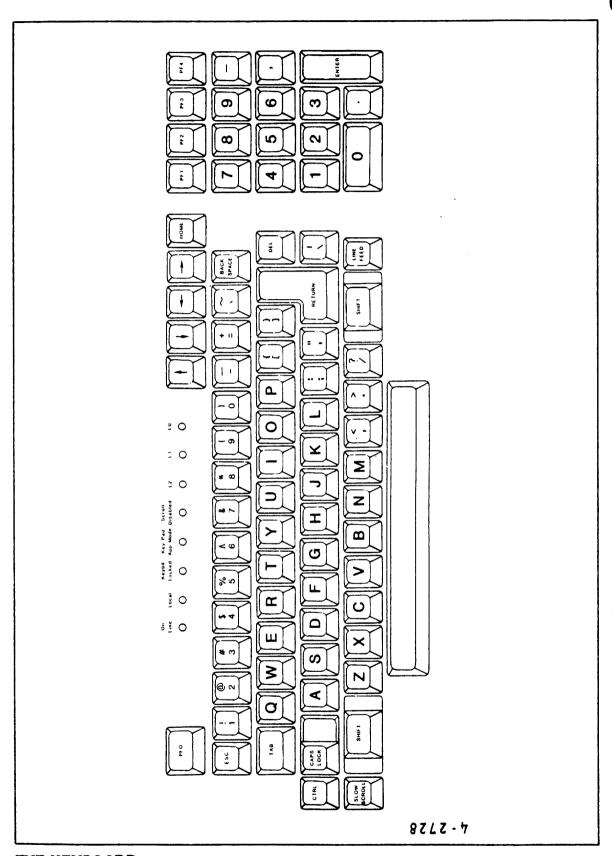

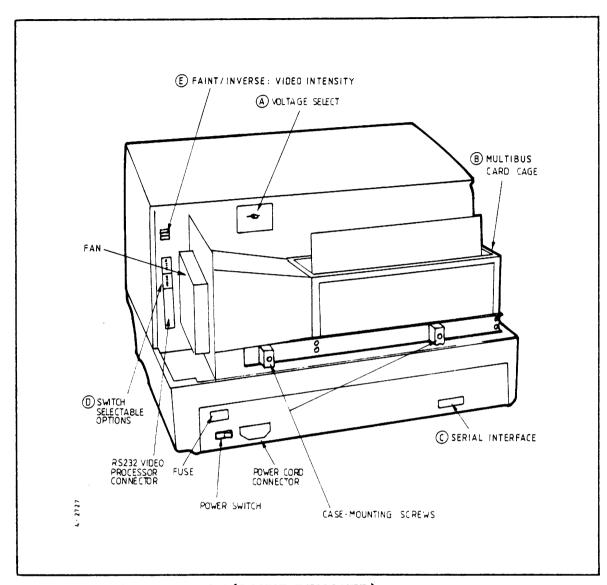

- 5.2.2 Terminal Components & Controls 5-135.2.2.1 Switch Selectable Options 5-19

- 5.2.3 Programmers' Information 5-25

- 5.2.3.1 Control Codes 5-25

- 5.2.3.2 Keypad Modes 5-26

- 5.2.3.3 Partitions and Scolling Regions 5-28

- 5.2.3.4 Terminal Modes 5-30

- 5.2.3.5 Cursor Control 5-32

- 5.2.3.6 LED Control 5-36

- 5.2.3.7 Attributes 5-36

- 5.2.3.8 Form-drawing Characters 5-37

- 5.2.3.9 Tabulation 5-39

- 5.2.3.10 Edit Commands 5-40

- 5.2.3.11 Status and Cursor Reports 5-44

- 5.2.3.12 Alternate Character Set 5-45

- 5.2.3.13 Reset 5-46

- 5.2.3.14 Screen Alignment Display 5-46

- 5.2.3.15 Escape Sequence Summary 5-48

| 5.2.4              | 2.4 Hardware Configuration Details 5-50 |                                                  |  |  |  |

|--------------------|-----------------------------------------|--------------------------------------------------|--|--|--|

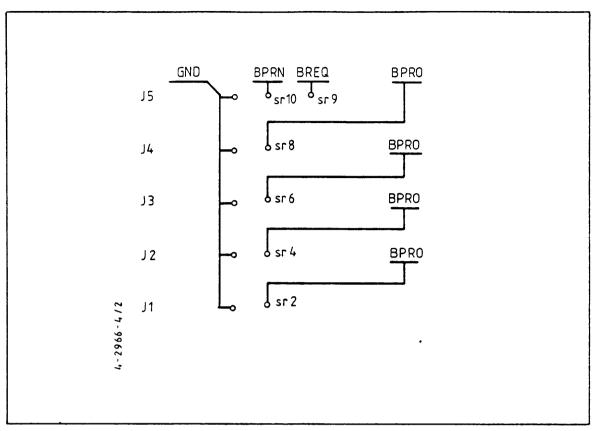

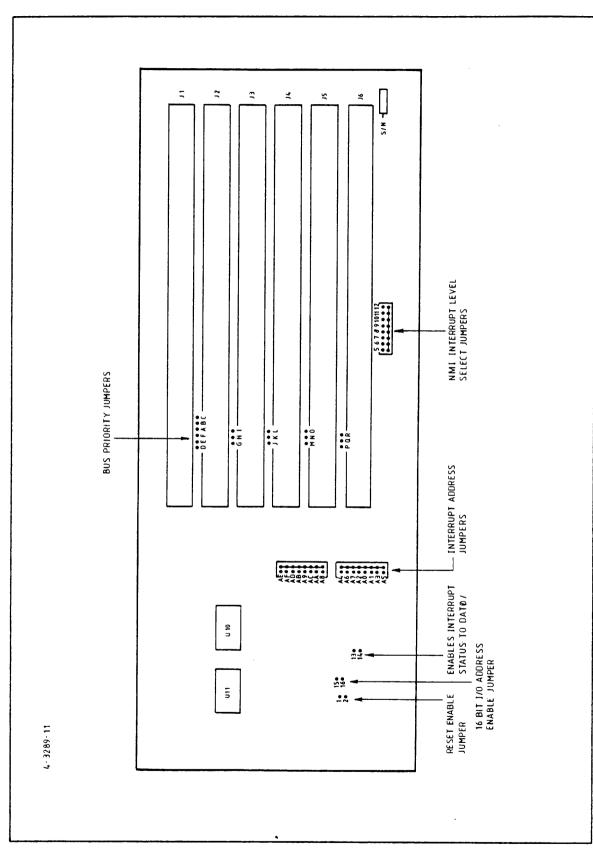

|                    | 5.2.4.1                                 | Bus Arbitration 5-50                             |  |  |  |

|                    | 5.2.4.2                                 | Reset Switch Logic 5-53                          |  |  |  |

|                    | 5.2.4.3                                 | Interrupt Switch Logic Configuration 5-53        |  |  |  |

|                    | 5.2.4.4                                 | Multibus IEEE 796 Differences 5-55               |  |  |  |

|                    | 5.2.4.5                                 | Backplane Power Supply 5-55                      |  |  |  |

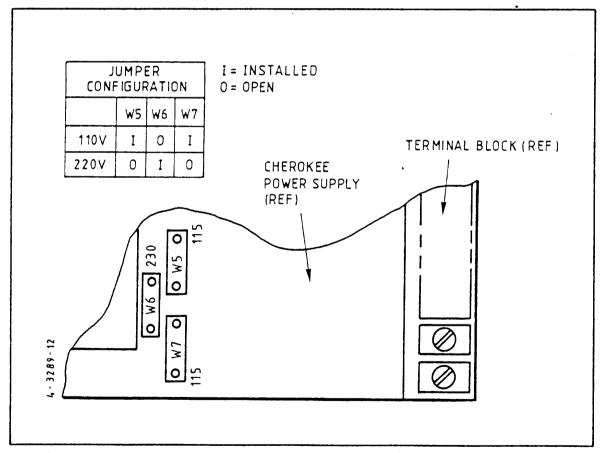

|                    | 5.2.4.6                                 | Voltage Select 5-56                              |  |  |  |

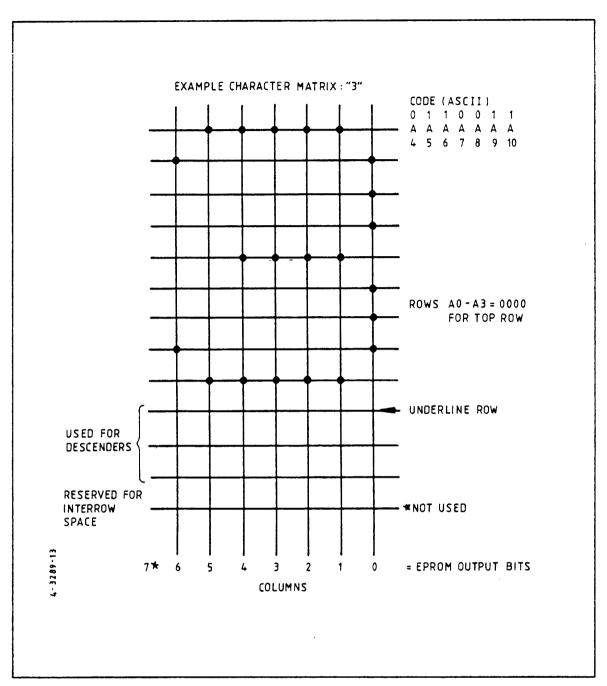

|                    | 5.2.4.7                                 | Alternate Character Set ROM Generation 5-57      |  |  |  |

|                    | 5.2.4.8                                 | RS232 Interface 5-58                             |  |  |  |

|                    | 5.2.4.9                                 | Cabling 5-61                                     |  |  |  |

| _                  |                                         |                                                  |  |  |  |

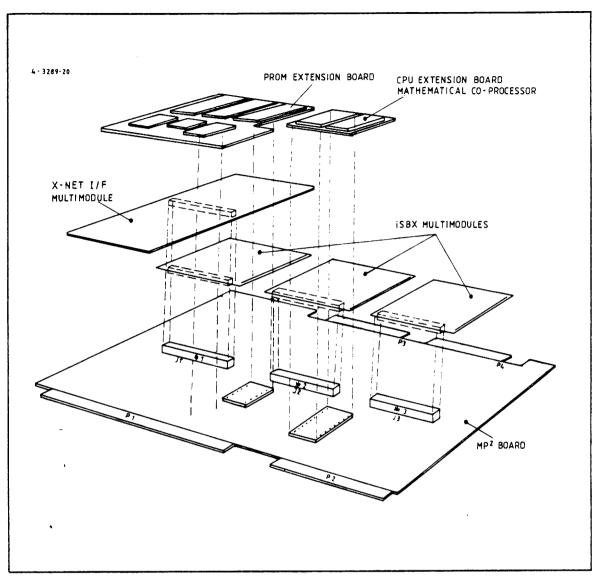

| MP <sup>2</sup> Ca | ard 5-63                                |                                                  |  |  |  |

| 5.3.1              | Introduction                            | on 5-63                                          |  |  |  |

| 5.3.2              | Functional                              | Summary 5-65                                     |  |  |  |

|                    | 5.3.2.1                                 | Main Processor 5-67                              |  |  |  |

|                    | 5.3.2.2                                 | Front Processor 5-68                             |  |  |  |

|                    | 5.3.2.3                                 | Multibus Interface 5-73                          |  |  |  |

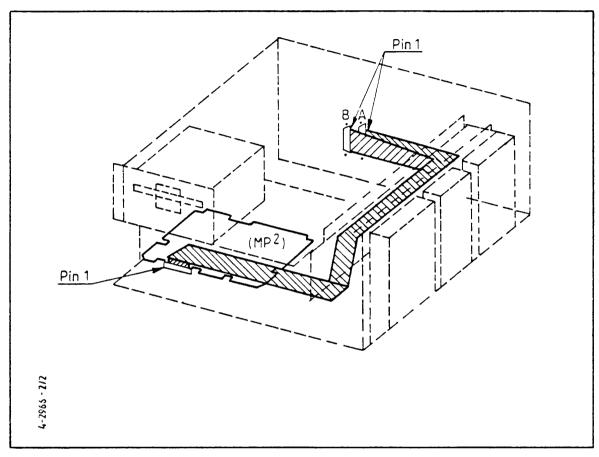

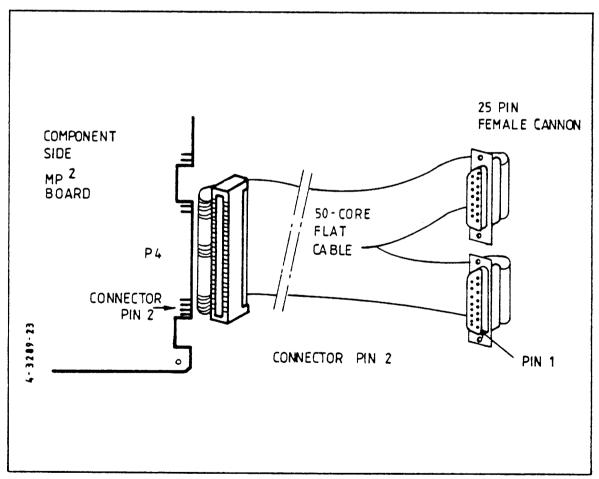

|                    | 5.3.2.4 Multimodule Interface 5-74      |                                                  |  |  |  |

|                    | 5.3.2.5                                 | MP <sup>2</sup> Bus Arbiter & Control Logic 5-74 |  |  |  |

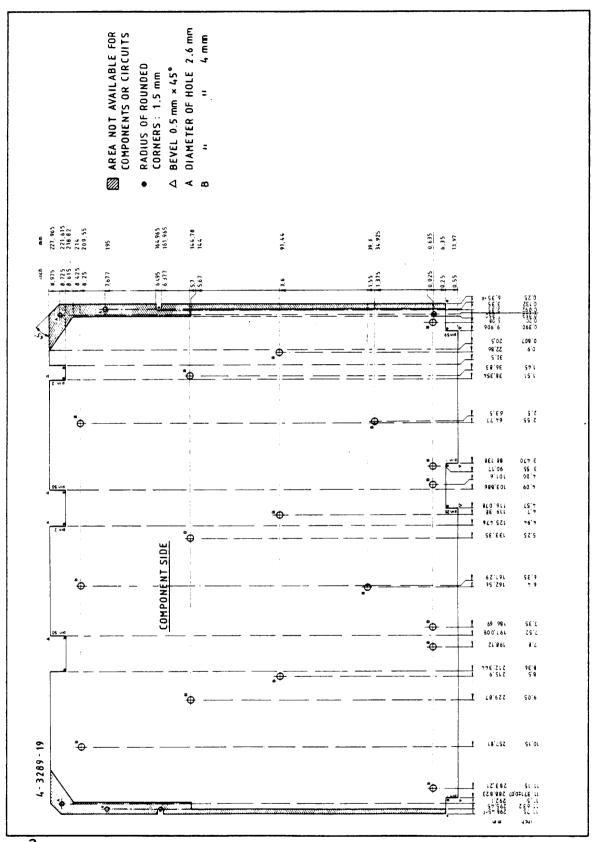

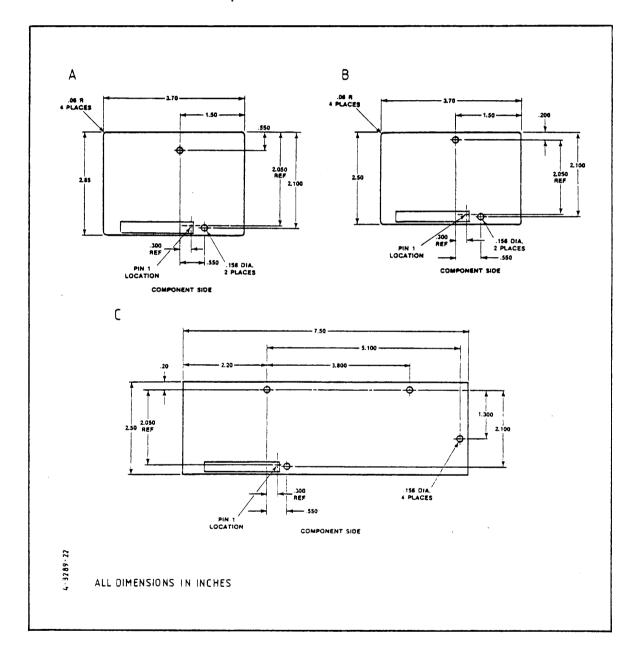

|                    | 5.3.2.6                                 | Mechanical Layout 5-75                           |  |  |  |

| 5.3.3              | Interface S                             | Specification 5-79                               |  |  |  |

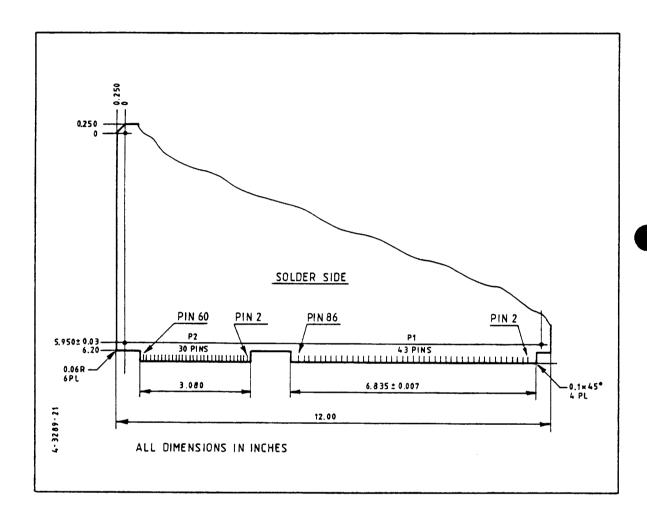

|                    | 5.3.3.1                                 | Multibus Interface 5-79                          |  |  |  |

|                    |                                         | Signal Specification 5-80                        |  |  |  |

|                    |                                         | Electr. Specification 5-85                       |  |  |  |

|                    |                                         | Mech. Specification 5-86                         |  |  |  |

|                    | 5.3.3.2                                 | Multimodule Interface 5-86                       |  |  |  |

|                    |                                         | Signal Specification 5-87                        |  |  |  |

|                    |                                         | Electr. Specification 5-90                       |  |  |  |

|                    |                                         | Mech. Specification 5-91                         |  |  |  |

|                    | 5.3.3.3                                 | Floppy Disc Interface 5-92                       |  |  |  |

|                    |                                         | Signal Specification 5-92                        |  |  |  |

|                    |                                         | Electr. Specification 5-95                       |  |  |  |

|                    | ₩## € S                                 | Mech. Specification 5-95                         |  |  |  |

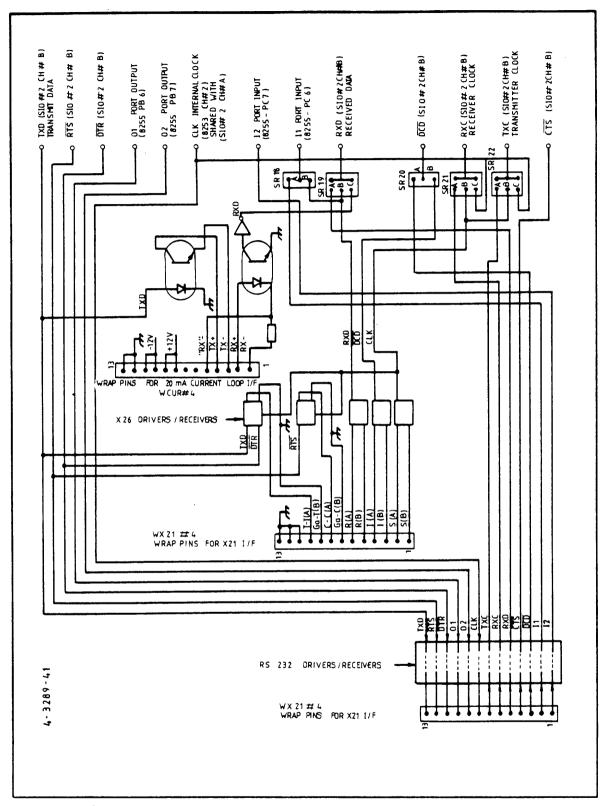

|                    | 5.3.3.4                                 | Line Communication Interface 5-95                |  |  |  |

|                    |                                         | Signal Specification 5-96                        |  |  |  |

|                    |                                         | Electrical Specification 5-98                    |  |  |  |

|                    |                                         | Mach Specification 5 00                          |  |  |  |

5.3

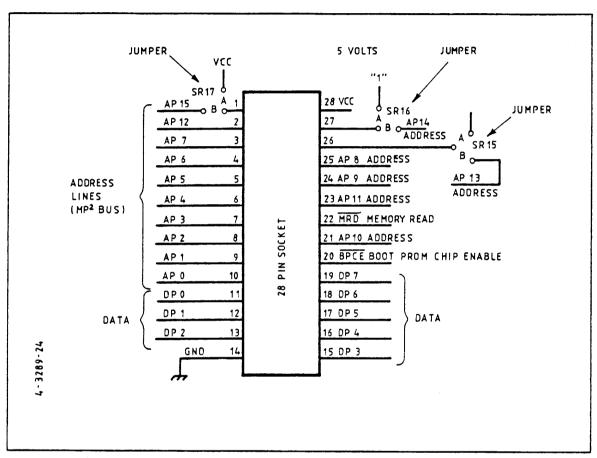

|        | 5.3.3.5                                       | Boot Load PROM 5-99                         |  |  |  |

|--------|-----------------------------------------------|---------------------------------------------|--|--|--|

|        |                                               | Signal Specification 5-99                   |  |  |  |

|        | 5.3.3.6                                       | Mathematics Co-processor 5-100              |  |  |  |

| 5.3.4  | Program                                       | ming and Operational Considerations 5-101   |  |  |  |

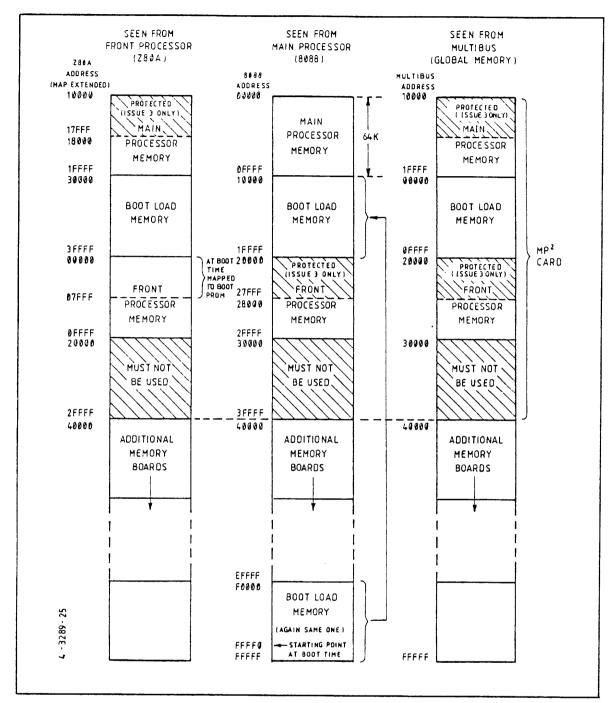

|        | 5.3.4.1                                       | I/O and Memory Addressing 5-102             |  |  |  |

|        |                                               | CR8 Memory Map +5-103                       |  |  |  |

|        |                                               | MP <sup>2</sup> Base Address 5-104          |  |  |  |

|        |                                               | CR8 I/O Map 5-106                           |  |  |  |

|        |                                               | Base Address (I/O) 5-107                    |  |  |  |

|        |                                               | Addressing the Boot PROM 5-107              |  |  |  |

|        | 5.3.4.2                                       | Extended Addressing for the Z80A 5-107      |  |  |  |

| 5.3.5  | Battery E                                     | Backup Option 5-111                         |  |  |  |

| 5.3.6  | Power Sp                                      | pecifications 5-112                         |  |  |  |

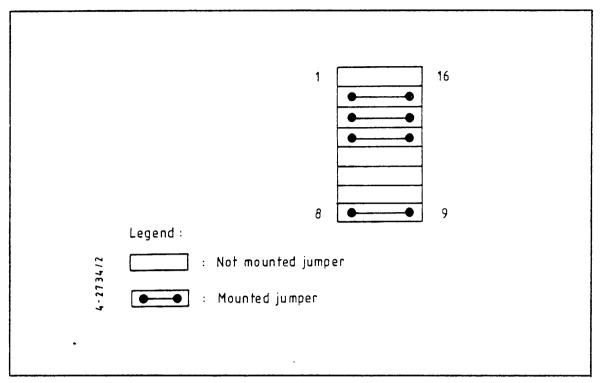

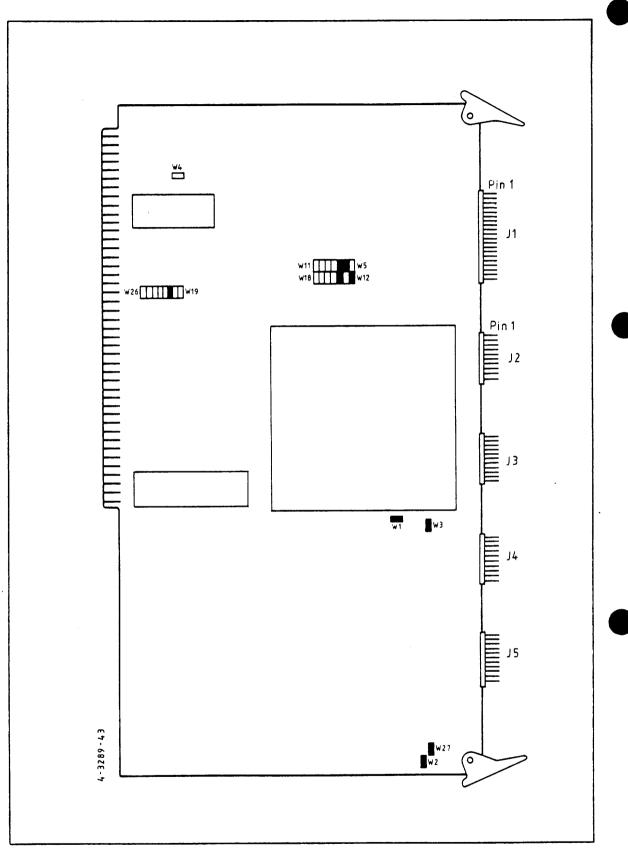

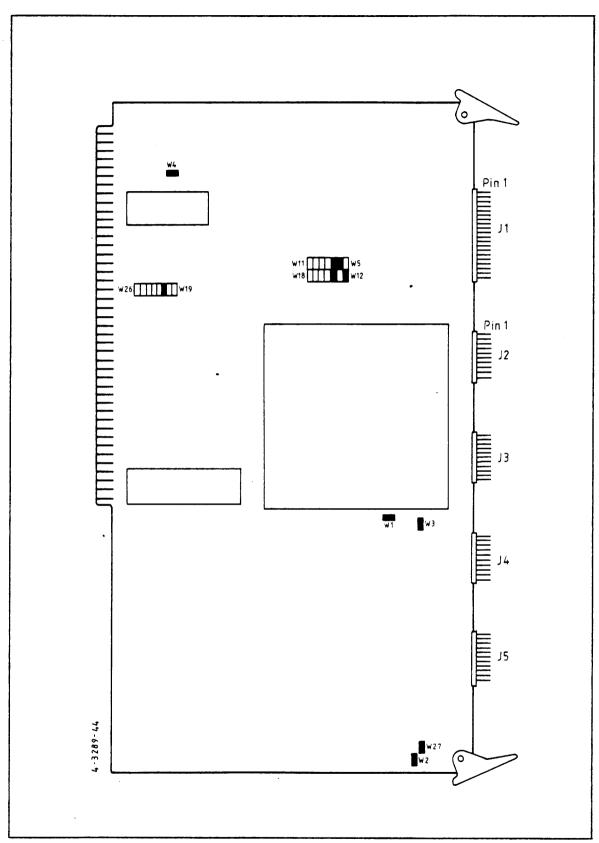

| 5.3.7  | Jumper &                                      | k Switch Settings 5-113                     |  |  |  |

| 5.3.8  |                                               | Differences between Issue 3                 |  |  |  |

|        | and Issue 4 of the MP <sup>2</sup> Card 5-118 |                                             |  |  |  |

|        |                                               | ·                                           |  |  |  |

| SCI Bo | ard 5-119                                     |                                             |  |  |  |

| 5.4.1  | Introduction 5-119                            |                                             |  |  |  |

| 5.4.2  | Function                                      | al Description 5-120                        |  |  |  |

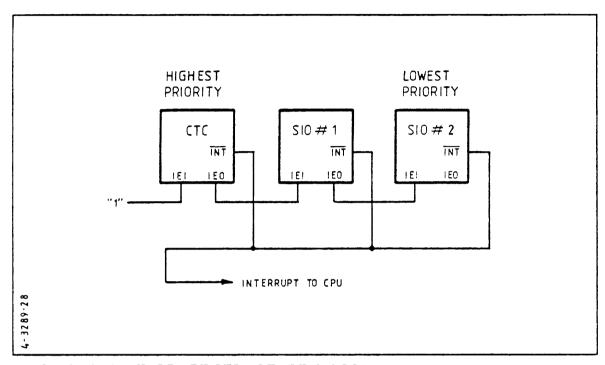

|        | 5.4.2.1                                       | Counter/Timer Circuit 5-125                 |  |  |  |

|        | 5.4.2.2                                       | Serial I/O Controllers 5-125                |  |  |  |

|        | 5.4.2.3                                       | "Daisy Chain" Interrupt Priorities 5-126    |  |  |  |

|        | 5.4.2.4                                       | Programmable Interval Timer 5-126           |  |  |  |

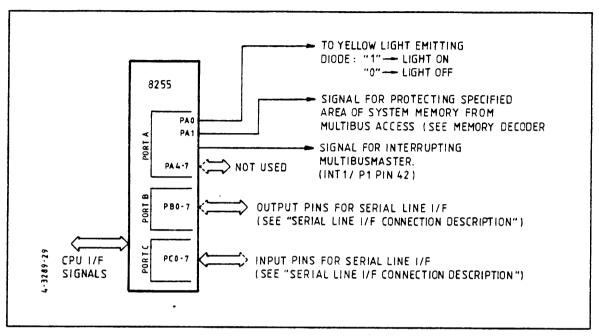

|        | 5.4.2.5                                       | Programmable Parallel I/O Port 5-127        |  |  |  |

|        | 5.4.2.6                                       | DMA Controller 5-127                        |  |  |  |

|        | 5.4.2.7 Booting the SCI 5-128                 |                                             |  |  |  |

|        | 5.4.2.8                                       | Pin Assignment on Edge Connector 5-129      |  |  |  |

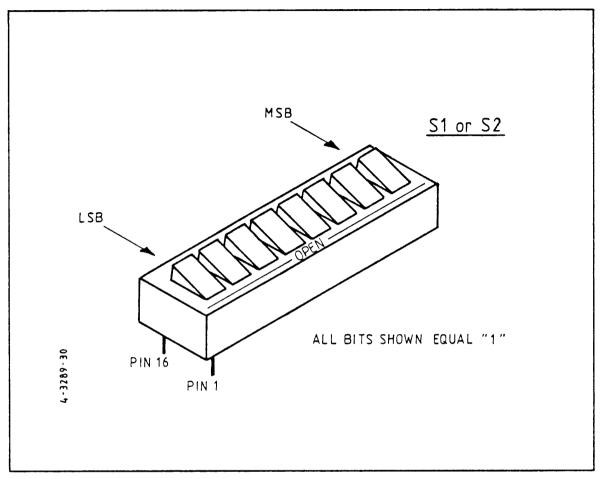

|        | 5.4.2.9                                       | On-board Switches S1 & S2 5-130             |  |  |  |

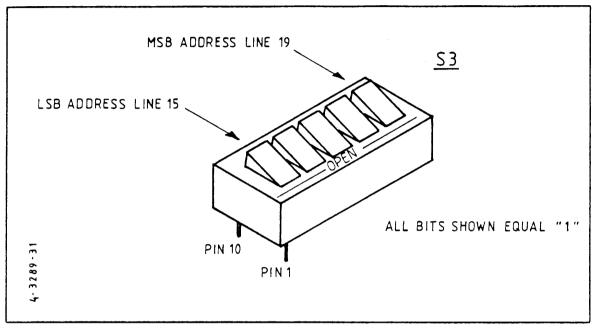

|        | 5.4.2.10                                      | Switch S3 - Board Address 5-131             |  |  |  |

|        | 5.4.2.11                                      | I/O Address Map 5-131                       |  |  |  |

| •      | 5.4.2.12                                      | Memory Address Map 5-134                    |  |  |  |

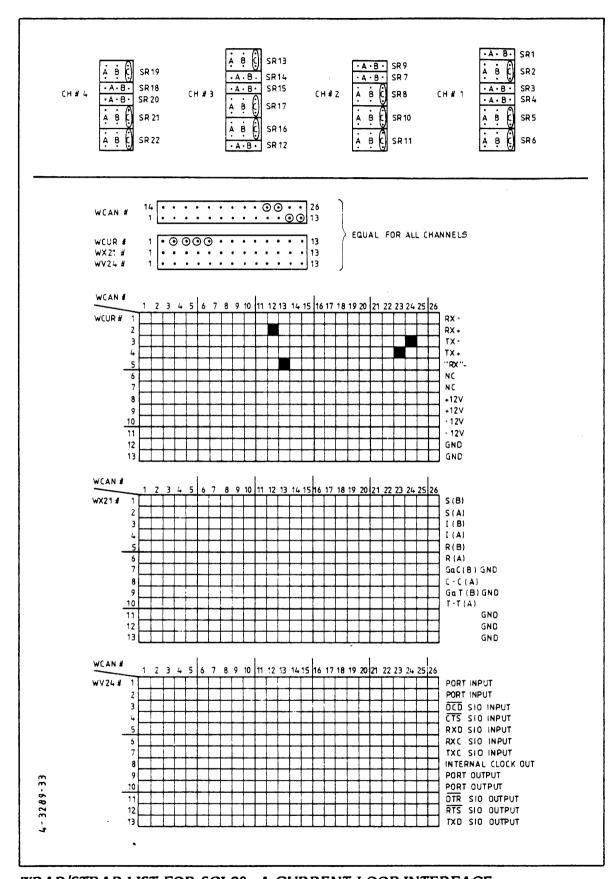

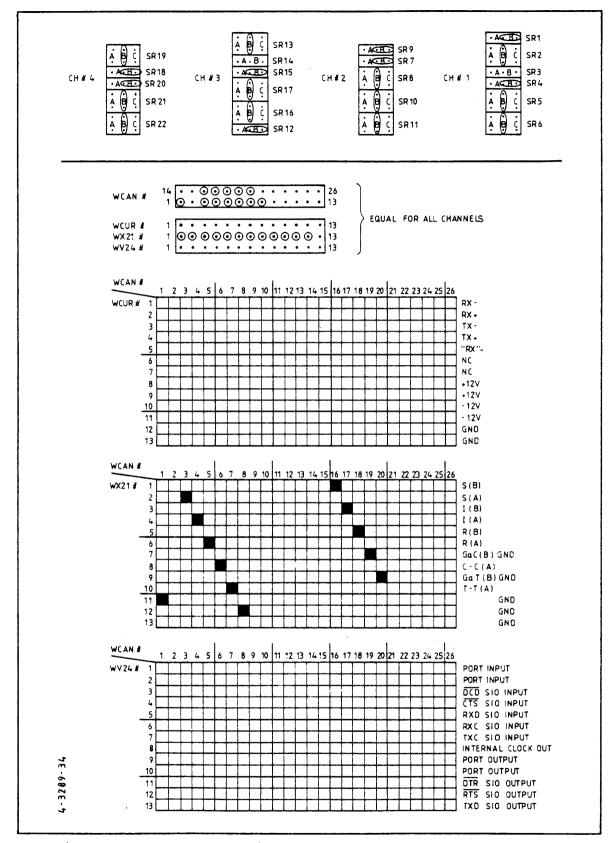

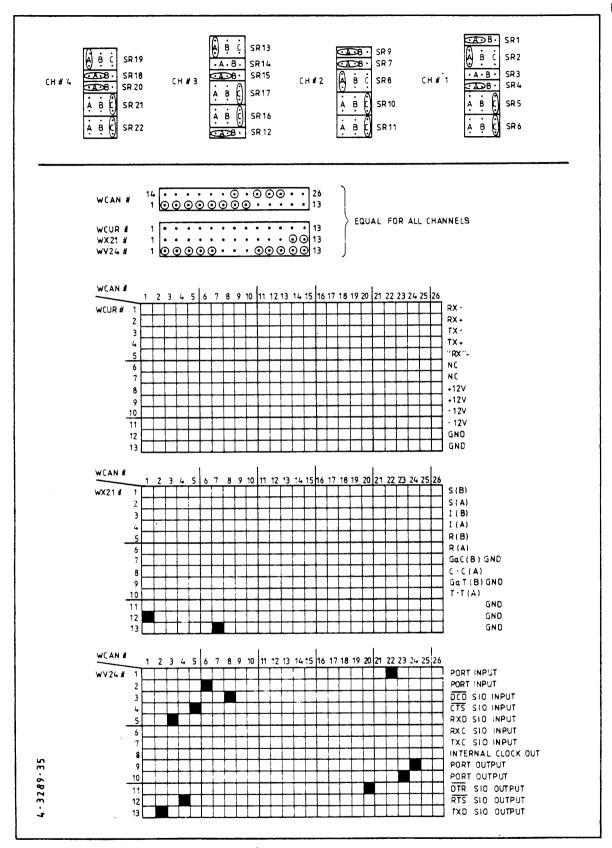

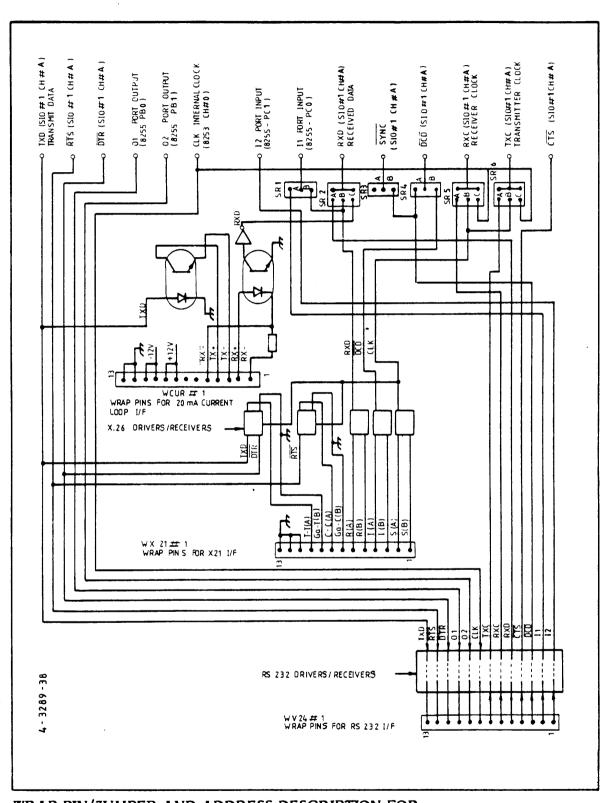

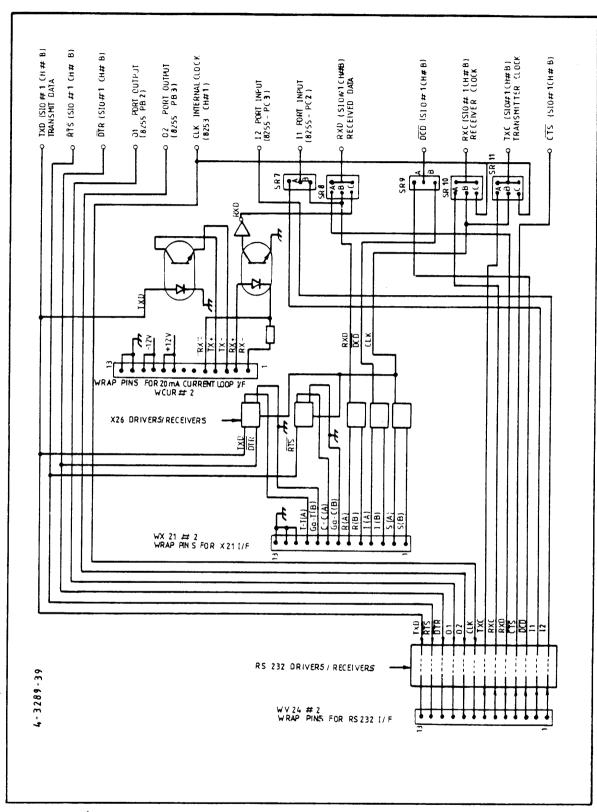

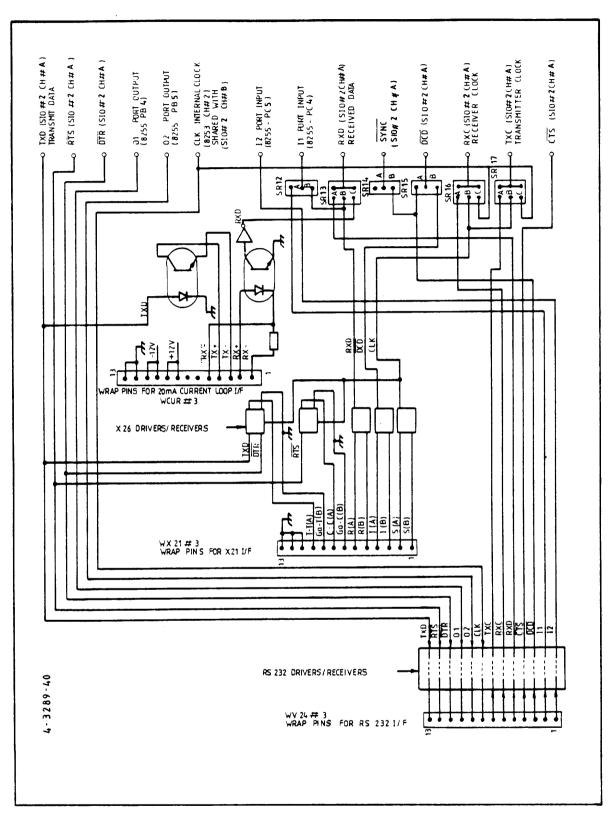

|        | 5.4.2.13                                      | Jumpers & Wire-wraps                        |  |  |  |

|        |                                               | (Standard Interfaces) 5-135                 |  |  |  |

| r      | 5.4.2.14                                      | Jumpers & Wire-wraps (description of) 5-139 |  |  |  |

5.4

- 5.5 Winchester & Controller 5-144

- 5.5.1 Disk Drive 5-144

- 5.5.2 Controller Board and its Jumper Settings 5-145

- 5.5.3 Formatting 5-151

- 5.6 Floppy Disk Drive 5-153

- 5.7 System Reset 5-155

- 5.7.1. CP/M 2.2 5-155

- 5.7.2 CP/M 86 5-156

- 5:7.3 MP/M II 5-157

- 5.7.4 MP/M 86 5-158

- 5.8 Adding More Memory 5-159

- 5.9 The SCRIMP/M Operating System 5-160

- 5.9.1 XMOS 5-162

- 5.9.1.1 The Purpose of XMOS 5-162

- 5.9.1.2 Some Terms Explained 5-163

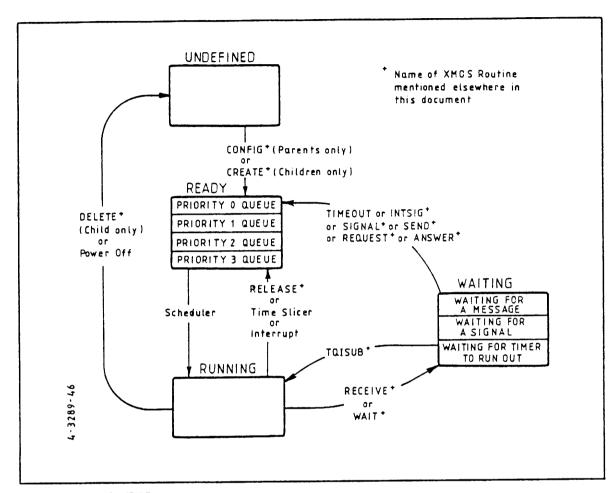

- 5.9.1.3 Process States 5-165

- 5.9.1.4 Process Hierarchy 5-166

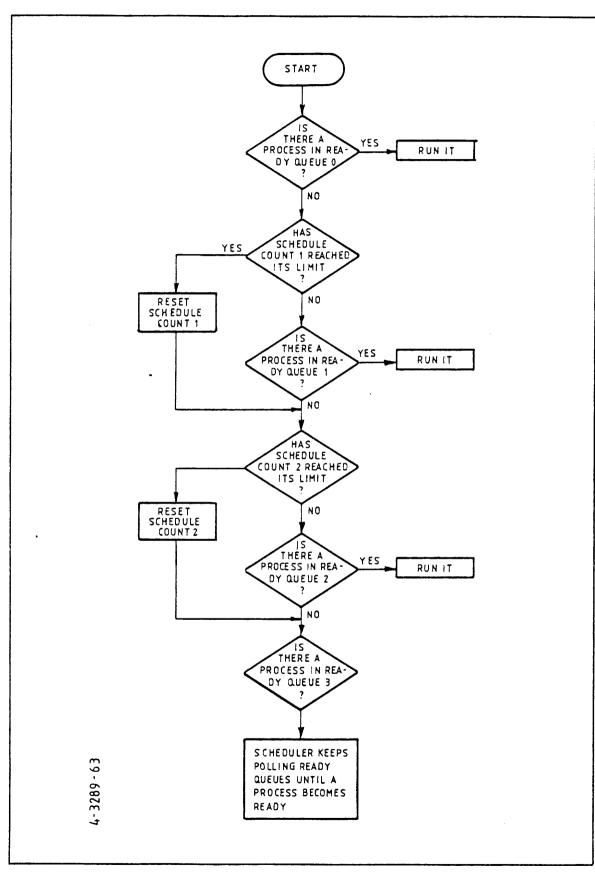

- 5.9.1.5 Scheduling 5-168

- 5.9.1.6 Memory & Time Requirements 5-171

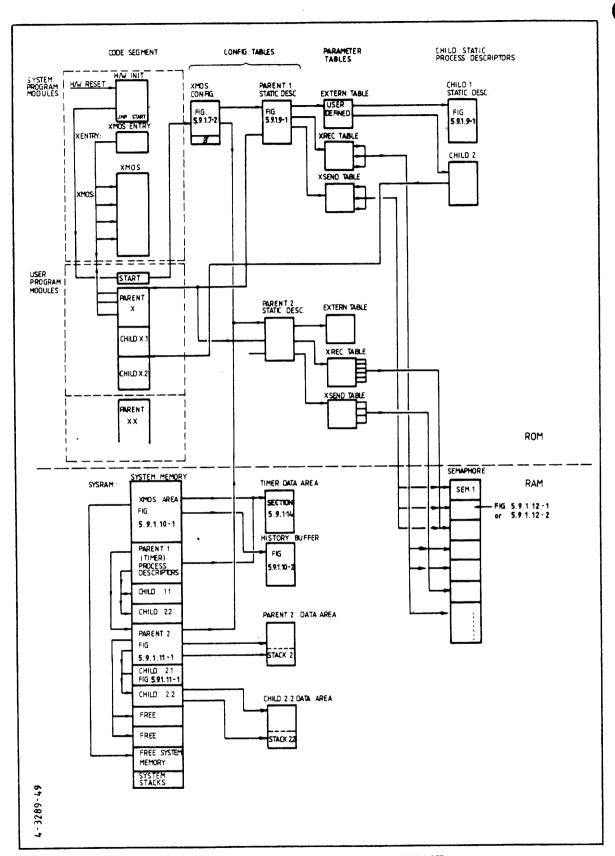

- 5.9.1.7 Storage Allocation 5-172

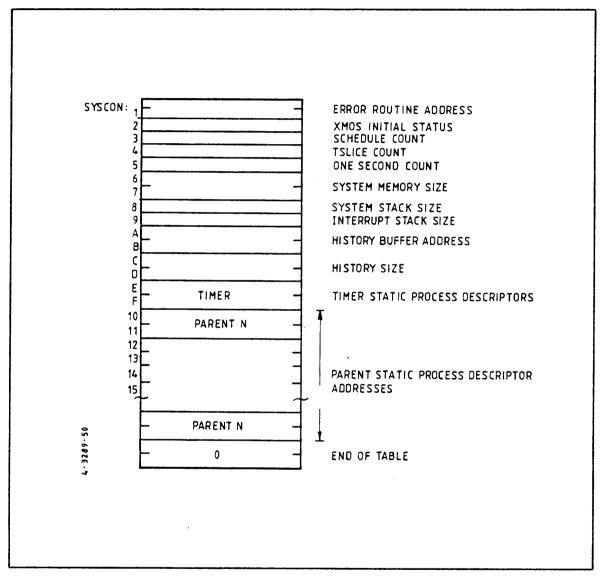

- 5.9.1.8 Configuration Table 5-174

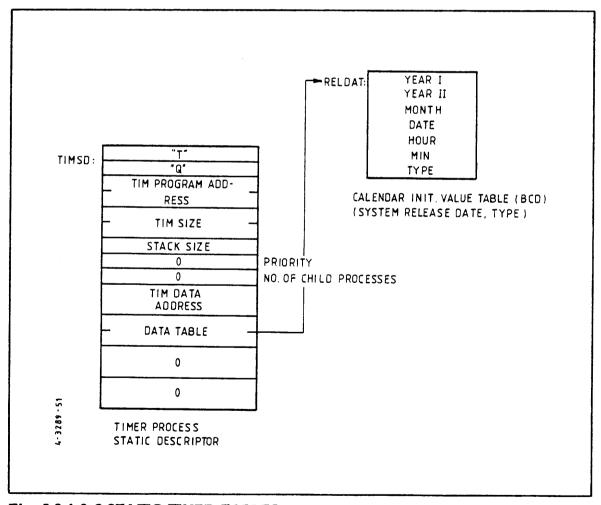

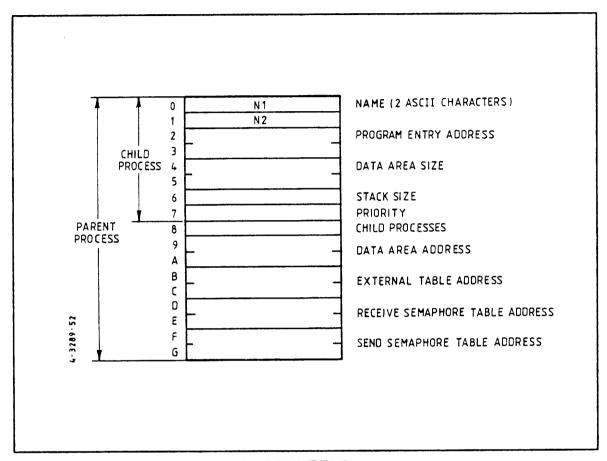

- 5.9.1.9 Static Process Descriptors 5-177

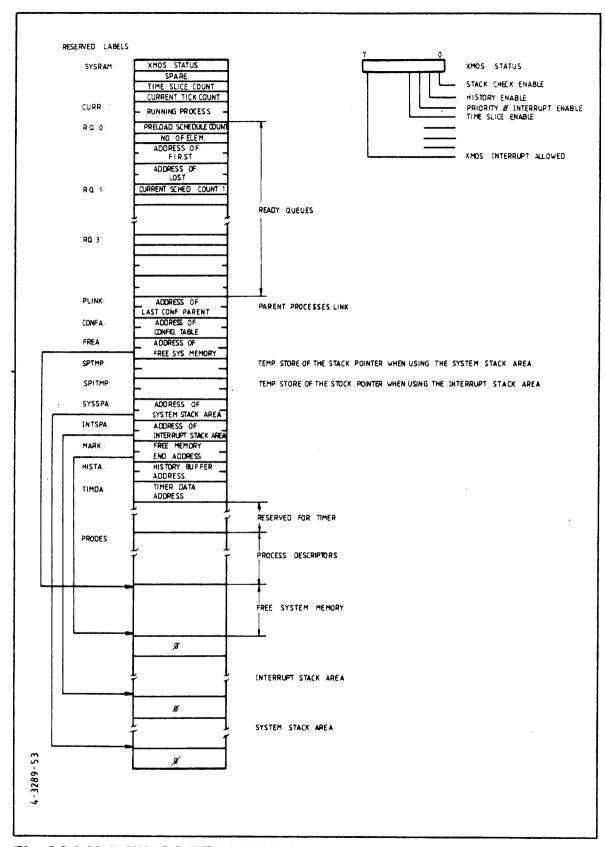

- 5.9.1.10 The "SYSRAM:" Area 5-179

- 5.9.1.11 Dynamic Process Descriptors 5-182

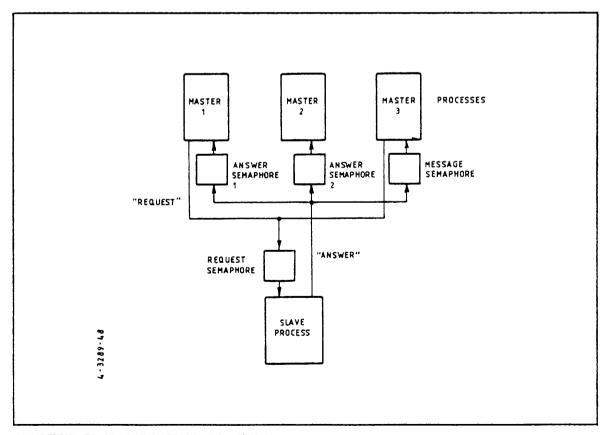

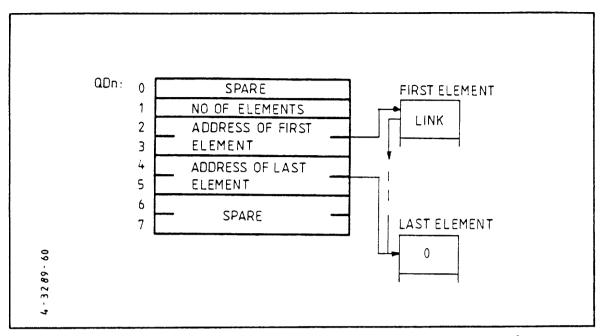

- 5.9.1.12 Semaphores and queues 5-183

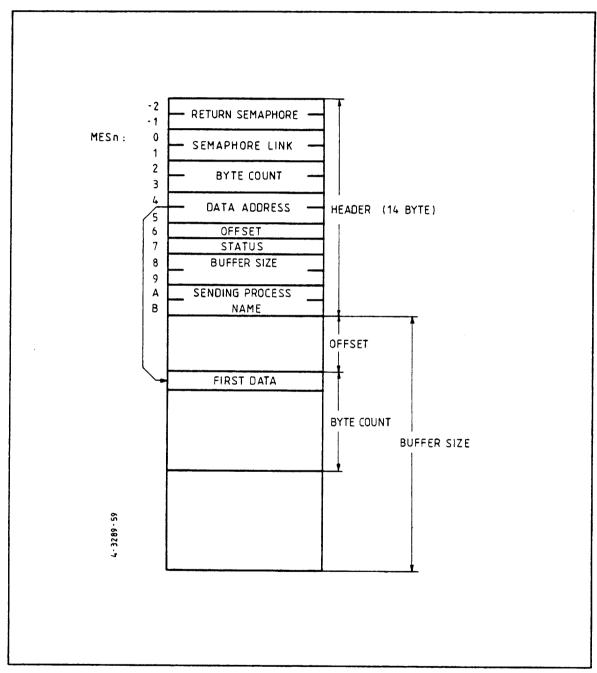

- 5.9.1.13 Messages 5-186

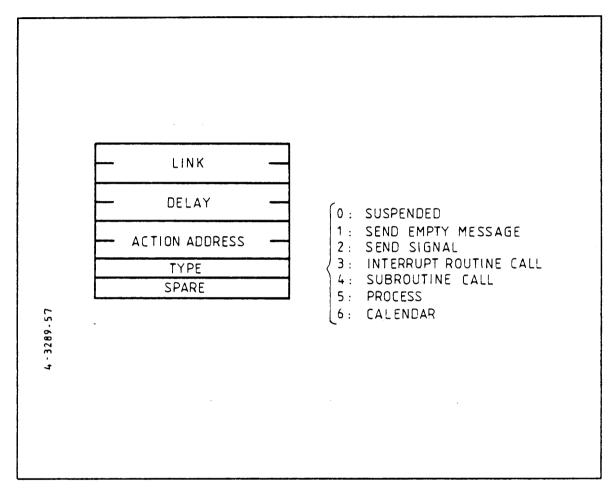

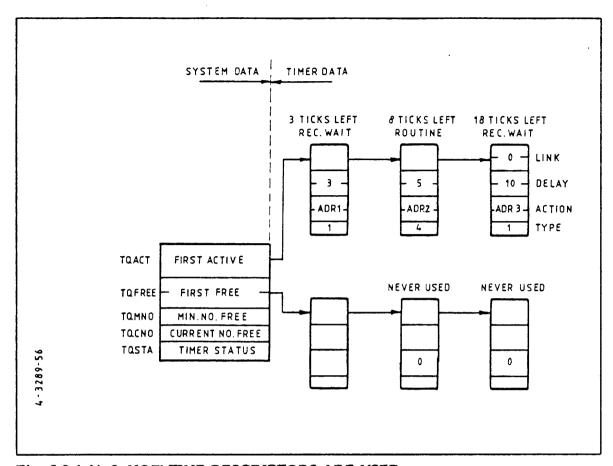

- 5.9.1.14 The Time Queue Monitor (TQM) 5-187

- 5.9.1.15 How to Use the XMOS Software Package 5-189

List of User Interface Routines 5-191

List of Time Queue Monitor Routines 5-191

List of Buffer Queue Monitor Routines 5-192

5.9.1.15.1 The 'User Interface' Routine 5-193

CONFIG 5-193

CREATE 5-193

DELETE 5-194

CURRENT 5-194

RELEASE 5-194

WAIT 5-195

SIGNAL 5-196

INTSIG 5-197

RECEIVE 5-197

ACCEPT 5-198

SEND 5-198

INTSEN 5-199

REQUEST 5-199

ANSWER 5-200

5.9.1.15.2 The Time Queue

Monitor Routines 5-201

TQEMES 5-201

TQISIG 5-201

TQSUB 5-201

TQISUB 5-202

TQSUSP 5-202

Calendar 5-203

5.9.1.15.3 The Buffer Queue

Monitor Routines 5-204

BQDEQ 5-204

BQENQ 5-204

BQSEND 5-205

BQRET 5-205

BQMOV 5-206

BQGET 5-206

BQCRE 5-206

BQSET 5-207

BQFIFI *5***-**207

BQFILA 5-208

BQLDTX 5-208

BQADTX 5-209

BQPOTX 5-209

BQADFI *5***-**209

BQADLA 5-210

BQAJFI 5-211

BQLDBC 5-211

BQLDRQ 5-212

BQRDRQ 5-212

BQRDNA 5-212

BQLDNA 5-212

SETSTA 5-213

SRESTA 5-213

- 5.9.2 Device Drivers Under SCRIMP/M 5-214

- 5.9.3 How to Incorporate a New Process into the SCRIMP/M System 5-224

----

5.9.3.1 Testing the New Process 5-224

5.9.3.2 Integrating the New System onto the System Tracks 5-224

- 5.9.4 Communication between SCRIMP/M and MP/M 5-226

- 5.10 Setting Baud Rate and other Characteristics of Terminals 5-227

- 5.10.1 CR7 Comfort 5-227

- 5.10.2 CR5 Compass 5-229

- 5.10.3 Tandberg TDV 2230 5-229

- 5.10.4 CR8 Integrated Workstation 5-229

- 6. LIST OF ABBREVIATIONS 6-1..2

- 7. **INDEX** 7-1..35

Form for Readers' Comments

Fig. 1. Control of the state of Standard Committee of the Committee of t And the second of the second o The Transfer of the Control of the C

- A CONTROL OF THE CONT

# . INTRODUCTION TO THE CR8

#### 1.1 BRIEF DESCRIPTION OF THE CR8

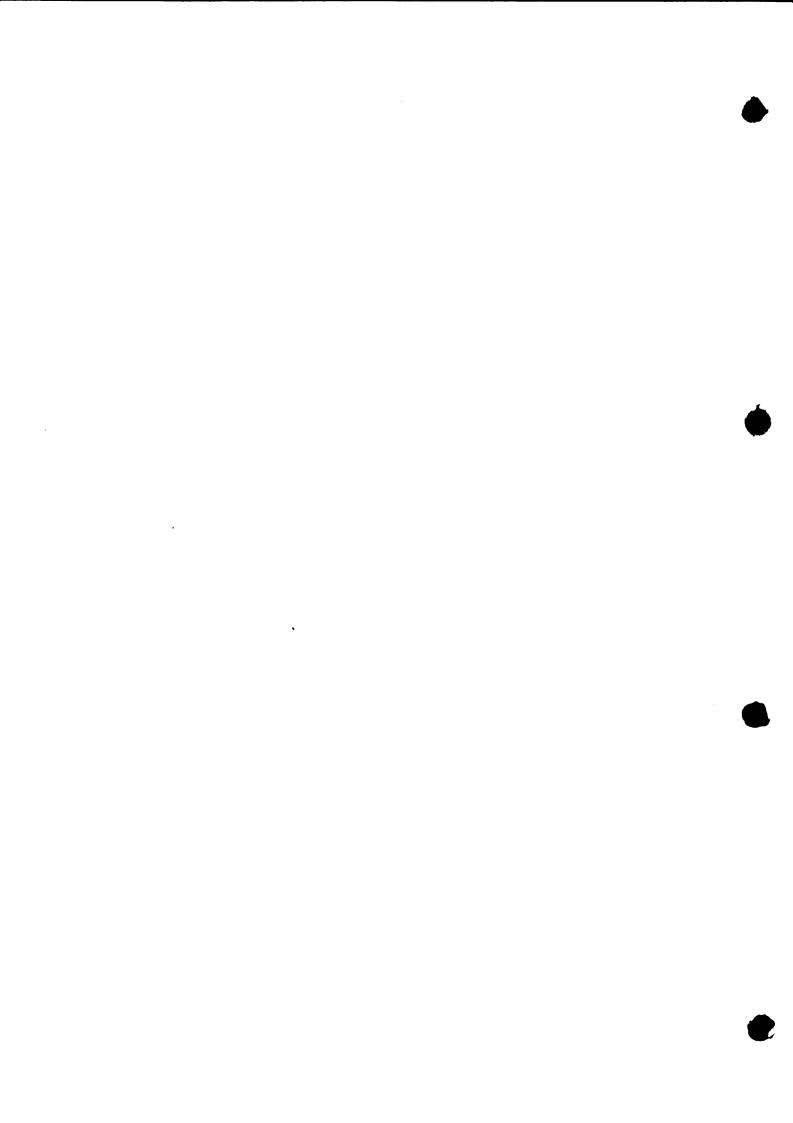

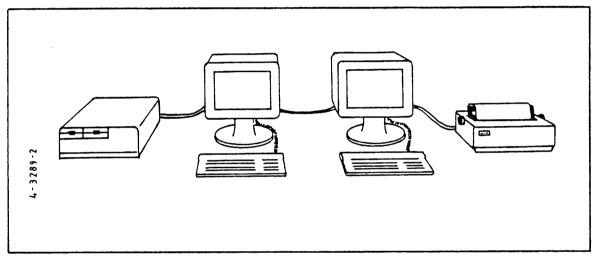

The CR8 is a complete general-purpose microcomputer system which is available in a variety of hardware and software configurations. It comes in two basic forms: the cabinet model and the integrated workstation. The integrated workstation looks like a normal VDU but it also contains the main processor(s) and disc drives - in fact a complete stand-alone computer system. The cabinet model contains much the same components, but the terminal(s) is (are) separate.

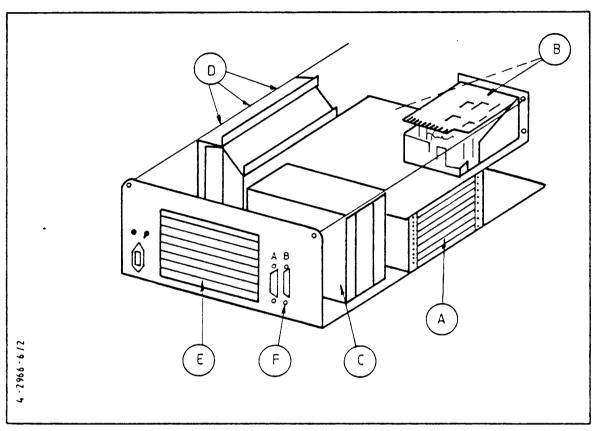

CR8 CABINET MODEL (A TYPICAL CONFIGURATION)

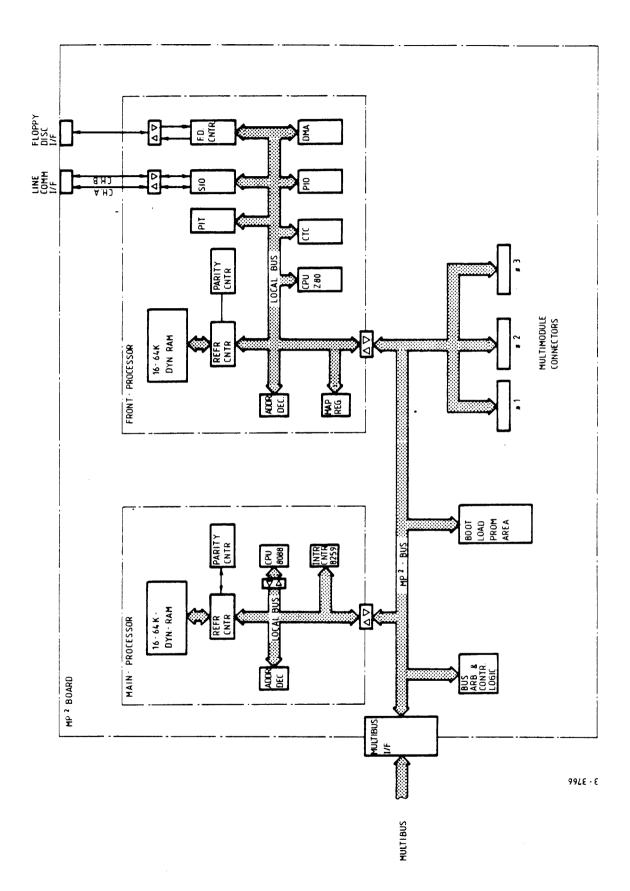

At the heart of every CR8 is the MP<sup>2</sup> (Multi Purpose Multi Processor) board. This is the part that controls the whole CR8 computer system and does the 'thinking'; it is here that programs 'run'. This single printed circuit board houses a Z80A single chip microprocessor plus the option of using an 8088 microprocessor as well. Up to 128K bytes of on-board RAM is accessible; a floppy disk controller and two serial interfaces (for connecting terminals or printers) are also included.

Every CR8 also includes 2 disk drives (apart from some special-purpose models). A disk drive is used for bulk storage of information - very often in the form of (an electronic representation of) text which can be displayed on a terminal or printer. Programs that define and control the duties to be performed are also stored on disk.

**CR8 INTEGRATED WORKSTATION**

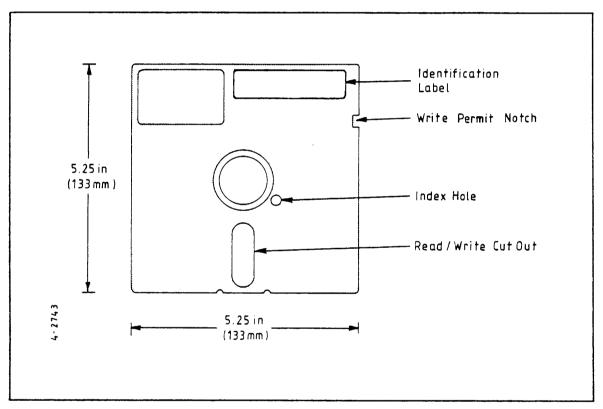

There are two types of disk drive available - floppy and hard. A floppy disk can hold less information than the hard (otherwise known as Winchester) disk, but has the advantage that the disks may be removed. Thus the upward limit of available storage depends only upon the available cupboard space for floppy disks.

The third vital component of the CR8 is one or more terminals. A terminal has two parts - a keyboard with which the user communicates with the processor board and a VDU screen or printer with which the processor communicates with the user.

There are also various optional circuit boards which are needed for certain applications. These include the SCI board which allows the connection of four more terminals to the CR8; the XMA board which allows connection to any number of other terminals or computers via an X-Net network; and the PAM bus driver board which turns the CR8 into a PAM process control system. The next section describes the various options in more detail.

ti. kening

All this equipment would be useless without some **software**. If the reader will excuse a small digression into some homespun philosophy, a computer without software is like a man without life. In other words a dead man is physically much the same as a live one, he consists of the same organs assembled in the same way. However, he cannot do anything at all, he is totally useless. So it is with a computer without software. Software is the invisible and intangible driving force which causes the computer to work.

The CR8 (in some configurations) is in effect two computers since it has two processors ("brains"). Thus it has two bundles of software to co-ordinate and control its activities. These are known as Operating Systems. One of these would be CP/M or MP/M, and the other is called SCRIMP/M. Various varieties of these operating systems are used on the CR8, depending on the exact configuration more details appear later. CP/M is for single user systems and MP/M is for multiuser systems. Both are very popular and commonly found within the microcomputer industry, which means that a large variety of application programs are available for the CR8. Application programs or packages are those pieces of software which actually do something useful like word processing; operating systems are programs that coordinate and control the useful programs. The range of uses to which the CR8 can be put, of course, is limited only by the programmer's imagination. However, ready-made programs are already available for, for example, word processing (including spelling correction), report generation, data base management, sorting & merging, project planning, and many more - for more details, see sections 1.3 and 2.2.3.

# 1.2 CONFIGURATION OPTIONS - HARDWARE

The two basic types of CR8 - cabinet and workstation models - each come in a variety of forms. Furthermore, each of the models can be configured using the options described in section 1.2.1.

# Standard Features of the CR8 Cabinet Models

| Model No. | Description of Features Included                                                                                                                                                                                |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CR8/007/1 | 4-Unit cabinet (size: width 48 x height 17.7 x depth 55-cms) containing: o MP <sup>2</sup> board (8088 processor, Z80A Processor, 128K bytes RAM, Floppy Disk Interface, 2 V24 interfaces, Multibus interface). |

|           | o 5 Multibus slots                                                                                                                                                                                              |

|           | o Power Supply (150 watts)                                                                                                                                                                                      |

|           | o Fans                                                                                                                                                                                                          |

|           | o Disk drives - one of the options 11, 21 or 31.                                                                                                                                                                |

|           | o Facility to connect 1 terminal and 1 printer (options 40 to 49). Single user system.                                                                                                                          |

| CR8/007/4 | Four user version of the above. In addition it houses:                                                                                                                                                          |

|           | o 128K bytes extra RAM (option 93)                                                                                                                                                                              |

|           | o 1 SCI board (option 97)                                                                                                                                                                                       |

| - ;       | o Facility to connect up to 4 terminals and 2 printers in all (options 40 to 49)                                                                                                                                |

| Model No. | Description of Features Included - 1979 1989                                               |

|-----------|--------------------------------------------------------------------------------------------|

| CR8/007/8 | Eight user version of CR8/007/1. In addition it houses: o 256K bytes extra RAM (option 94) |

|           | o 2 SCI boards (option 97)                                                                 |

|           | o Facility to connect up to 8 terminals and two printers in all (options 40 to 49)         |

# Standard Features of the CR8 Integrated Workstation Models

| Model No. | Description of Features Included                                                                                                                                                        |  |  |  |  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| CR8/017/1 | Integrated Workstation (microcomputer and disks built into VDU with a 12" screen and detachable keyboard). The unicontains:  o MP <sup>2</sup> board (see description of Cabinet model) |  |  |  |  |

|           | o 8 Multibus slots (6 in older examples)                                                                                                                                                |  |  |  |  |

|           | o Power Supply (165 Watts)                                                                                                                                                              |  |  |  |  |

|           | o Fans                                                                                                                                                                                  |  |  |  |  |

|           | o Disk drives - one of the options 11, 21 or 31                                                                                                                                         |  |  |  |  |

|           | o Facility to connect one printer (Options 40 to 46)                                                                                                                                    |  |  |  |  |

| CR8/017/4 | Four user version of the above. In addition it houses:  o 128K bytes of extra RAM (option 93)                                                                                           |  |  |  |  |

|           | o One SCI board (option 97)                                                                                                                                                             |  |  |  |  |

|           | o Facility to connect up to 3 terminals and two printers (options 40 to 49)                                                                                                             |  |  |  |  |

# 1.2.1 Optional Extras

A list of CR8 optional extras is given below, followed by short descriptions of each one. This list was correct on 1st March, 83; new options are added from time to time - for instance, larger capacity disks are shortly to be announced.

| Option Number | Description 5 1/4 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                    |

|---------------|------------------------------------------------------------------------------------------|

| 01            | Single floppy drive, 5-1/4", 1 Mbyte (dual side, dual density)                           |

| 11            | Dual floppy drive, 5-1/4", 2 x 1 Mbyte (dual side, dual density)                         |

| 21            | 6.38 Mbyte Winchester disk + 1 floppy drive (opt-01) + Winchester disk controller board. |

| 31            | 12.76 Mbyte Winchester disk + 1 Floppy drive (Opt-01) + Winchester disk controller board |

| 40            | Matrix printer, 80 cps                                                                   |

| 41 A          | Matrix printer, 120 cps                                                                  |

| 41B           | Matrix printer, 200 cps                                                                  |

| 42A           | Daisy wheel printer, 40 cps (letter quality)                                             |

| 46A           | Tractor feeder for Opt-42A                                                               |

| 42B           | Daisy wheel printer 55 cps (letter quality)                                              |

| 42C           | Daisy wheel printer 35 cps (letter quality)                                              |

| 44B,C         | Double sheet feeder for Opt-42B,C                                                        |

| 45B,C         | Single sheet feeder for Opt-42B, C                                                       |

| 46B,C         | Tractor feeder for Opt-42B, C                                                            |

# CR8 USER GUIDE - INTRODUCTION

| Option Number | Description                                   |                                          |

|---------------|-----------------------------------------------|------------------------------------------|

| 48B           | CR5 Compass, X3.64 subset terminal            | English ch.                              |

|               | the second section of the second section is   | Danish ch.                               |

| 48C           | CR7 Comfort, X3.64 subset terminal            | English ch.                              |

|               |                                               | Danish ch.                               |

| 48D           | CR7 Comfort-X, direct X-Net                   | 10 10 10 10 10 10 10 10 10 10 10 10 10 1 |

|               | attachable X3.64 subset terminal              | English ch.                              |

|               |                                               | Danish ch.                               |

| 49            | ANSI X3.64 Compatible Terminal                |                                          |

|               | (Tandberg TDV)                                | English ch.                              |

|               |                                               | Danish ch.                               |

| 93            | 128K byte memory board                        |                                          |

| 94            | 256K byte memory board                        |                                          |

| 97            | SCI-board, 4K universal serial comm. I/F      |                                          |

|               | (V24/RS232, X21, current loop) incl. on       |                                          |

|               | board Z80A and 32K RAM.                       |                                          |

| o             | XMA, X-Net interface for MP-square            |                                          |

| 0             | MP-square incl. 8088, Z80, 2x64K RAM,         |                                          |

|               | floppy disk interface                         |                                          |

|               | 2xV24 and Multibus interface                  |                                          |

| 0             | CR8 Cabinet, 2U, incl. 5 Multibus slots,      |                                          |

|               | Power Supply (150W, 5V 20A, +12V 6A, -12V 1   | l.5A)                                    |

|               | and fan units. (W48cms (19"), H8.85 cms (2U)  |                                          |

|               | L55cms)                                       |                                          |

| 0             | CR8 Cabinet, 4U, incl. 5 Multibus slots,      |                                          |

|               | Power Supply 150W, 5V 20A, +12V 6A, -12V 1    | .5A)                                     |

|               | and fan units (W48 (19"), H17.7 (4U), L55cms. | )                                        |

#### CR8 USER GUIDE - INTRODUCTION

- o CR8 Cabinet, 6U, incl. 10 Multibus slots, one power supply (150W, 5V 20A, +12V 6A, -12V 1.5A) and fan units (W48 (19"), H26.5 (6U), L55)

- o CR8 Cabinet, 6U as above, but with two power supplies.

- o PAM Interface

- o Mathematics Co-processor for MP<sup>2</sup>

**Memory** Extra RAM can be added - 128, 256 or 512 Kbytes. This does not include memory on  $MP^2$  or SCI boards.

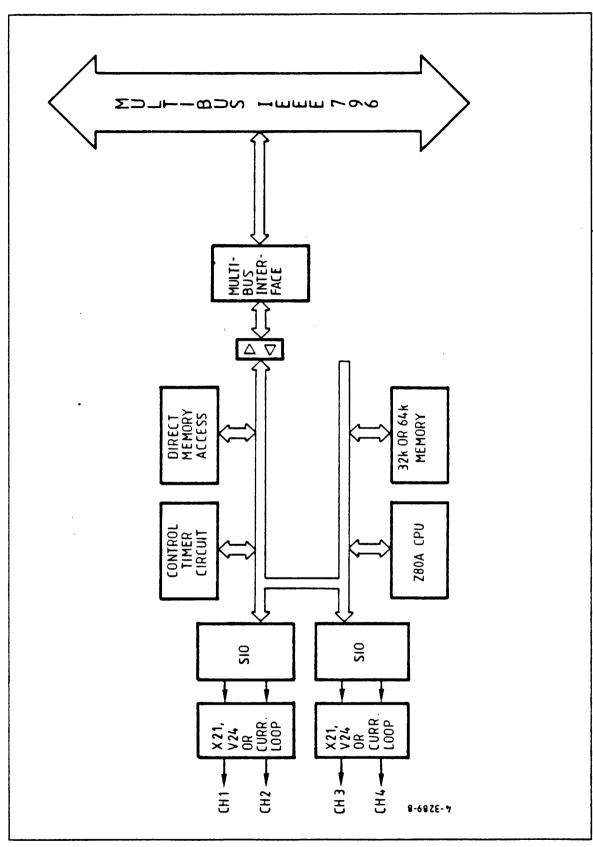

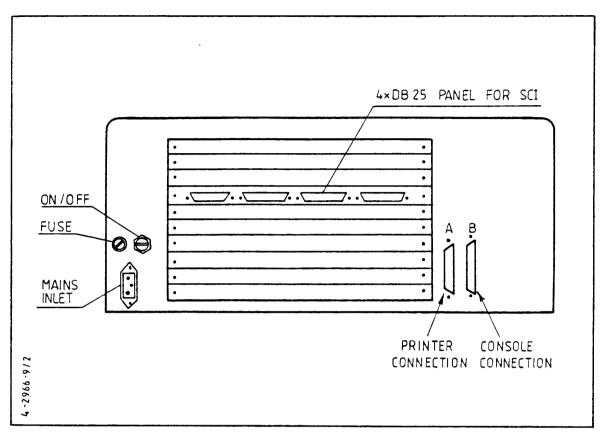

SCI Board This serial communications interface board can be set up to provide various interface types, (V24, X21, current loop) for communication with other devices such as terminals, printers or mainframes. Each board supports 4 interfaces which do not have to be of the same type. The SCI board houses its own Z80A microprocessor and 32K bytes of RAM.

Mathematics Co-processor In dual processor systems, the 8088 CPU may be replaced by a small board which houses both the 8088 plus an 8087 mathematics co-processor. It is used to speed up processing for applications requiring a lot of floating-point operations. It extends the normal instruction set and range of data types.

X-Net Interface Board X-Net is Chr. Rovsing A/S's local area network which is used for connecting various computing resources within, say, a factory or university campus. X-Net will connect to any manufacturer's equipment; however, this is simplified in the case of the XMA X-Net interface board, which precludes the use of the separate terminal adapter required by other manufacturer's terminals. Furthermore, the CR8 may take on a special role within X-Net as the X-Net Administrator (XNA). Please refer to X-Net Local Area Network System Description (ref. X-NET/RFM/0001) for further details. The X-Net interface board occupies one Multimodule slot in the MP<sup>2</sup> board.

PAM Interface. The Process Addressable Monitor is Chr. Rovsing's process monitoring & control system, which is used in many applications in for example, production supervision, energy management, and building security. It uses a single twisted pair cable for both data transmission & power distribution to the monitoring/control points, at distances of up to 4 kilometres. The CR8 Interface board handles up to 160 PAM interface modules, each of which in turn carries signals for up to 8 sensors or output devices. The interface board occupies one of the 3 available Multimodule slots on the MP<sup>2</sup> card.

Other Multimodule boards. The user may of course plug any Multimodule-compatible boards into the Multimodule slots. Many such boards are commercially available, for example serial or parallel programmable peripheral interfaces; alternatively the user may build his own.

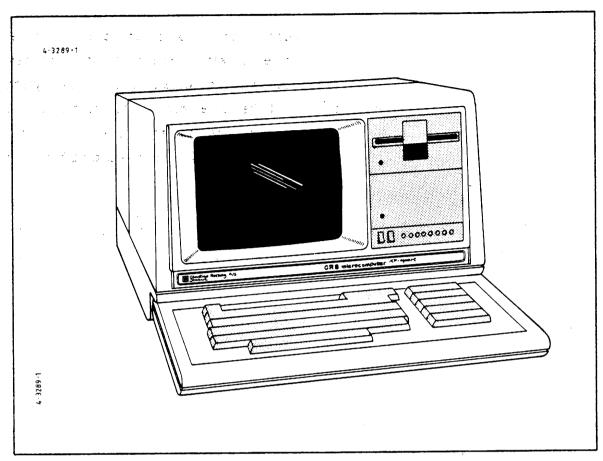

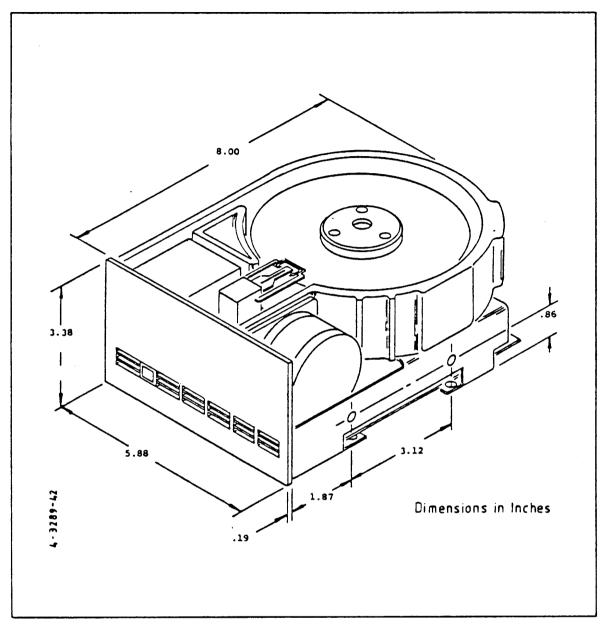

#### Disk Drives

All CR8 models (apart from the 2 Unit Cabinet Model) have space for two disk drives of standard size ((5.88 x 3.38 x 8.00 inches) or four in cases where the newer type of disk is installed which is only 1.69 inches high. The capacities quoted in the list of options are all unformatted capacities, i.e. a small proportion of these capacities are used by the system for 'housekeeping' and is not available to the user. Note that the Winchester disk requires a controller board whereas up to 2 floppy drives are catered for as standard within the  $MP^2$  board.

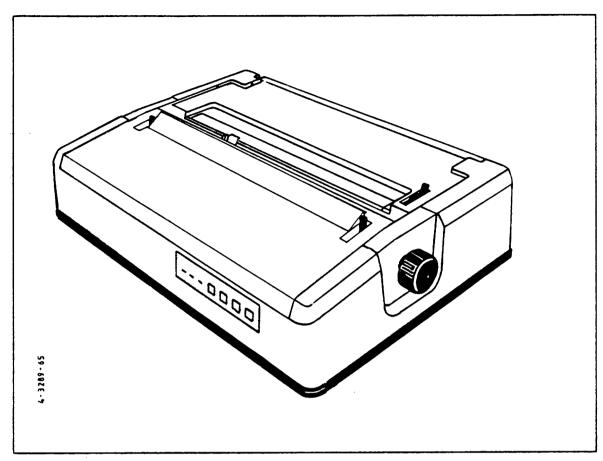

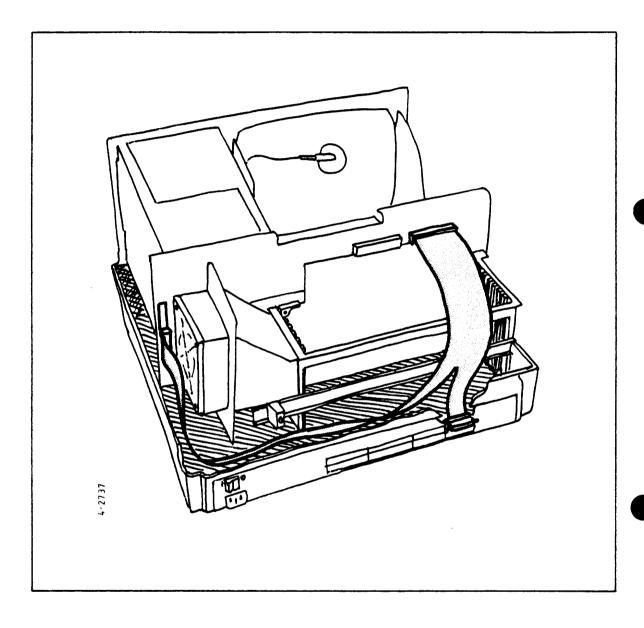

CLOSE-UP OF CR8 WORKSTATION SHOWING FLOPPY DISK ABOVE AND WINCHESTER BELOW

**VDU's** There are several VDU types that may be supplied with the CR8. One of these is included as the basis of the integrated workstation - in other words the VDU contains the disc drives, processors, etc. Any of the types supplied by CR may be used in multi-user CR8 systems. All are asynchronous terminals supporting ANSI X3.64. All have detachable keyboards and cursor addressing.

THE CR5 COMPASS TERMINAL

The three terminal types that do not contain disc drives etc. are the CR5 Compass, the CR7 Comfort, and the Tandberg TDV.

Note that any terminal to be used with the CR8 should support the ANSI X3.64 standard.

THE CR7 COMFORT TERMINAL

THE TANDBERG TDV TERMINAL

#### CR8 USER GUIDE - INTRODUCTION

**Printers** There are 2 main types of printer that may be supplied with the CR8 - dot matrix and daisy wheel.

The dot matrix printers used continuous stationery which is fed through by a tractor feed mechanism (engaging with the holes in the edges of the paper). These printers are intended for higher speed of output though the print quality is not as good as that of the daisy wheel printer. The dot-matrix printers come in three versions (which outwardly appear very similar):

# Option 40:

Speed: 80 characters per second. 80 columns of characters across the paper.

# Option 41A:

Speed: 120 characters per second. 132 columns of characters across the paper.

# Option 41B:

Speed: 200 characters per second. 132 columns of characters across the paper. This model has the option of running at half speed but with a higher print quality.

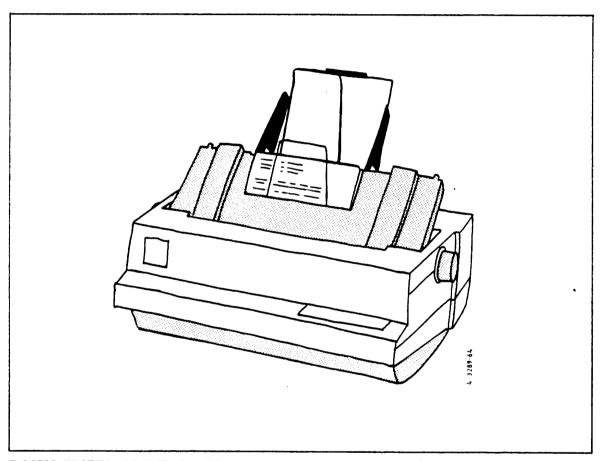

DOT-MATRIX PRINTER

The other type of printer that may be supplied with the CR8 is a daisy wheel printer. This is in effect an electric typewriter without a keyboard, so the print is of letter quality. It is intended for word processing applications. There is a choice of three adaptors - a tractor feed for continuous forms, a single sheet feeder, or a double sheet feeder. When the double sheet feeder is fitted, the user may select one of two paper styles when printing different parts of his document. This feature is particularly useful when the first page of a letter requires pre-printed headed paper whereas the continuation sheets use plain paper. It takes only few seconds to swap one adaptor for another.

DAISY-WHEEL PRINTER WITH SINGLE SHEET FEEDER (OPTION 42B, C)

DAISY-WHEEL PRINTER (OPT. 42A)

### 1.3 CONFIGURATION OPTIONS - SOFTWARE

The CR8 microcomputer supports a range of CP/M-based operating systems, as follows:-

|                | Systems using<br>Z80 Only  | Systems using both Z80 and 8088 |                               |  |

|----------------|----------------------------|---------------------------------|-------------------------------|--|

|                | Z80                        |                                 | 8088                          |  |

| Single<br>user | CP/M 2.2                   | SCRIMP/M                        | CP/M-86                       |  |

| Multi<br>User  | MP/M II (supports 4 users) | SCRIMP/M                        | MP/M-86<br>(supports 8 users) |  |

CP/M 2.2 and CP/M-86 are single user systems, suitable for dedicated use in small offices or industrial control applications. As "single user" systems, there is only one system console, and only one application program may be executing at any time.

MP/M II and MP/M-86 are multi-user, multi-programming systems. That is, they support a number of system consoles (interactive terminals) - up to 4 for MP/M II, 8 for MP/M-86, each console having full control of the system facilities. It is possible to run several programs simultaneously from one (in fact, any) terminal.

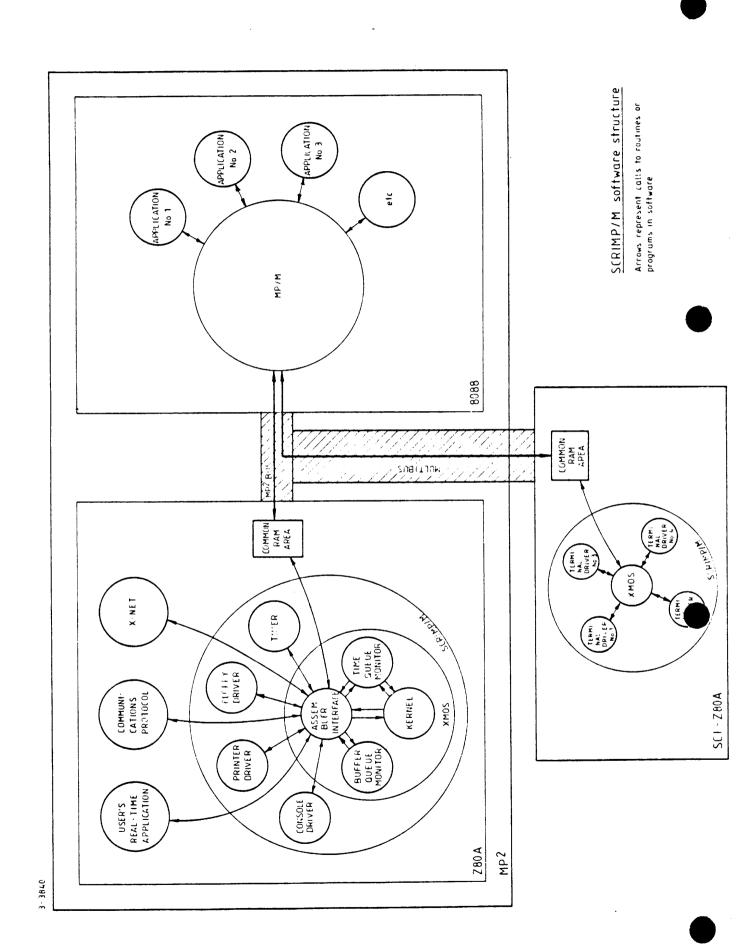

**SCRIMP/M** - Subset Comparable Real-time Implementation MP/M - is designed to handle the input/output functions both on the MP<sup>2</sup> processor board and SCI serial interface board (Z80A processors in both cases).

The following gives a glimpse of the applications packages for the CR8 which are available from Chr. Rovsing; more details of them are given in section 2. A full list of the available software is given at the end of this section; it does not include specialist software such as X-Net or protocol conversion.

Word-processing system for text entry and amendment. This optionally includes a mailing program to simplify the production of many letters that have sections in common, and a spelling checker.

Financial Modelling This is a sophisticated screen-oriented calculating package which may be programmed so that numeric fields in the display may be defined as mathematical functions of other fields. Thus the effects of changing a parameter are instantly displayed at all stages through the calculation. The package has many applications including: balance sheets, tax estimation, market share analysis, or statistics calculation in scientific experimentation.

Planning Tool This package is an aid to planning and handles report generation. It can also do calculations as part of its report. Its function is similar to the Financial Modelling package described above. The report is programmed in a very high-level English-like language.

File Sorting CR can provide a program for sorting files. It allows a wide variety of sorting keys and input and output formats, and includes facilities for merging up to 32 files.

A **Project Management** tool is available to aid in the management of small projects, using the technique of critical path analysis. The tradeoffs between time, money and manpower may be investigated: which activities may be delayed without delaying the whole project and which may not.

# Data Management Packages:

A data entry and retrieval system is available to facilitate the storage of information on user defined forms. Records may be selectively retrieved using a mask of the record to be matched; for example if the data were customer names and addresses, all customers called Smith or all customers in a certain town could be selected.

dBASE II is a simple data base management system that allows for a flexible user designed input form. All functions are specified in a command language that can be used interactively or combined into programs to be run as a job (for more complex report generation for example).

MDBS III is a comprehensive data base management system for the storage and retrieval of information on a large scale. Not only the data but the relationships between them are stored. Data can be retrieved using the English-like MDBS-QRS query language or via the user's own programs which can be in a variety of programming languages.

# **Programming Languages**

The CR8 will support the following programming language options: Basic (CBASIC interpreter or compiler), Pascal, Cobol, and Fortran. Z80 assembler and 8088 assembler come as standard with the CR8.

#### Communications

The CR8 may be provided with software to solve many communications problems, including emulators for IBM 2780 and 3274, Burroughs TC500, ICL CO3, NCR 801, X25 protocol and others.

#### **Others**

This brief overview of the available software is not complete, and will quickly become out of date since CR frequently release new software packages and options. Please contact the Business Group, CR Hotline for a current list. The address is at the front of this manual.

# SOME OF THE SOFTWARE AVAILABLE FOR THE CR8

Please consult CR for the latest list.

| Option No.                   | <u>Name</u>                                                                                                   | Z80A<br>single<br>user | Z80A<br>multi<br>user | 8088<br>single<br>user | 8088<br>multi<br>user |

|------------------------------|---------------------------------------------------------------------------------------------------------------|------------------------|-----------------------|------------------------|-----------------------|

| 200<br>201<br>202<br>203     | Operating Systems CP/M 86 MP/M 86 CP/M 2.2 MP/M II SCRIMP/M                                                   | X<br>X                 | X<br>X                | х                      | х                     |

| 60<br>61A<br>61B<br>62<br>63 | Languages FORTRAN C-BASIC BASIC compiler PASCAL MT+ (incl. SPP) COBOL                                         | X<br>X<br>X<br>X       | X<br>X<br>X<br>X      | X<br>X<br>X<br>X       | ×<br>×<br>×           |

| 64A<br>64B •<br>65           | Applications Word Processing, English Word Processing, Danish Proof Reading (English) Calculation & Financial | X<br>X<br>X            | X<br>X                |                        |                       |

| 67<br>69                     | Planning<br>Data Input<br>Sorting                                                                             | X<br>X<br>X            | X<br>X                | Х                      | X                     |

| 70<br>71A<br>71B<br>72       | Project Management<br>Mailing, English<br>Mailing, Danish<br>Indexing                                         | X<br>X<br>X            | X<br>X<br>X           | Х                      | х                     |

| 73<br>74<br>75               | MDBS III database<br>dBASE II<br>Finanssystem med budget-                                                     | X<br>X                 | X<br>X                |                        |                       |

| 76<br>77<br>78               | modul, Danish Debitorsystem, Danish Lagersystem, Danish Kreditorsystem med                                    | X<br>X<br>X            | X<br>X<br>X           | X<br>X<br>X            | X<br>X<br>X           |

| 79                           | Finansintegration, Danish<br>Kundeordresystem,<br>(forudsætter Debitor/                                       | Х                      | Х                     | X                      | х                     |

| 80<br>81                     | lager) Danish<br>Totalsystem incl. opt.75-79<br>Planning & Report                                             | X<br>X                 | X<br>X                | X<br>X                 | X<br>X                |

| 82A<br>82B                   | Generation, English Textproc. English Textproc. Danish                                                        | X<br>X<br>X            | X<br>X                | X<br>X                 | X<br>X                |

# 2. FEATURES OF THE CR8

# 2.1 Hardware

The CR8 was designed to be not merely a stand-alone desk-top computer, nor merely a multi-user microcomputer system but as the starting point for building communications systems, local networks, process control systems, and many other applications.

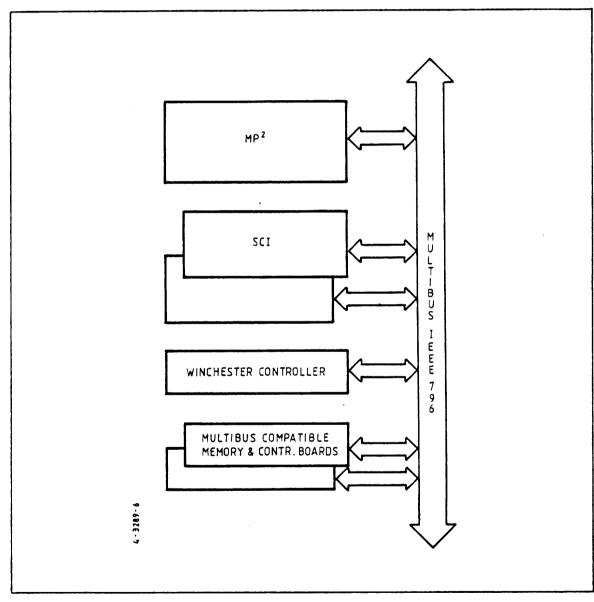

**CR8 FUNCTIONAL DIAGRAM**

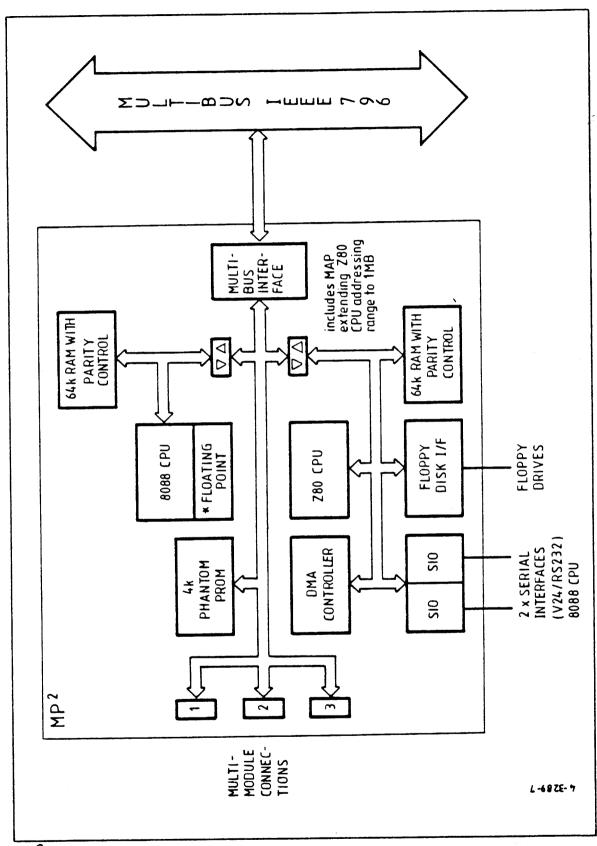

This expandability is in turn a function of various CR8 design features - in particular its MP<sup>2</sup> dual processor board, its System Communications Interface board, its Multimodule and Multibus compatibility, its 1-megabyte addressing range, and its CP/M, MP/M and SCRIMP/M operating systems.

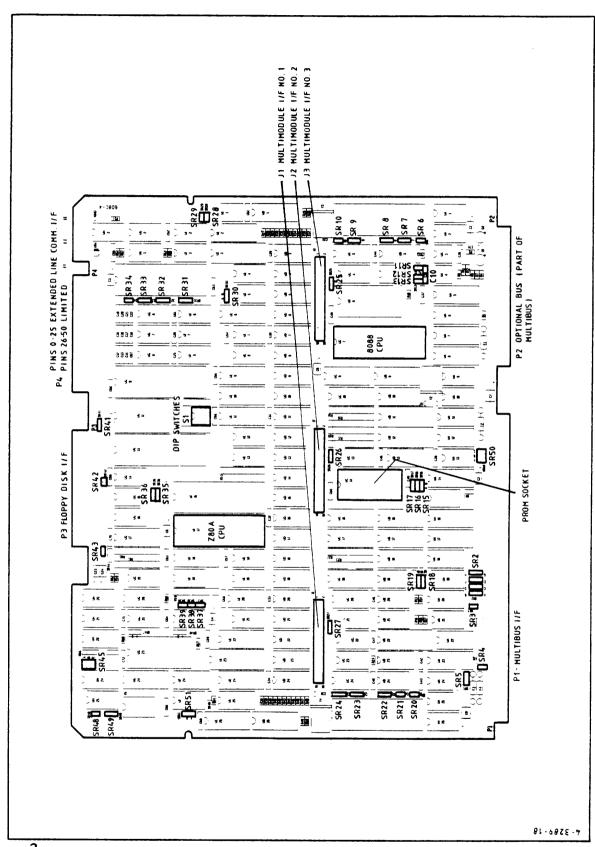

# 2.1.1 MP<sup>2</sup> Processor Board

This is the heart of the CR8 microcomputer. It is a highly integrated dual processor microcomputer system on one board. This board is mechanically and electrically compatible with the INTEL Multibus Interface (IEEE796 standard). This means that the user may combine any of hundreds of commercially available boards with the MP<sup>2</sup> in his CR8. Commercially available boards include parallel I/O, analog interfaces, memory, processors, hard disc interfaces, and so on. In addition the board has connectors for 3 standard INTEL iSBX Multimodule cards. Here again, many applications are catered for in the market place, or the user may design and make his own interface cards to that standard for his own special peripherals. Furthermore, you could use these Multimodule slots for CR's interface cards to the X-NET local area network or PAM monitor and control systems.

The two processors in the CR8 are the Zilog Z80A 8-bit cpu and the INTEL 8088 16 bit CPU. In simpler CR8 models using one processor, the Z80A does everything; in dual CPU versions, the user's applications generally run in the 8088 while the I/O overhead is off-loaded onto the Z80. This greatly improves the performance compared with single processor microcomputers, especially in the case of multi-user systems. Furthermore, a mathematics co-processor (INTEL 8087) may be added for further increase in performance for "number crunching" applications. (See section 5.3.3.6 for further details of this mathematics co-processor).

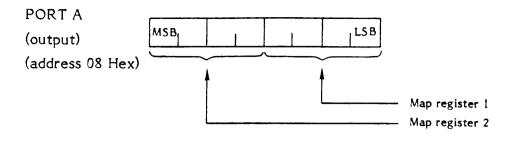

The MP<sup>2</sup> board houses 128 Kbyte of RAM, half of this is local memory for each processor though most is globally accessible by both processors. Note also that extra memory may be added on separate Multibus boards up to an overall maximum of 640 Kbytes. The addressing range of the Z80A, normally 64 Kbytes, has been extended to a megabyte in the MP<sup>2</sup> card by means of mapping registers. Thus both processors can address the full megabyte. The PROM area on the MP<sup>2</sup>, normally 4 or 8 Kbyte, may optionally be increased up to 64 Kbyte.

MP<sup>2</sup> FUNCTIONAL DIAGRAM

The MP<sup>2</sup> board also contains a built-in interface for two floppy disk drives.

Two serial interfaces are included on the MP<sup>2</sup>. One is a full modem interface, capable of synchronous or asynchronous operation with HDLC, SDLC, BSC, etc. The other is a limited interface for use with a terminal. In the integrated workstation this latter interface connects to the VDU section of the CR8 workstation. The signals and timing on both interfaces adhere to CCITT V24 recommendations.

# 2.1.2 System Communications Interface (SCI)

One feature of the CR8 which may be of interest particularly to systems houses is that by merely plugging in one or more of these SCI boards and loading new software from a floppy diskette, a simple CR8 desk-top computer is instantly converted to a sophisticated multi-processor communications device. With the help of the SCI it can now handle a variety of communications protocols such as X25, using software that has already been developed.

Similarly, a user of the simple single-user CR8 in, say, an accounting or word processing application can very simply upgrade to the multi-user model. By merely inserting this (same) SCI board and loading new software, the single-user system becomes a system with 6 serial channels, 4 of which are independently strap-selectable to X21/DTE, V24/DTE/DCE, or 20 mA current loop. By adding another SCI he can then add a further four serial channels. Thus in the maximum configuration, 10 terminals could be attached to the CR8 running the multi-user MP/M operating system, though generally the users would require a printer or two, leaving room for 9 or 8 terminals in all.

The SCI board fills one Multibus slot. It contains a Z80A microprocessor which runs software downloaded to it when the CR8 is booted. Certain details of the channels that it supports are programmable - baud rate, data length, number of stop bits per character and parity details. Other options are selected by switches or jumpers.

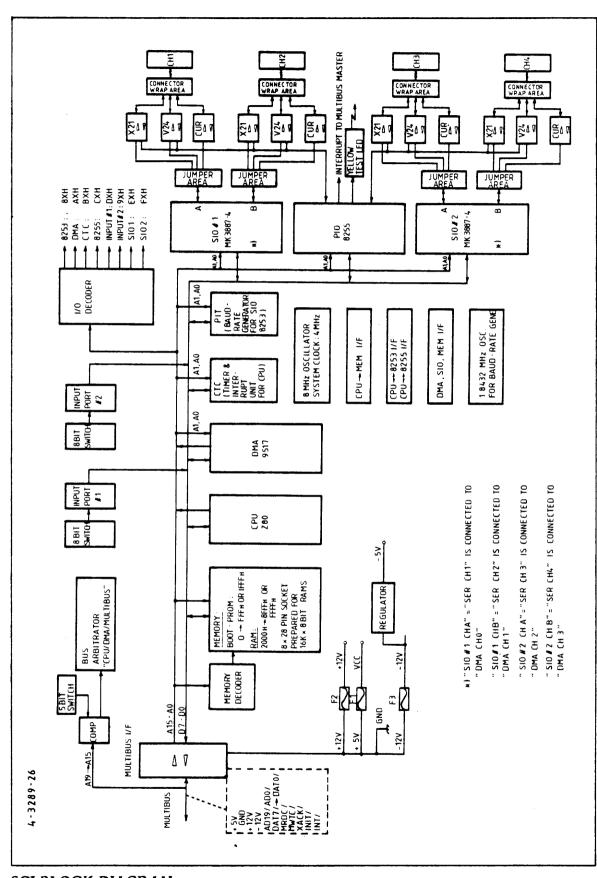

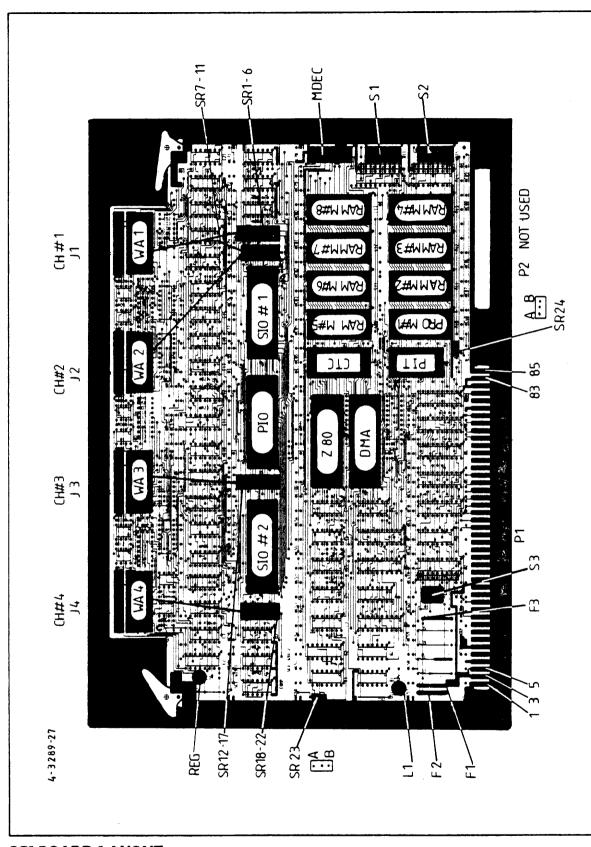

SCI FUNCTIONAL DIAGRAM

## 2.2 Software

## 2.2.1 Operating Systems

The merits of the CP/M and MP/M operating systems that are available on the CR8 have been described elsewhere in this and many other documents. Suffice it to say here that they are well-proven operating systems which are very widely used throughout the industry. Thousands of programs are available for them, and therefore, for the CR8.

What is different about the CR8 is the SCRIMP/M operating system, and the way that work normally done by CP/M or MP/M is offloaded to SCRIMP/M which runs on a separate processor. Thus the amount of useful work that can be done on the main processor with CP/M or MP/M is greatly increased compared with the more usual single processor/operating system combination. Furthermore, SCRIMP/M can handle real-time applications that simply could not be implemented under MP/M, since the latter slices time too slowly for fast real-time interaction. A process under MP/M might typically have the CPU for about 15 msec. A time slot of much less than this would lead to 'thrashing' (perpetual swapping with little useful work being done) since there is a fixed overhead of 2 or 3 msec which is required to perform the swap. Because SCRIMP/M is a lot simpler than MP/M - it does no file handling (such tasks can be handed over to CP/M or MP/M if required) - then it has a much smaller overhead when swapping between processes, so can afford to slice time into periods of around 2 or 3 msec with an overhead per swap of around 200 microseconds. Thus one could say it is very roughly 10 times more responsive than MP/M.

SCRIMP/M can be used either as an autonomous operating system, or it may be considered as a job running under CP/M or MP/M (and of course in turn has jobs running under itself). It should be stressed that SCRIMP/M is a multi-programming operating system which can manage several real time processes simultaneously. It is used 'internally' within the CR8 to handle the time-critical parts of device-driving (terminals, floppy discs etc.), and at the same time can be running real-time applications such as process control. In addition it is particularly suited to handling the lower levels of protocol in communications applications. SCRIMP/M generally runs in the Z80s - on the MP<sup>2</sup> board for level 3 X25 protocol, floppy disc

#### CR8 USER GUIDE - SOFTWARE FEATURES

driving, 2 serial lines, PAM, X-NET, and applications; and simultaneously on the SSCI board Z80 for 4 more serial lines, and X25 levels 1 and 2.

Finally, users of CR's CR80 minicomputer should note that device drivers and communication protocol software written for XMOS (which is the central part of SCRIMP/M) in the LTU (Line Termination Unit) can be transferred to the CR8 with only very minor modifications. Further details of SCRIMP/M are given in section 5.9.

### 2.2.2 Communications Software

The CR8 can be supplied with software that implements various protocols in order to allow communication between IBM mainframes and ANSI X3.64 terminals.

## 2.2.2.1 IBM 2780 Emulation

The CR8 may be supplied with emulation software so that it acts as an IBM 2780 Data Transmission Terminal. The card reading, card punching and printing operations of the IBM 2780 are simulated on the CR8 as disc read or write operations. The BSC (Binary Synchronous Communications) protocol used by the IBM 2780 is implemented by this software. Furthermore, the CR8 can of course be used to create or edit the JCL or data files needed for the IBM batch job.

#### 2.2.2.2 IBM 3274 Emulation

Software also exists to emulate IBM's 3274 end-to-end protocol which defines how an IBM mainframe communicates with a terminal through a Control Unit. The CR8 acts in the role of an IBM Control Unit. Several asynchronous terminals are connected via SCI boards within the CR8. This IBM terminal emulation can take place via CR's X-NET local area network if required.

## 2.2.3 Applications Software

The following applications packages have been 'tailored' for use on the CR8 and are available from CR; of course, there are hundreds of other programs available

for CP/M or MP/M from other suppliers. Furthermore CR's range of software is continuously being added to and updated. See the list at the end of section 1.

## 2.2.3.1 WORD PROCESSING PACKAGE (OPTION 64)

Virtually any typing task can be carried out with this powerful editor. The main features of the editing functions include: automatic buffering, on-screen text formatting, word-wrap, flexible find & replace commands, on-screen help, dynamic page break display, precise control of text format and hyphen help.

The part of the document being entered or corrected is always shown on the terminal screen, additions and corrections being immediately displayed. The text entry is accomplished merely by typing the desired text. Command functions such as cursor motion or deletion of text are immediately visible on the screen.

Automatic Disk Buffering (Temporary Automatic Storage). The size of a document is not limited by the amount RAM in the CR8, but by the disk capacity (approx. 200 A4 pages). The text is brought into RAM as required, with no operator intervention or concern.

On-Screen Formatting. Text is displayed on the screen as it will appear when printed, allowing review and correction before printing. On-screen text formatting is accomplished with the aid of these features: word-wrap, automatic margin setting, justification, variable line spacing, centring and paragraph re-form.

Word-wrap. Paragraphs may be entered at high speed without hitting the RETURN key. When a word exceeds the right margin, word-wrap automatically moves the whole word to the next line and justifies and re-displays the line just completed. The RETURN key is only used to indicate the end of a paragraph, blank line, or other points where a permanent line break is desired. The user need not pause to think about the end of the line, nor feel the necessity of looking up from the material being entered.

Flexible "Find" and "Replace" Commands. Searching operations can be done as many times as required, globally (on the entire document), on whole words only, ignoring case (upper or lower), and selectively (you will be asked whether replacement is to be performed in each instance).

On-Screen Help. During editing, a menu of commands will appear at the top of the screen, which may be withdrawn to give additional text display area. If a character is entered, after a short pause the menu automatically changes to show all commands that begin with that character. Furthermore the user can select one of 4 levels of help offering different amounts of detail.

Dynamic Page Breaks. Within certain limitations, the page breaks that will occour at printout are indicated on the screen during editing, and change appropriately in response to every insertion or deletion. Thus it is not necessary to print in order to review page layout or page break positions.

**Printing.** A useful feature of the printing function is that whilst one document is being printed, another can be edited - i.e. concurrent printing is provided. The print formatting features also include page formatting, pagination control, special effects, microspace justification and operator options.

Automatic Margin Setting, Justification, Line Spacing and Centring. With word-wrap in effect, each completed line is automatically adjusted to fit the left and right margins, justified (right-aligned) unless you selected ragged-right format, and optionally double or triple spaced. A line of text can be centred between the current left and right margins with a keystroke command.

Paragraph Re-form. The text from the cursor position to the end of the paragraph may be "re-formed" on command to change the margins or line spacing, to change from ragged right to justified or vice versa, or to clean up after alterations.

Hyphen Help. Text Master can identify desirable places to divide a word between lines with a hyphen. At each occurrence, the user may decide whether to hyphenate, and optionally adjust the hyphen position. Hyphen-help inserts temporary hyphens which do not print if moved to mid-line by later reforming.

Special Print Effects. In response to special characters embedded into the document, Word Star can <u>underline</u>, double strike, **boldface**, superscript, and subscript. These special characters that are used to invoke enhancements are displayed at the beginning and at the end of the affected text, during editing.

Type Ahead Buffer. This feature enables the user to type faster than the screen display can respond; the keyboard strokes are saved until they can be processed.

Scrolling. The document being created can be longer or wider than the VDU screen; the screen can be used as a movable "window" onto the text.

Column Mode. This feature is very useful for moving, copying or deleting columns of text and numbers. Column mode is particularly useful in creating and editing tables.

Screen Highlights. The CR8 uses reverse video to differentiate menus and special control characters from the main text being entered.

In addition to these standard features, four optional programs are available. The proof-reading and mailing options cannot be used "stand alone".

Mailing (Option 71). This is used to produce standard documents. It is designed to save a great deal of time with repetitive documents, standard form letters etc. Some examples are: - a report or proposal that goes to different organisations where standard text is used in a variety of situations adding different introductory material and arranged in different order; or where the name and address change, while the rest of the letter stays the same; and mailing lables, where everything changes except the format.

The Mailing program also makes it possible to chain several files during printout, with continuous page numbering, and to print both letters and envelopes from the same mailing list with a single command. The mailing program also has all the normal print functions available with the main word processing program. The one exception is that it cannot print a file while editing another.

Proof-reading (Option 65). The Proof-reading program is designed to check for spelling errors and any typing mistakes in a file. It does this by taking each word within the file and matching it to the words in its dictionary. In the event that the word isn't listed in the dictionary (or dictionaries), the program assumes the word is misspelled.

The program's dictionary contains over 20,000 words. However, it does not include all the words one might use, such as names of people, places, technical terms and obscure words. Thus it is bound to pitch these out as well as words that are genuinely misspelled. Dictionary entries may be added or removed, or whole new dictionaries may be created.

Data Input (Option 67) and Sorting (Option 69). These two word processing options are covered elsewhere (sections 2.2.3.5 & 2.2.3.3), since, unlike the other two, they can be used independently of the word processing package.

## 2.2.3.2 Calculation & Financial Planning.

This is a very flexible and generally-applicable "spreadsheet" program which can be used for report generation, complex calculations and cost planning. It is in fact a programmable program, in that the user can set it up to perform certain calculations (including conditional statements). The calculations may then be repeated using different parameters.

The user designs his own report or form - a large sheet of text and/or numbers. It can have up to 63 columns and 254 lines of entries (though the overall total is 600 entries), where an entry is a text string of up to 116 characters or a number of up to 16 significant figures (maximum  $\pm 10^{63}$ ). Entries can be defined as fixed text or numbers, or variables. In the latter case the value can be accepted by typing it in each time a new calculation is done or it can be extracted directly from a data file; alternatively it can be some mathematical function of other entries on the form. These mathematical functions can call any of the following built-in functions:

Addition, subtraction

Multiplication, division

Raising to a power

Sum of arguments

Number of values in argument list

Mean value

Maximum, minimum value

Logarithms (base e or 10)

Square root

Absolute value

Exponential function

Logical expressions (AND, OR, IF, etc.)

Integer value of

Table lookup

Net Present Value of cash returns at a given discount

ΡI

Trigonometric function (SIN, ASIN, etc.)

So, using these functions to do a calculation in stages, it is easy to see on the screen **how** the calculation was done - giving greater credibility to the final report! For large or complex calculations that do not fit onto the screen, it is possible to "roam" over the report so that the screen is used as a window onto a part of the large report. Furthermore, whole lines or columns of particular interest may be optionally "fixed" into the display so that these do not disappear when the display is scrolled.

The package is so flexible and powerful that it is impossible to give a comprehensive list of possible applications; however the following gives a taste of the possibilities:

Balance sheets & accounting generally

Tax estimation

Market share analysis

Statistic calculation in scientific experimentation such as analysis of variance, correlation.

Data storage and retrieval (especially where there is a lot of different "facts" relating to each item).

Any application that could be done slowly with a packet calculator and reams of paper.

# Planning & Report Generation Package (Option 81)

This package serves much the same function as the one just described (Option 66). The user does not create the report "on the screen" as he would with the other package. This package acts more like a traditional programming language, where a separate program is written which describes the desired report. It does however, have a few more mathematical accounting functions such as Internal rate of return, and four different types of depreciation calculation. It can also do a table lookup (a useful programming feature). It lacks the Linear Regression function that Option 66 has. This package is more flexible in the style and format of final report that it can generate; the 66 Option is more 'User Friendly' but gives a more limited range of reports as a result. The 81 Option could in fact be considered as an inexpensive alternative to Cobol.

# 2.2.3.3 FILE SORTING (Option 69)

This is a sort/merge package which can be used either as a stand-alone program, or in a form which in accessible from the user's own software (in BASIC, FORTRAN, COBOL or assembler). It can sort up to 32 input files and simultaneously merge these into a single output file. Alternatively, by merging one file into one file, use can be made of the extensive file conversion features without sorting.

The data format is very flexible. Files can be ASCII, binary, BCD (Cobol packed decimal), or EBCDIC. The user may even define his own collating sequence. It can handle signed and unsigned integers, or single and double precision floating point in both binary and character form. Moreover in the latter case the numbers can be in a variety of Exponential or floating point formats. Characters can have their case ignored or can even be read backwards.

The file format is equally flexible. The program supports records of up to 4096 characters, maximum 65K records per file. Records may be fixed length, variable length (with byte count or carriage-return-delimited). COBOL "relative" file type is also supported. Fields within a record may be of fixed length, or of variable length delimited by commas.

The keys for sorting can be up to 32 in number and each key's attributes may be independently defined (from the large variety of formats mentioned previously).

Another feature of this package is the "Exclude" and "Select" commands. By using these the user can, for example, ignore input data within a certain range of values, or data that is not in ASCII, or numbers less than a certain value, and so on. By this means the package can be used for data retrieval rather than (or as well as) sorting.

## 2.2.3.4 PROJECT MANAGEMENT (Option 70)

This package uses the technique of Critical Path Analysis as an aid in the management of small projects. The tradeoffs between time, manpower and money may be investigated. Parts of the project that constitute "bottlenecks" may be identified. That is, the program highlights those activities which if completed late will delay the whole project. Furthermore, it can generate a report on the project that can help to clarify what has to be done. Unlike many critical path analysis packages, this package is interactive and simple to use (and does not require a vast mainframe in which to run). So its aim is both to clarify the project to the manager and to produce easy-to-read reports on the project so the manager can more easily explain to others where the "vital links" in the project lie. It is intended for the analysis of small projects (or for a superficial view of a large project). Of course, it is ideal for use on a small subset of a large project.

As well as analysing the use of time, this package can estimate the costs of a project; also it can instantly re-estimate costs (or time) if the user specifies different starting conditions.

Calculations take place virtually instantaneously. The program can handle more than 100 activities in the project. Manpower is divided into nine different skill categories. The user can choose the time unit as being hours, days, weeks, months, quaters, or fiscal quarters; the longest project is 9999 units. It can allow for holidays, and the normal working week can be defined.

The printed output from the program consists of four reports. The first defines the initial parameters such as manpower-skill-types available and dates of public holidays. The second is a detailed description of each task into which the project has been divided in terms of timings and estimated cost. The third report is a timetable of the whole project with the critical path (and non-critical timings) clearly marked. The final report consists of a table showing job number, job name, duration, early and late timings, slack time, costs, prerequisite jobs, and number of men needed in each skill category. If all of these will not fit across the printer, the user can divide them into separate tables as required.

### 2.2.3.5 DATA BASE SYSTEMS FOR THE CR8

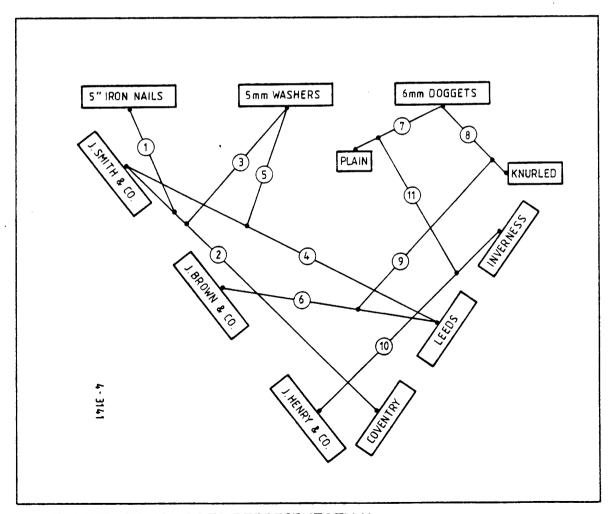

Three different packages are available from CR to cover what can loosely be termed data management - i.e. the storage and retrieval of large amounts of information in a flexible way. The three packages are: the simple data entry and retrieval system (Opt. 67), dBase II, and MDBS III. The third of these is by far the most sophisticated - it is the only one which is designed to handle many-to-many relationships. For instance, imagine a stock control application:

| ITEM                | SUPPLIER      | LOCATION  |

|---------------------|---------------|-----------|

| 5" iron nails       | J. Smith & Co | Coventry  |

| 5mm washers         | J. Smith & Co | Coventry  |

| 5mm washers         | J. Smith & Co | Leeds     |

| 6mm knurled doggets | J. Brown & Co | Leeds     |

| 6mm plain doggets   | J. Henry & Co | Inverness |

|                     |               |           |

## 2 DIMENSIONAL DATA REPRESENTATION

All 3 systems could store and retrieve information set out as above. Notice however that six fields have to be filled in order to record four facts, namely that 5mm washers can be bought from J. Smith in Coventry and Leeds. The duplication of "5mm washers" and J. Smith" is necessary because a 2-dimensional table such as this can only record one-to-one relationships (such as "5mm washers"/"Leeds" or "5mm washers"/"J. Smith & Co.") This duplication of information is both wasteful of disc space, and can cause much confusion. For example, J. Smith & Co. might stop selling 5mm washers, so the user deletes record 2 from the data base but forgets to delete record 3. In this simple example the duplication of information is very small; in real life it would be much greater, in fact to the point where a "table" format would be impractical for many applications.

Of the three systems, only MDBS is designed to cater for many-to-many relationships like this:

**MULTI-DIMENSIONAL DATA REPRESENTATION**

### CR8 USER GUIDE - SOFTWARE FEATURES

Our 15-entry table now can be represented by only 11 relationships. In a "real-world" example the saving would be much greater since the table might now have say 30 columns. One new item to be stocked would now require an extra 30 items to be recorded in the data base; in the multi-dimensional case only one new relationship (possibly more, but probably not as many as thirty) would need to be recorded. Furthermore, information retrieval can be made much more flexible and efficient since the database software can just 'follow the relationships'. For example (please refer to the diagram above), an enquirer might ask "Is there any point in going to Leeds?" The database system could follow the relationships 6, 9, and 8 for the reply "Yes, you could go to Browns & get knurled doggets", and relationships 4 and 5 for "You could also go to Smiths and get 5mm washers" What is more, the software would immediately know that there was nothing else in Leeds (since only 4 and 6 connect to it) so it need waste no further time in ploughing through its massive memory banks.

So, for applications where the data have few inter-relationships (or where such relationships are of no interest), or where the overall amount of data is fairly small, then the data entry system or dBase II would be the best choices. The data entry system is very convenient to use and has advanced data checking (on input). It is not very programmable in the sense that its only interaction with the user's own software is that it can make a file which can be accessed via CP/M or MP/M.

dBase II however is programmable "within itself" - that is the user can write data manipulation programs but he must use dBase II's special command language. For complete integration with a user's own software in Pascal, Cobol, etc. then the only choice is MDBS.

Further details on each of the 3 packages now follow.

# The Data Entry & Retrieval System (Option 67)

This is a data-handling program that allows the user to enter, retrieve, and update data in the form of text and/or numbers. It includes a program called with which the user can create the form to his own design. That form is then filled in (and filed on disc) using the main program.

The program is easy to use since a menu of commands is always displayed on the screen; there is also a Help facility to obtain further details without having to refer to the manual. The data entry package is compatible with the word processor (opt. 64) or can easily be incorporated into existing software written in e.g. BASIC, FORTRAN or COBOL.

The form generation program is very flexible in the style of form that it can handle. The form can be several pages long (depending on system memory size) or up to three pages wide. Furthermore, it is easy to insert built-in checks for each data field. For instance one can specify that when a datum is entered in a particular field it must be 8 letters or up to 6 letters or a number between 14 and 25 or whatever. One can even specify a list of valid entries for a field against which any datum entered must be checked. It is also possible to automatically fill certain fields by performing arithmetic on the contents of other fields, much as in the calculation package (opt. 66), or by copying across character strings from one field to another.

The program supports a batch mode whereby data is entered into a temporary file which can be checked - preferably by a different person - prior to updating the data file.

On the data retrieval side, the user can supply a "mask" to be compared with every record so that he could display, for example, the records for all customers in a given town, or all customers called Smith - in short all records that conform to the user-specified "template record". Alternatively the user can "leaf through" the whole data-base in user-supplied index-number order or in an unspecified order (which is more convenient for the CR8). There are of course facilities for printing out the selected information.

# Data Base Management System - dBASE II (Option 74)

This is rather more simple than MDBS. It supports a two-dimensional "table" structure of data. All communication with the system is via its own high-level language; any applications programs for the package must be written in that language. The user may interrogate the data base with a simple interactive dialogue, or combine commands (i.e. dBASEII language elements) into command files (programs) for the excecution of more complex procedures. The "form" is set up using an interative dialogue, then data is entered into the data base by filling in the blanks in the pre-defined form. The cursor automatically moves to the next box to be filled in. Simple data-type checking takes place during data entry and an audible warning given if data is of the wrong type.

One feature of the system is that it is possible to add data types or categories to an existing data base, without affecting programs already written - the new fields are simply ignored by the old programs.

dBASEII can generate reports from one or more databases; the report-writing software can do simple arithmetic also.

## Data Base Management System - MDBS III

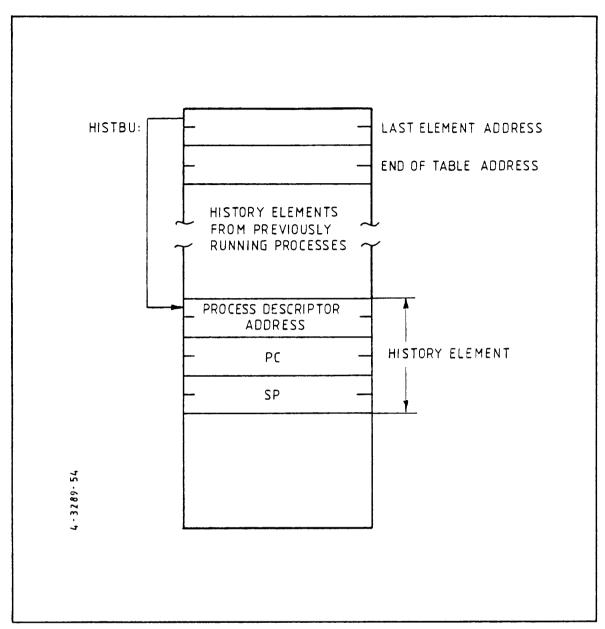

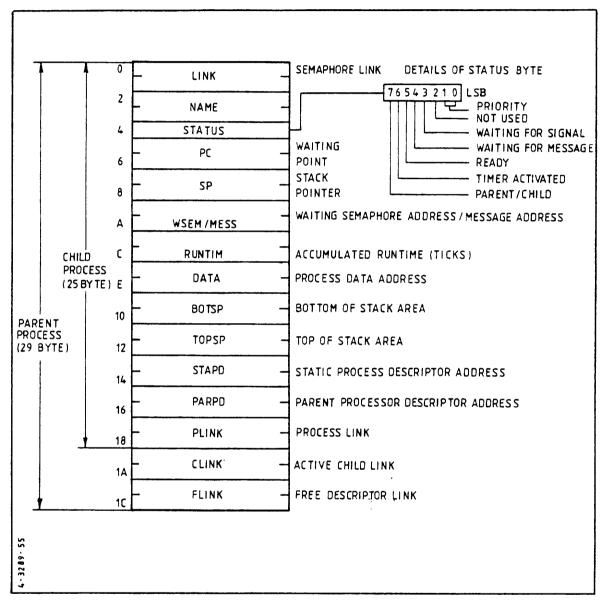

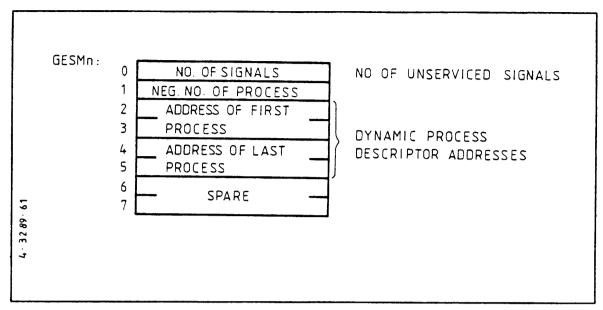

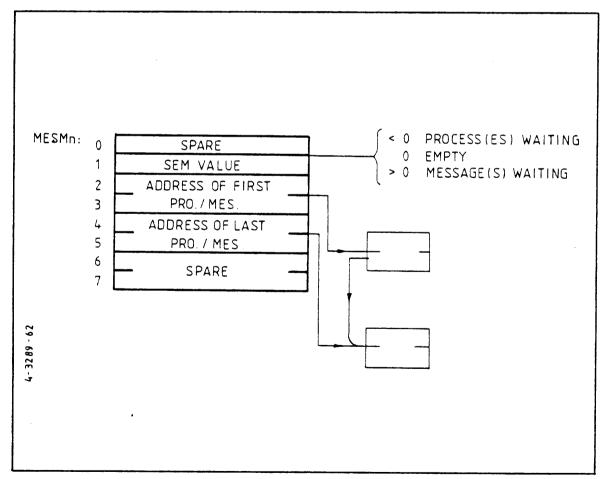

MDBS III (Micro Data Base System Version III) is a large and sophisticated data base management system which is available for the CR8. It is a **relational** data base system, that is, the relationships between data are recorded as well as the data themselves. These relationships can be one-to-many (like CODASYL or a trestructured disc filing system), one-to-one (pairs of related items) or many-to-many (just like the real world!) Furthermore, sets may be recursive - that is, data may be indirectly related to themselves.