# TOWARDS A SYSTEM ARCHITECTURE

Project report of the

EF-57 industrial research education program

Tue Bertelsen

## TABLE OF CONTENTS

| THE EF-57  | INDUSTRIAL RESEARCH                   | EDUCATION   | PROGRAM  | • |     | •   | • | . I-3         |

|------------|---------------------------------------|-------------|----------|---|-----|-----|---|---------------|

| 1.0        | Acknowledgements .                    |             |          |   | • • |     |   | . I-3         |

| 1.1        | Synopsis                              |             |          |   |     |     |   |               |

| 1.2        | Conclusions                           |             |          |   |     |     |   |               |

| 1.3        | Summary                               |             |          |   |     |     |   |               |

| 1.4        | Project History                       |             |          |   |     |     |   |               |

| 1.5        | Dansk summary                         |             |          |   |     |     |   |               |

|            |                                       |             |          | · |     | . • | · |               |

| PROJECT BA | ACKGROUND                             |             |          | • |     | •   | • | 11-1          |

| 2.0        | Introduction                          |             |          |   |     |     | • | II-1          |

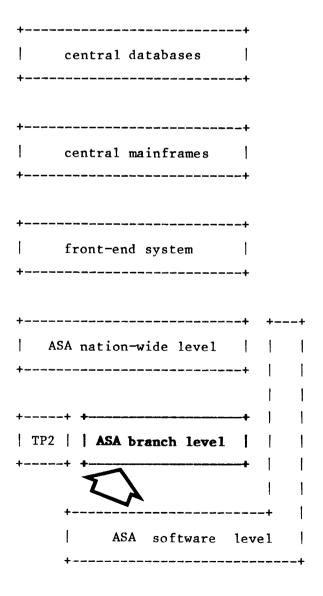

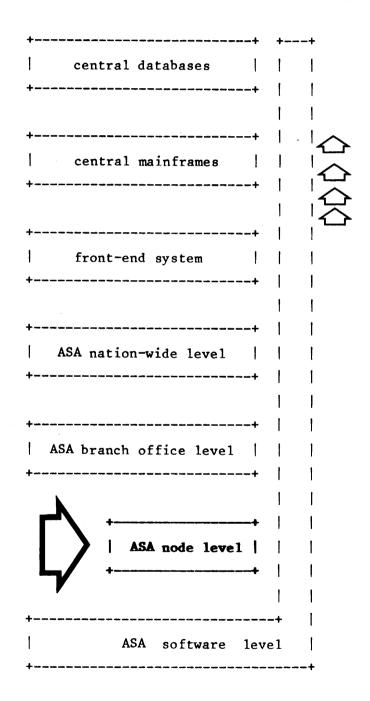

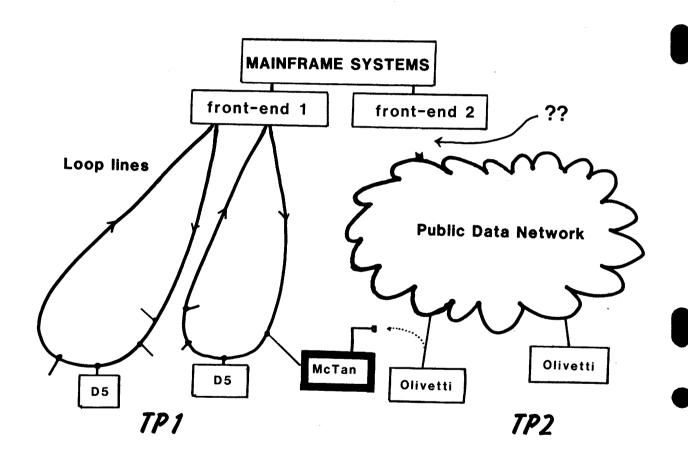

| 2.1        | TP2                                   |             |          | • |     |     |   | II <b>-</b> 3 |

| 2.2        | EF-57 Project Goal                    |             |          |   |     |     |   | II-6          |

| 2.3        | Long Term Goals and                   |             |          |   |     |     |   | II-8          |

| 2.4        | Confinements:                         |             |          |   |     |     |   | II-12         |

| 2.5        | Default assumptions                   |             |          |   |     |     |   | II-16         |

| 2.6        | Previous and curren                   |             |          |   |     |     |   | II-19         |

| 2.6        |                                       | •           |          |   |     |     |   | 11-19         |

| 2.6        | · · · · · · · · · · · · · · · · · · · |             |          |   |     |     |   | 11-19         |

| 2.6        |                                       |             |          |   |     |     |   | 11-20         |

| 2.6        |                                       |             |          |   |     |     |   | II-27         |

| 2.6        |                                       |             |          |   |     |     |   | 11-30         |

| 2.6        |                                       |             |          |   |     |     |   | 11-32         |

|            | .7 Slooo typical in                   | struction 1 | timing . | • |     |     | • | 11-33         |

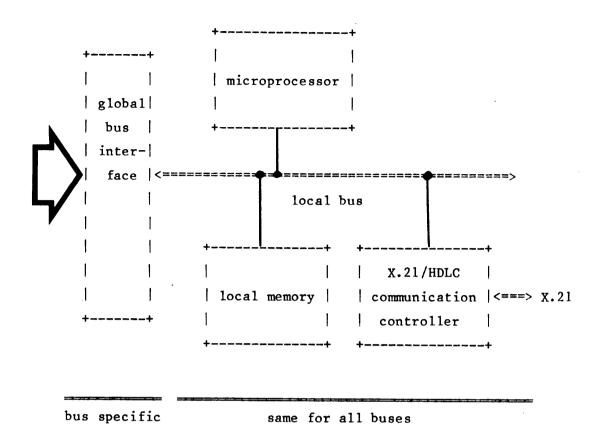

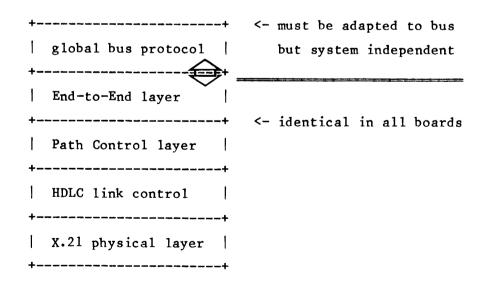

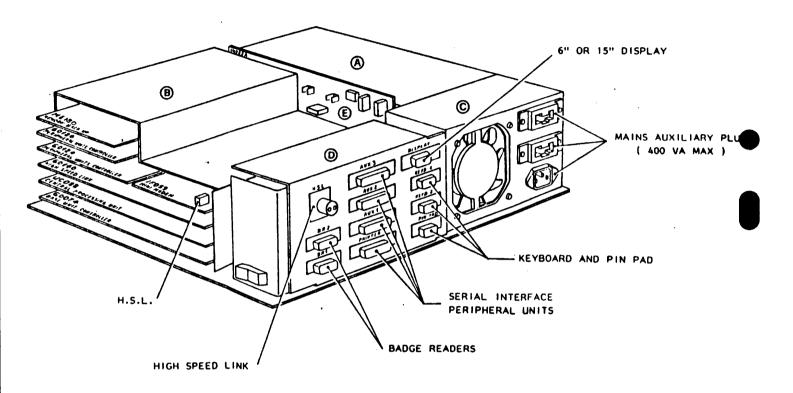

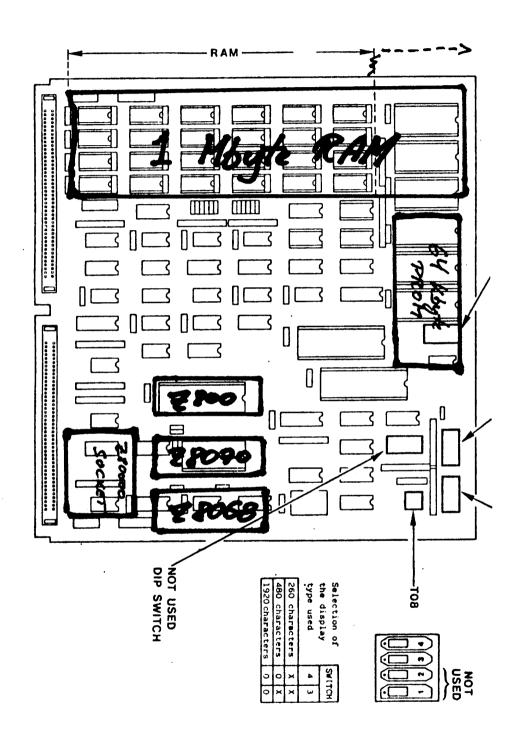

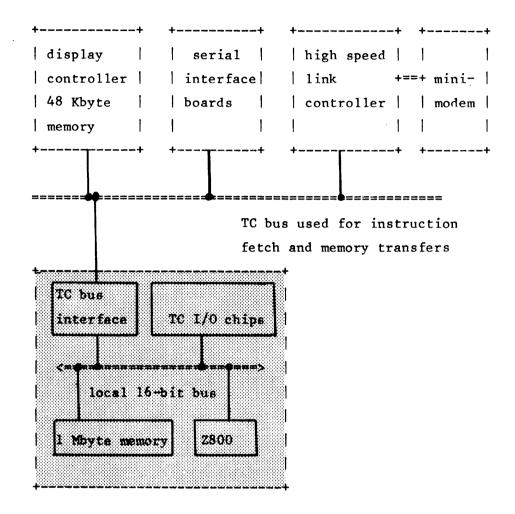

| 2.6        | .8 Sl000 circuit bo                   | arda        |          | • |     |     | • | 11-36         |

| 2.6        | .9 The high speed 1                   |             |          |   |     |     |   | 11-38         |

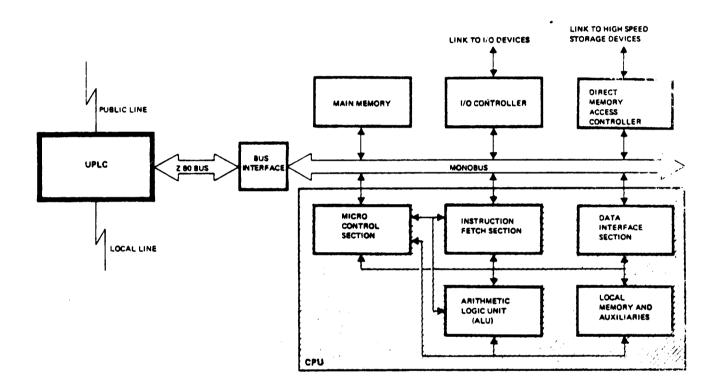

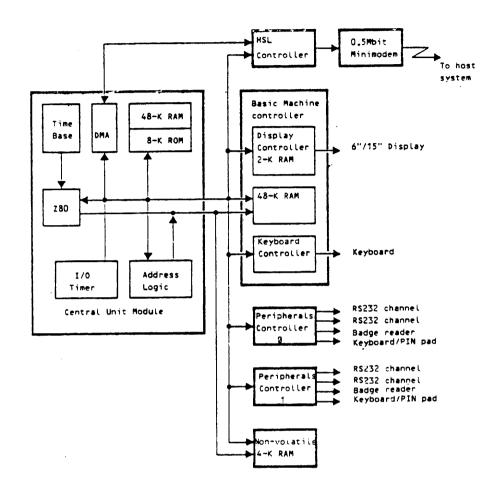

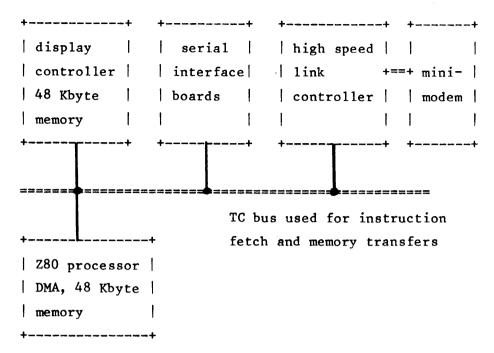

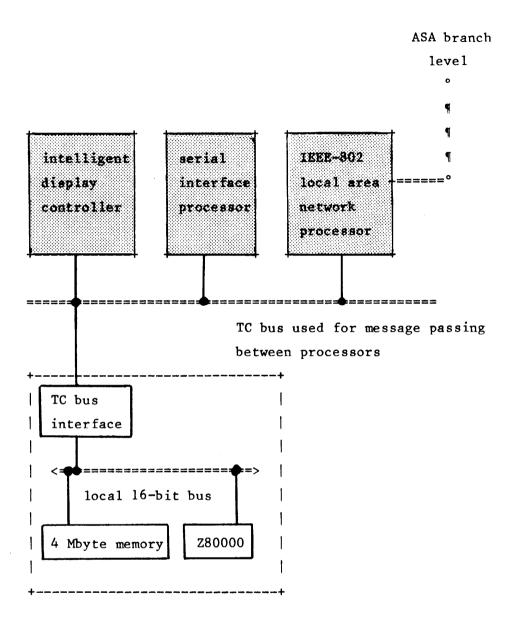

|            | .10 TP2 overall arch                  | itecture    |          |   |     |     | • | 11-39         |

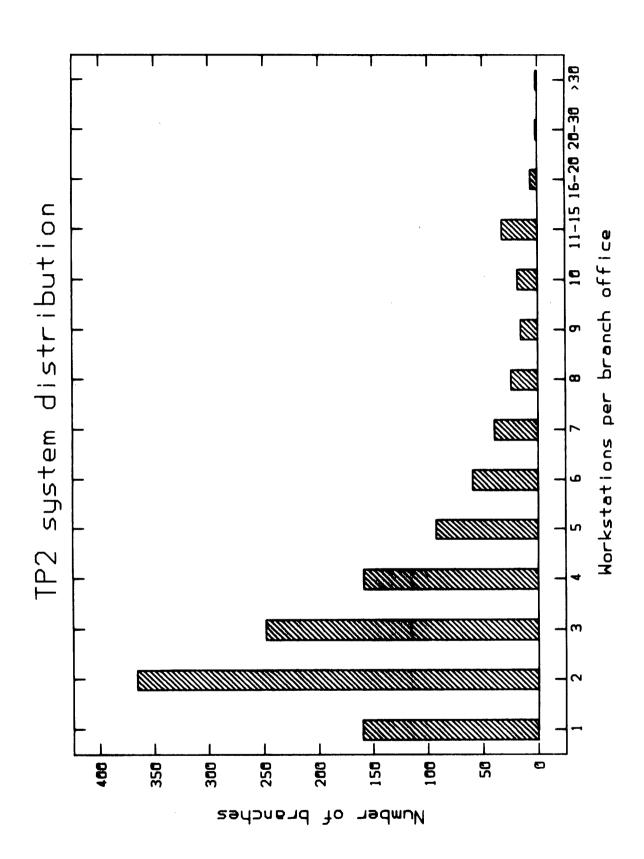

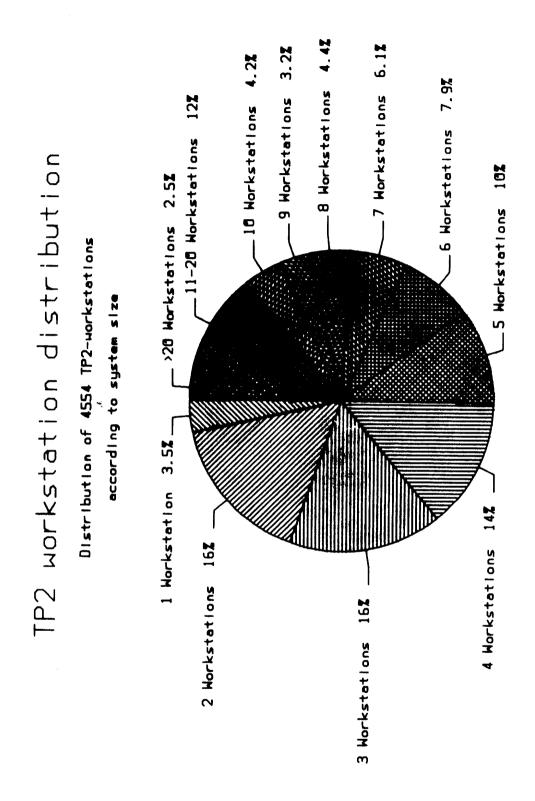

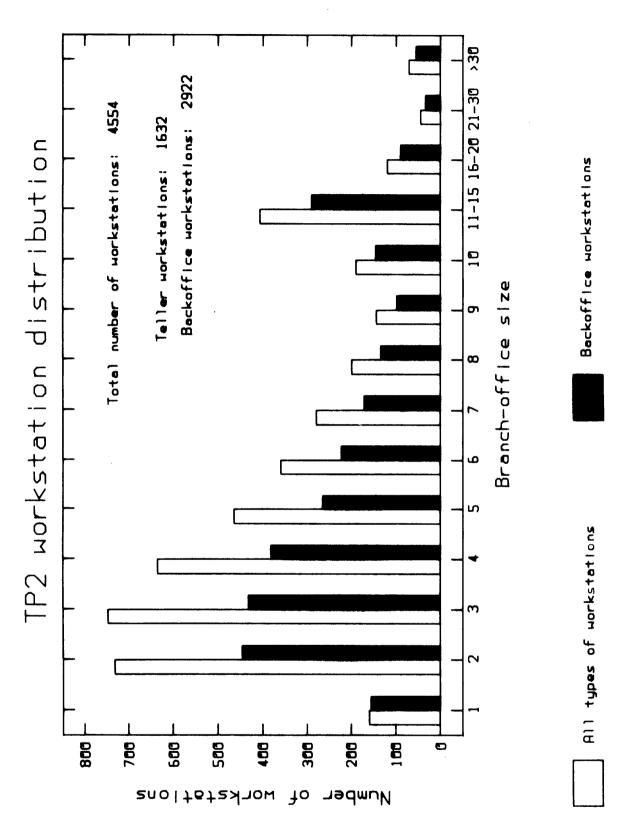

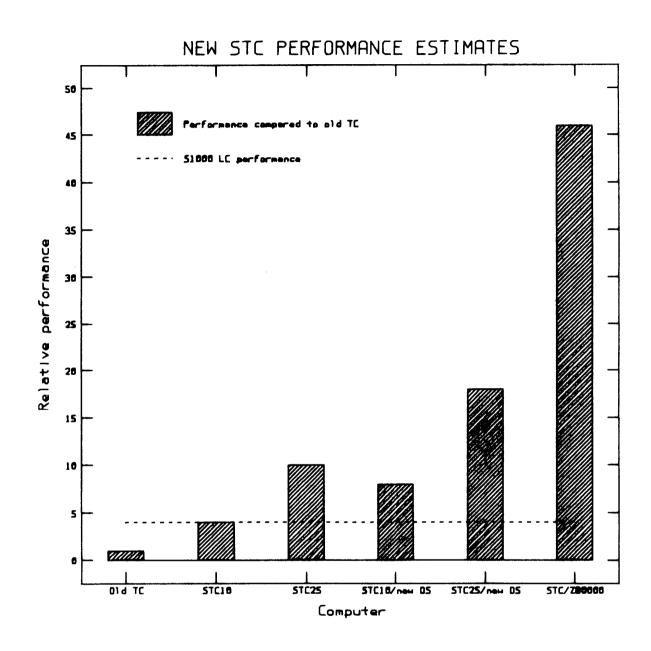

| 2.7        | TP2 performance pro                   |             |          |   |     |     |   | 11-52         |

| 2.8        | Conclusions                           |             |          |   |     |     |   | II-54         |

| 2.0        | Conclusions                           | • • • •     | • • • •  | • | • • | •   | • | 11-54         |

| TECHNOLOG  | Y IMPACT ON THE SAVI                  | NGS BANKS'  | Systems  |   |     |     | • | 111-1         |

| 3.0        | Introduction                          |             |          |   |     |     |   | III-1         |

| 3.1        | Basic concepts                        |             |          |   |     |     |   |               |

| 3.2        | Items to be covered                   |             |          |   |     |     |   | III-4         |

| 3.3        | Microprocessors                       |             |          |   |     |     |   | III-7         |

| 3.4        | Standard Microproce                   |             |          |   |     |     |   | III-11        |

| 3.5        | 8-bit microprocesso                   |             |          | - |     |     |   | III-12        |

| 3.5        | <del>-</del>                          |             |          |   | •   |     |   | III-13        |

| 3.5        |                                       |             |          | _ | •   |     |   | III-13        |

| 3.6        | 16-bit microprocess                   |             |          |   | • • |     |   | III-14        |

| 3.6        |                                       |             |          |   | • • |     |   | III-15        |

| 3.6        | 2 Intel 80186                         |             |          |   | • • |     |   | III-10        |

| 3.6        |                                       |             | -        |   |     |     |   |               |

| 3.6        |                                       |             |          |   |     |     |   |               |

| 3.6        |                                       |             |          |   |     |     |   |               |

| J. U.      | " DITTOR TOOMS                        |             |          | • |     |     | • |               |

| 3.7                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                | 111-23                                                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.8                                                                                                                        | 32-bit microprocessors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                | III <b>-2</b> 5                                                                                                                                                                           |

| 3.8.                                                                                                                       | 1 Extensions of existing architectures .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                | III-26                                                                                                                                                                                    |

| 3                                                                                                                          | 3.8.1.1 Motorola 68020                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                | 111-26                                                                                                                                                                                    |

| 3                                                                                                                          | 3.8.1.2 National Semiconductor 16032                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                | III <b>-</b> 26                                                                                                                                                                           |

| 3.8.                                                                                                                       | 2 Migrations from 16-bit processors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                | III-27                                                                                                                                                                                    |

|                                                                                                                            | 3.8.2.1 Intel 80386                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                |                                                                                                                                                                                           |

| 3                                                                                                                          | 3.8.2.2 Zilog Z80000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                | III-27                                                                                                                                                                                    |

| 3.8.                                                                                                                       | 3 New 32-bit designs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                | III-28                                                                                                                                                                                    |

| 3                                                                                                                          | 3.8.3.1 Bellmac-32A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                | III-29                                                                                                                                                                                    |

| 3                                                                                                                          | 3.8.3.2 HP 32-bit chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                | III-29                                                                                                                                                                                    |

| 3                                                                                                                          | 3.8.3.3 NCR/32 chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                | III-29                                                                                                                                                                                    |

| 3.8.                                                                                                                       | 4 New architectures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                | III-30                                                                                                                                                                                    |

| 3                                                                                                                          | 3.8.4.1 Intel iAPX 432                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                | III-30                                                                                                                                                                                    |

| 3.8.                                                                                                                       | 5 32-bit microprocessor applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                | III-31                                                                                                                                                                                    |

| 3.9                                                                                                                        | Support circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                | III-32                                                                                                                                                                                    |

|                                                                                                                            | 1 I/O circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |                                                                                                                                                                                           |

|                                                                                                                            | 2 Coprocessors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |                                                                                                                                                                                           |

| 3.10                                                                                                                       | Memories                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                | III-35                                                                                                                                                                                    |

| 3.11                                                                                                                       | Peripheral components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                | III-36                                                                                                                                                                                    |

| 3.11                                                                                                                       | .1 Floppy disks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                | III <b>-</b> 36                                                                                                                                                                           |

| 3.11                                                                                                                       | .2 Hard disks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                | III-38                                                                                                                                                                                    |

| 3.11                                                                                                                       | .3 Cartridge tapes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                | III-39                                                                                                                                                                                    |

|                                                                                                                            | Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                |                                                                                                                                                                                           |

|                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |                                                                                                                                                                                           |

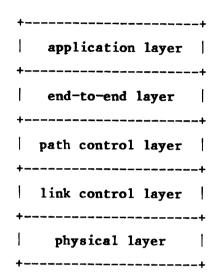

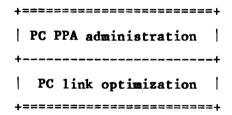

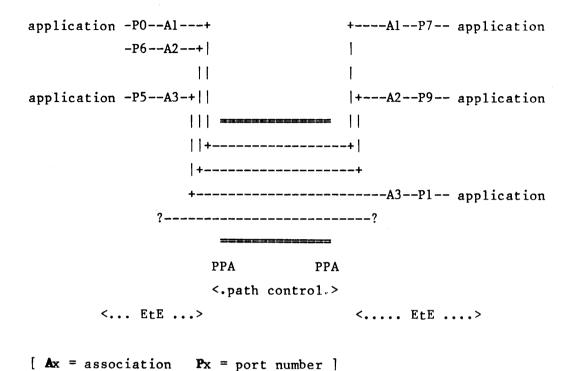

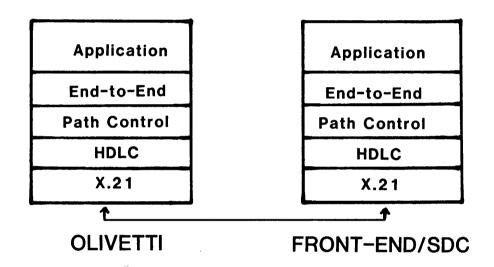

| ARCHITECTU                                                                                                                 | JRAL ELEMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                | IV-1                                                                                                                                                                                      |

| 4.0                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |                                                                                                                                                                                           |

| 4.0                                                                                                                        | introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                | IV-1                                                                                                                                                                                      |

| 4.0                                                                                                                        | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                | IV-1<br>IV-2                                                                                                                                                                              |

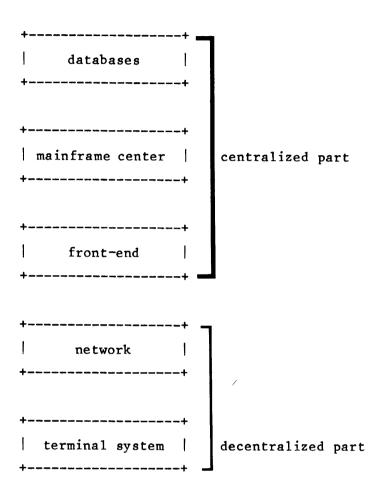

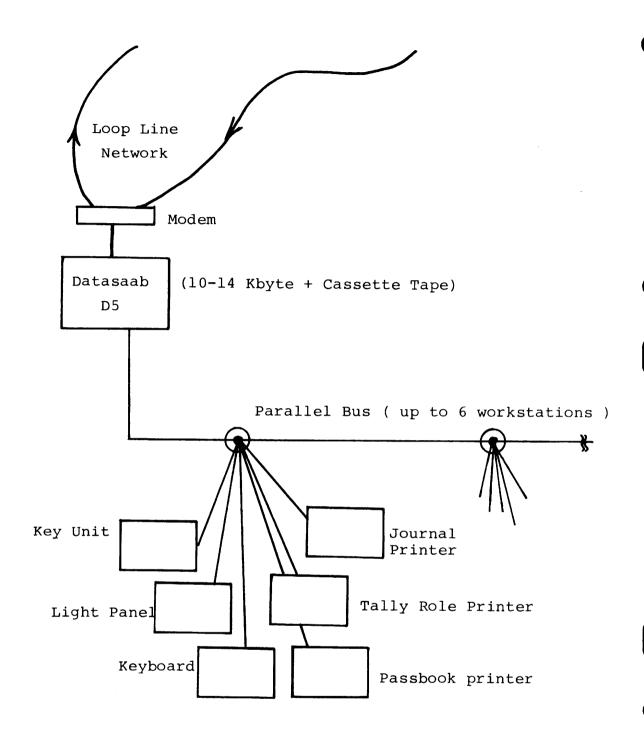

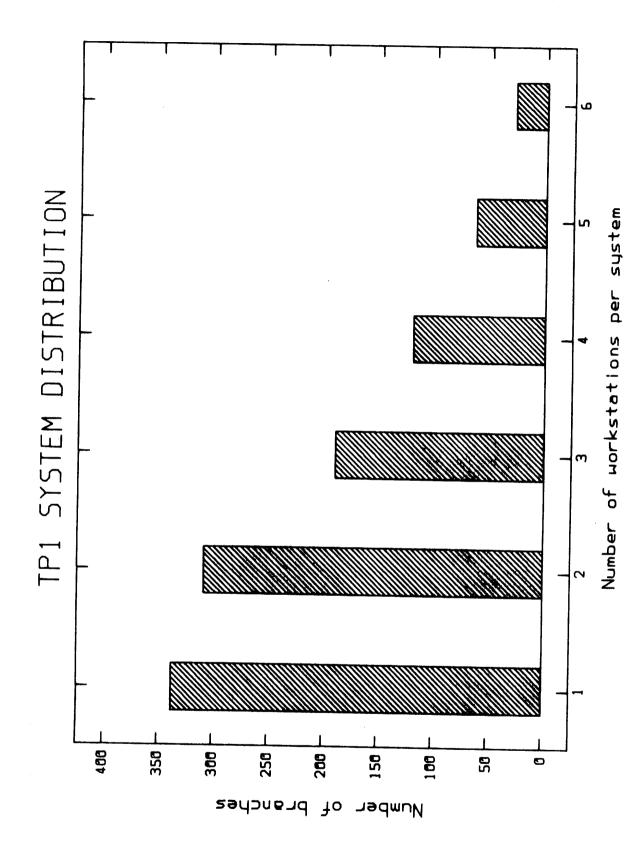

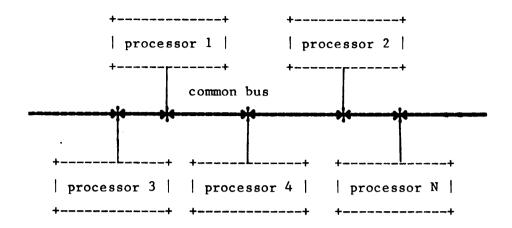

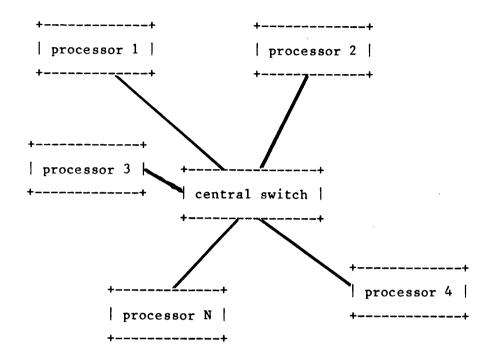

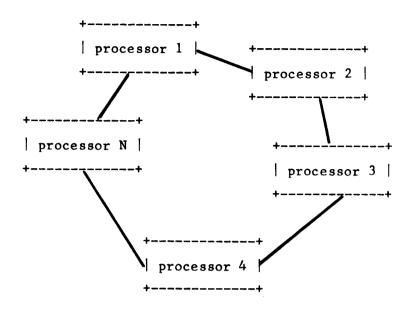

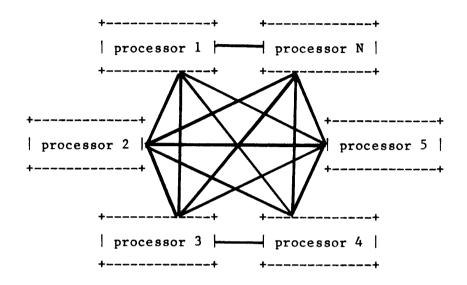

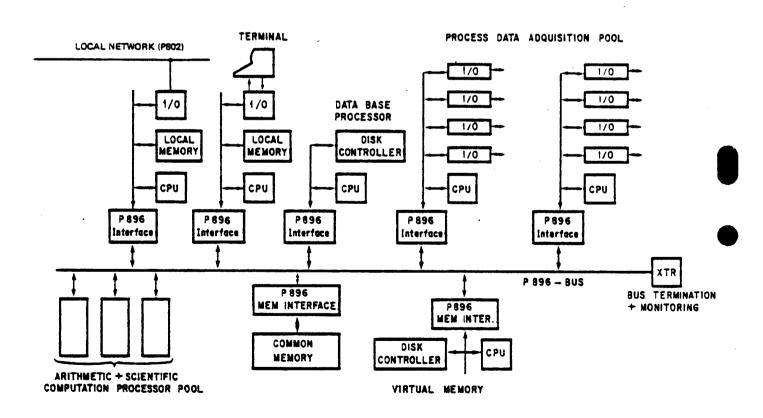

| 4.1                                                                                                                        | System architectures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                |                                                                                                                                                                                           |