# PROFESSIONAL COMPUTER

#### PREFACE

This document is the Standard Maintenance (STD) Manual for the Professional Computer. It is organized in accordance with the approved STD outline established at the Field/Home Office Publications meetings conducted on September 14th and 15th, 1982. The scope of this manual reflects the type of maintenance philosophy selected for this product (swap unit, printed circuit assembly, chip level or any combination thereof).

The purpose of this manual is to provide the Wang-trained Customer Engineer (CE) with instructions to operate, troubleshoot and repair the Professional Computer. It will be updated on a regular schedule.

## Second Edition (Sept 1983)

This edition of the Professional Computer STD manual obsoletes document(s) no. 729-1190-A and 729-1190-Al. The material in this document may only be used for the purpose stated in the Preface. Updates and/or changes to this document will be published as Product Service Notices (PSN's) or subsequent editions.

This document is the property of Wang Laboratories, Inc. All information contained herein is considered company proprietary, and its use is restricted solely for the purpose of assisting the Wang-trained CE in servicing this Wang product. Reproduction of all or any part of this document is prohibited without the prior consent of Wang Laboratories, Inc.

© Copyright WANG Labs., Inc. 1983

#### WARNING

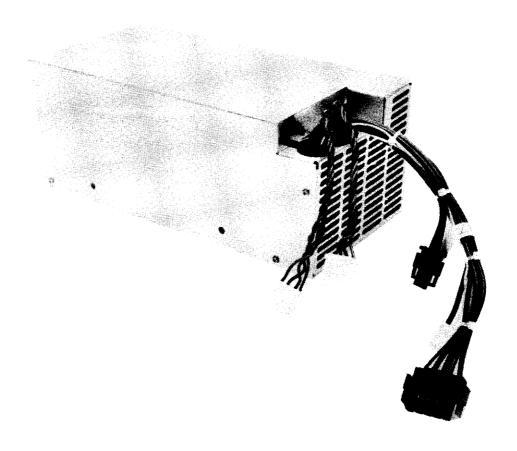

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\* \* DO NOT OPEN THE SWITCHING POWER SUPPLY UNDER ANY \* CIRCUMSTANCE. EXTREMELY DANGEROUS VOLTAGE AND CURRENT LEVELS (IN EXCESS OF 300 VOLTS DC AND UN-LIMITED CURRENT) ARE PRESENT WITHIN THE POWER SUPPLY. DO NOT ATTEMPT TO REPAIR THE SWITCHING POWER \* SUPPLY; IT IS FIELD REPLACEABLE ONLY. AFTER POWERING THE UNIT DOWN AND DISCONNECTING THE AC \* POWER PLUG FROM THE WALL OUTLET, ALLOW ONE MINUTE BEFORE REMOVING THE POWER SUPPLY TO PROVIDE ADEQUATE TIME FOR ANY RESIDUAL VOLTAGE TO DRAIN THROUGH THE \* \* BLEEDER RESISTORS.

# TABLE OF CONTENTS

| CHAPTER A                                                                                                                                                                            | ND TITLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | PAGE                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                      | CHAPTER 1<br>INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                     |

| 1.1 1.2 1.3 1.3.1 1.3.1.1 1.3.1.2 1.3.1.3 1.3.2 1.3.2.1 1.3.2.2 1.3.2.3 1.3.2.4 1.3.2.5 1.3.2.6 1.3.2.6 1.3.2.7 1.3.2.8 1.3.2.9 1.3.2.10 1.3.2.11 1.3.2.12 1.3.2.13 1.3.2.14 1.4 1.5 | APPLICABLE DOCUMENTATION SYSTEM DESCRIPTION Standard Equipment Supplied Electronics Enclosure (PC-001) Low-Profile Universal Keyboard (UNI/KBD-xx) Floppy Diskette Drive OPTIONS Monochrome Display (PC-PM004) Character Display Adapter (PC-PM001) Graphics Display Adapter (PC-PM002) Color and Graphics Display Adapter (PC-PM003) Memory Expansion Cards Remote Communications (PC-PM040) Local Communications (PC-PM041) CP/M-80 Emulation Board (PC-PM050) 10MB Winchester Disk Drive And Adapter Board (PC-PM021) 20-CPS Daisy Printer (PC-PM011) 80-CPS Matrix Printer (PC-PM010) Monitor Clamp and Arm (PC-AC001) System Unit Clamp (PC-AC002) Additional Floppy Diskette Drive (PC-PM020) SYSTEM CONFIGURATIONS SYSTEM SPECIFICATIONS | 1-2<br>1-5<br>1-5<br>1-6<br>1-6<br>1-7<br>1-7<br>1-7<br>1-7<br>1-8<br>1-8<br>1-8<br>1-8<br>1-9<br>1-9<br>1-9<br>1-9<br>1-10<br>1-10 |

|                                                                                                                                                                                      | CHAPTER 2<br>THEORY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                     |

| 2.1<br>2.2<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>2.2.5<br>2.2.6<br>2.2.7<br>2.2.8<br>2.2.8.1                                                                                        | INTRODUCTION  SYSTEM FUNCTIONAL DESCRIPTION  8221 CPU Board  SPS200 Power Supply  8237 Motherboard  360K Floppy Drive  Medium Resolution Character Generator (8243/8343)  Low-Profile Serial Keyboard  Wang Monochrome Monitor  Option Boards  10M Byte Winchester Controller (8225A) and Disk Drive                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-1<br>2-1<br>2-3<br>2-3<br>2-3<br>2-4<br>2-4<br>2-5<br>2-5                                                                         |

#### TABLE OF CONTENTS

| CHAPTER      | AND TITLE                                          | PAGE         |

|--------------|----------------------------------------------------|--------------|

|              | CHAPTER 2                                          |              |

|              | THEORY (Cont'd)                                    |              |

| 2.2.8.2      | 8233 Medium Resolution Graphics Generator          | 2-6          |

| 2.2.8.3      | 8242 Expanded Memory Board                         |              |

| 2.2.8.4      | 8248 CP/M-80 Emulator                              | 2-6          |

| 2.2.8.5      | 8222 Low Resolution Board                          | 2-6          |

| 2.2.8.6      | Remote Communication Controller (8232)             |              |

| 2.2.8.7      | Local Communications Option                        |              |

| 2.2.9        | EXTERNAL OPTIONS                                   | 2-7          |

| 2.2.9.1      | Printers                                           | 2-7          |

| 2.2.9.2      | Wangnet (Modems)                                   |              |

| 2.2.9.3      | Video Monitors and Televisions                     |              |

| 2.2.9.4      | Async Modem                                        |              |

| 2.3          | 8221 CPU/SYSTEM BOARD THEORY OF OPERATION          | 2-8          |

| 2.3.1        | CPU Processor Theory                               |              |

| 2.3.1.1      | 8086/8087 Co-processors                            |              |

| 2.3.1.2      | 8284A Clock Generator and Wait State Logic         |              |

| 2.3.1.3      | DMA Bus Acquisition Logic                          |              |

| 2.3.1.4      | DMA Controller Programming                         |              |

| 2.3.1.5      | 8288 Bus Controller and System Bus                 | 2-14         |

| 2.3.2        | SYSTEM BOARD THEORY                                | 2-17         |

| 2.3.2.1      | System Bus Buffering                               | 2-17         |

| 2.3.2.2      | RAM Control Logic and Address Mux                  | 2-17         |

| 2.3.2.3      | I/O Chip Select Decode and 'SAD'                   |              |

| 2.3.2.4      | 9517A DMA Controller                               | 2-20         |

| 2.3.2.5      | 8235-5 Programmable Interval Timer                 |              |

| 2.3.2.6      | 8259A Programmable Interrupt Controller            |              |

| 2.3.2.7      | 6402 UART                                          |              |

| 2.3.2.8      | 2661 Extended Programmable Communication Interface |              |

| 2.3.2.9      | Floppy Disk Controller                             |              |

| 2.3.2.10     | 111111111111111111111111111111111111111            |              |

| 2.3.2.11     |                                                    |              |

| 2.4          | SPS200 SWITCHING POWER SUPPLY                      |              |

| 2.5          | 8237 MOTHERBOARD                                   |              |

| 2.6          | 360K BYTE FLOPPY DRIVE                             |              |

| 2.7<br>2.7.1 | MEDIUM RESOLUTION CHARACTER GENERATOR (8243/8343)  |              |

| 2.7.1        | Medium Resolution Board Overview                   | 2-30         |

| 2.8          | LOW-PROFILE SERIAL KEYBOARD                        |              |

| 2.8.1        | Keyboard Overview                                  |              |

| 2.8.2        |                                                    | 2-35         |

| 2.9          | Keyboard Theory Of Operation                       | 2-39         |

| 2.10         | OPTION BOARDS                                      | 2-41         |

| 2.10.1       | Winchester Controller                              | 2-43<br>2-43 |

| 2.10.1       | Expanded Memory Board                              | 2-43         |

|              |                                                    | 40           |

| CHAPTER AN                                                                                                                                                                                                                           | ND TITLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | PAGE                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                      | CHAPTER 2 THEORY (Cont'd)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                              |

| 2.10.2.1<br>2.10.2.2<br>2.10.2.3<br>2.10.2.4<br>2.11<br>2.12<br>2.13<br>2.14<br>2.14.1<br>2.14.1.1<br>2.14.1.2<br>2.14.1.3<br>2.14.1.4<br>2.14.2<br>2.14.2.1<br>2.14.2.1<br>2.14.2.1<br>2.14.2.1<br>2.14.2.1<br>2.14.2.1<br>2.14.2.1 | Expanded Memory Board Overview Theory Of Operation Of Expanded Memory Board CPU Memory Access DMA Memory Access MEDIUM RESOLUTION GRAPHICS BOARD LOW RESOLUTION CONTROLLER 280 Option Board 8248 Local Communications Option CPU BOARD 8246 280A CPU, Clock and Interface Circuitry 8086 Bus Interface and I/O Control Circuitry Interrupt Circuitry Keyboard Simulation Logic Datalink 8245 64K Triple-Ported Main Memory CRT Memory Memory Arbitration and Refresh 928 Datalink Interface REMOTE TELECOMMUNICATIONS OPTION RTC Board Theory of Operation MULTIPORT COMMUNICATIONS CONTROLLER (PC-PM042) MCC Option Theory of Operation | 2-48<br>2-53<br>2-54<br>2-56<br>2-58<br>2-63<br>2-64<br>2-64<br>2-72<br>2-73<br>2-75<br>2-77<br>2-77<br>2-77<br>2-80<br>2-91 |

|                                                                                                                                                                                                                                      | CHAPTER 3 CONTROLS AND INDICATORS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                              |

| 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.3.1<br>3.3<br>3.4<br>3.4.1<br>3.5<br>3.6<br>3.7                                                                                                                                         | Keyboard Indicators Important Keyboard Keys INITIAL CONTROL SETTINGS INITIAL TURN-ON PROCEDURES System Initialization NORMAL SHUT-DOWN PROCEDURE EMERGENCY SHUT-DOWN PROCEDURE                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                              |

| CHAPTER AN     | ND TITLE                                     | PAGE |

|----------------|----------------------------------------------|------|

|                | CHAPTER 4 INSTALLATION AND CHECKOUT          |      |

| 4.1            | SCOPE                                        |      |

| 4.2            | PRE-INSTALLATION SITE CHECK                  |      |

| 4.3            | SPECIAL TOOLS AND TEST EQUIPMENT             |      |

| 4.4            | UNPACKING                                    |      |

| 4.4.1          | Unpacking The Auto-Enclosed Materials        |      |

| 4.4.2          | Unpacking The Keyboard                       |      |

| 4.4.3          | Unpacking The Electronics Unit               |      |

| 4.4.4          | Unpacking The Monitor                        |      |

| 4.4.5<br>4.4.6 | Unpacking System Attachments                 |      |

| 4.4.6          | Final Unpacking Sequence                     | 4-8  |

| 4.6            | INSPECTION                                   |      |

| 4.6.1          | INTERCONNECTION OF EQUIPMENT                 |      |

| 4.6.2          | Base Unit                                    |      |

| 4.6.2.1        | Base Unit PCB's                              |      |

| 4.6.2.2        | Serial Keyboard                              |      |

| 4.6.2.3        | Video Monitor                                |      |

| 4.6.2.4        | Printers (Optional)                          |      |

| 4.7            | SWITCH SETTINGS                              | 4-26 |

| 4.7.1          | System Board Switch Setting                  |      |

| 4.7.2          | 115/230V Switch Setting                      |      |

| 4.7.3          | Keyboard Switch Setting                      |      |

| 4.7.4          | MX-80FT Type III Printer Switch Setting      |      |

| 4.7.5          | DW20 Printer                                 |      |

| 4.7.6          | System Floppy Drive                          |      |

| 4.8            | INSTALLATION                                 |      |

| 4.8.1          | System Unit Installation                     | 4-31 |

| 4.8.2          | Connecting The Keyboard                      | 4-32 |

| 4.8.3          | Connecting The Monitor                       | 4-32 |

| 4.8.4          | Connecting the AC Power Cord                 |      |

| 4.8.5          | Connecting the Printer (Optional)            | 4-32 |

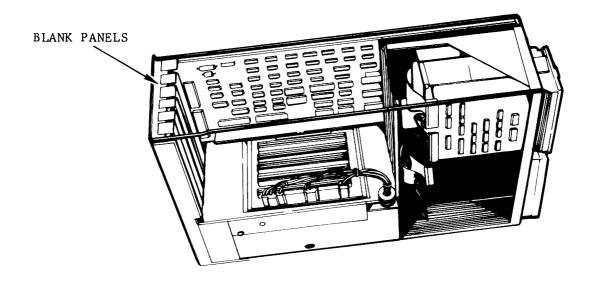

| 4.9            | SYSTEM EXPANSION                             | 4-33 |

| 4.9.1          | Installing an Option PCB                     | 4-33 |

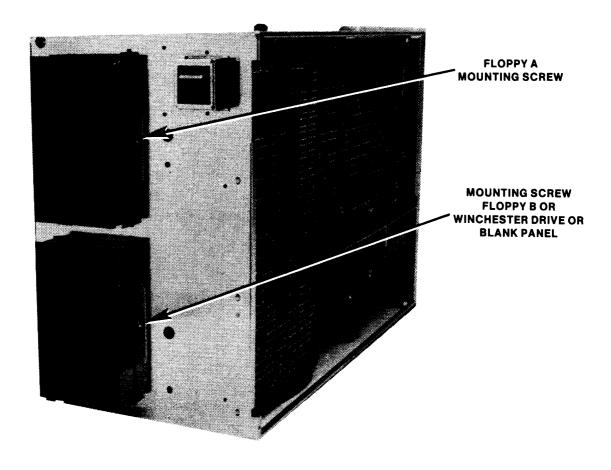

| 4.9.2          | Installing a 2nd Diskette Drive (Drive B)    | 4-35 |

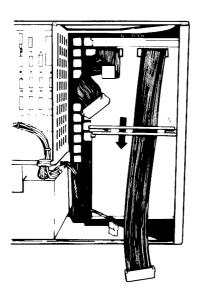

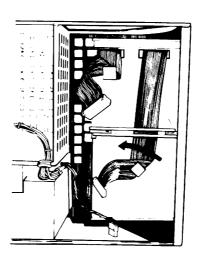

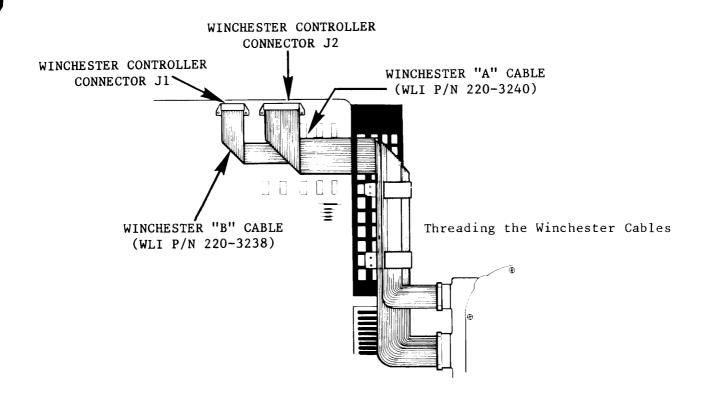

| 4.9.3          | Installing a Winchester Disk Drive (Drive C) |      |

| 4.9.4          | Replacing the Electronics Unit Cover         |      |

| 4.10           | POWERING-ON THE SYSTEM                       |      |

| 4.11           | SYSTEM RESTART (Warm Start)                  |      |

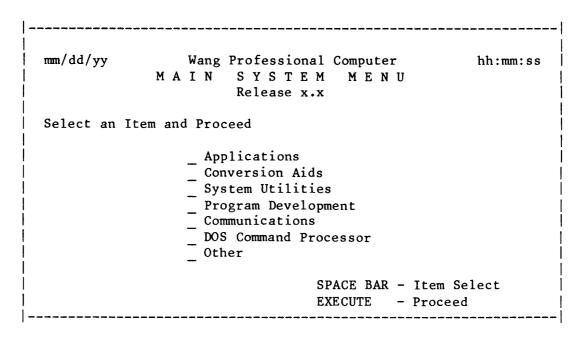

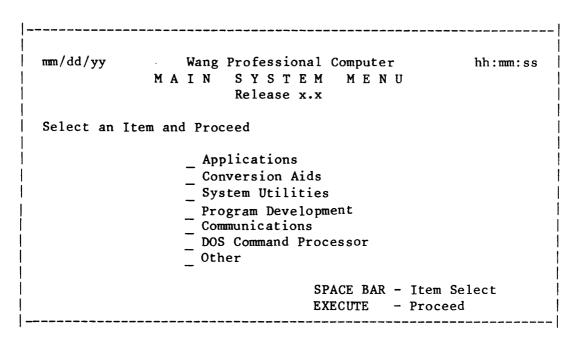

| 4.12           | MAIN SYSTEM MENU OPTIONS                     |      |

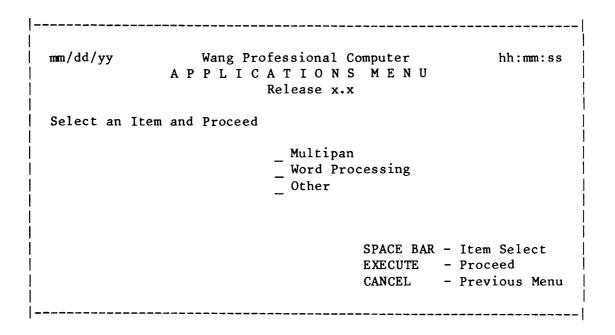

| 4.12.1         | Applications                                 |      |

| 4.12.2         | System Utilities                             |      |

| 4.12.3         | Program Development                          |      |

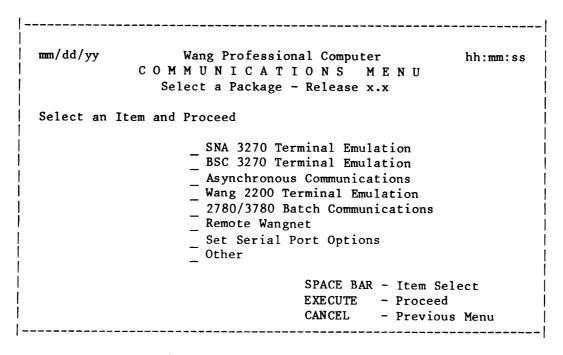

| 4.12.4         | Communications                               | 4-46 |

| CHAPTER A                                                                                                                                                                                                                       | ND TITLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PAGE                                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                 | CHAPTER 4 INSTALLATION AND CHECKOUT (Cont'd)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                              |

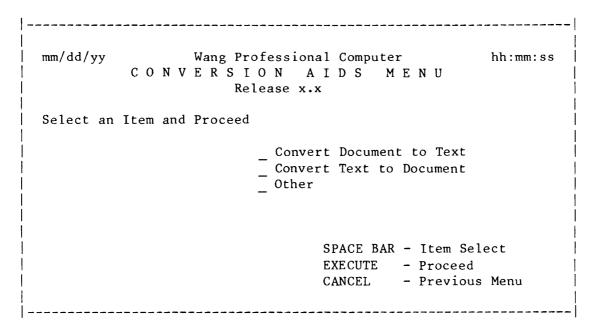

| 4.12.5<br>4.12.6<br>4.12.7<br>4.13<br>4.13.1<br>4.13.2<br>4.13.2.1<br>4.13.2.2<br>4.13.3<br>4.13.4<br>4.13.5                                                                                                                    | DOS Command Processor Other Conversion Aids POWER-UP DIAGNOSTIC Operation Error Reporting FATAL ERRORS NON-FATAL ERRORS B.I.T. Options Keyboard Loopback Floppy-Based Diagnostic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-48<br>4-48<br>4-49<br>4-49<br>4-49<br>4-50<br>4-50<br>4-51                                                 |

|                                                                                                                                                                                                                                 | CHAPTER 5 PREVENTIVE AND CORRECTIVE MAINTENANCE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                              |

| 5.0<br>5.1<br>5.1.1<br>5.2<br>5.2.1<br>5.3<br>5.3.1<br>5.3.1.2<br>5.3.1.3<br>5.3.1.4<br>5.3.1.5<br>5.3.1.6<br>5.3.1.7<br>5.3.2<br>5.3.2.1<br>5.3.2.2<br>5.3.2.1<br>5.3.2.2<br>5.3.2.3<br>5.3.2.4<br>5.3.2.5<br>5.3.2.7<br>5.3.3 | PREVENTIVE MAINTENANCE  CORRECTIVE MAINTENANCE  Special Tools  ELECTRICAL ADJUSTMENTS  Electrical Measurements and Checks  MECHANICAL ADJUSTMENTS  Tandon Floppy Disk Drive Adjustments  Tandon Floppy Disk Voltage Check  Tandon Drive Motor Speed Adjustment  Tandon Drive Radial-Track Alignment  Tandon Track 00 End-Stop Adjustment  Tandon Index-To-Data Alignment  Tandon Neoprene Drive Belt  Tandon Write-Protect Switch  MPI DISK DRIVE ADJUSTMENTS AND MEASUREMENTS  MPI Drive Motor Speed Adjustment  MPI Radial-Track Alignment  MPI Radial-Track Alignment  MPI Track 00 End Stop  MPI Drive Belt Adjustment  MPI Track 00 End Stop  MPI Drive Belt Adjustment  MPI Write-Protect Check  WINCHESTER DRIVE ADJUSTMENTS | 5-1<br>5-1<br>5-1<br>5-3<br>5-4<br>5-4<br>5-6<br>5-9<br>5-10<br>5-11<br>5-12<br>5-12<br>5-12<br>5-13<br>5-17 |

| 5.4<br>5.4.1<br>5.4.1.1<br>5.4.1.2                                                                                                                                                                                              | VIDEO MONITOR ADJUSTMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5-19<br>5-20<br>5-20<br>5-23                                                                                 |

| CHAPTER                                                                                    | AND TITLE                                                                                                   |                                                         | PAGE                                                         |

|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|--------------------------------------------------------------|

|                                                                                            | Pl                                                                                                          | CHAPTER 5 REVENTIVE AND CORRECTIVE MAINTENANCE (Cont'd) |                                                              |

| 5.4.2<br>5.5<br>5.5.1<br>5.5.1.1<br>5.5.1.2<br>5.5.1.3<br>5.5.2<br>5.5.3<br>5.5.3.1<br>5.6 | Graph<br>REMOVAL A<br>System Un<br>Power Sur<br>Floppy Dr<br>Wincheste<br>Wang Monr<br>Keyboard<br>Keyboard | nitor Adjustments For Character And ics Display         | 5-29<br>5-29<br>5-31<br>5-32<br>5-32<br>5-33<br>5-34<br>5-34 |

|                                                                                            |                                                                                                             | CHAPTER 6<br>SCHEMATICS                                 |                                                              |

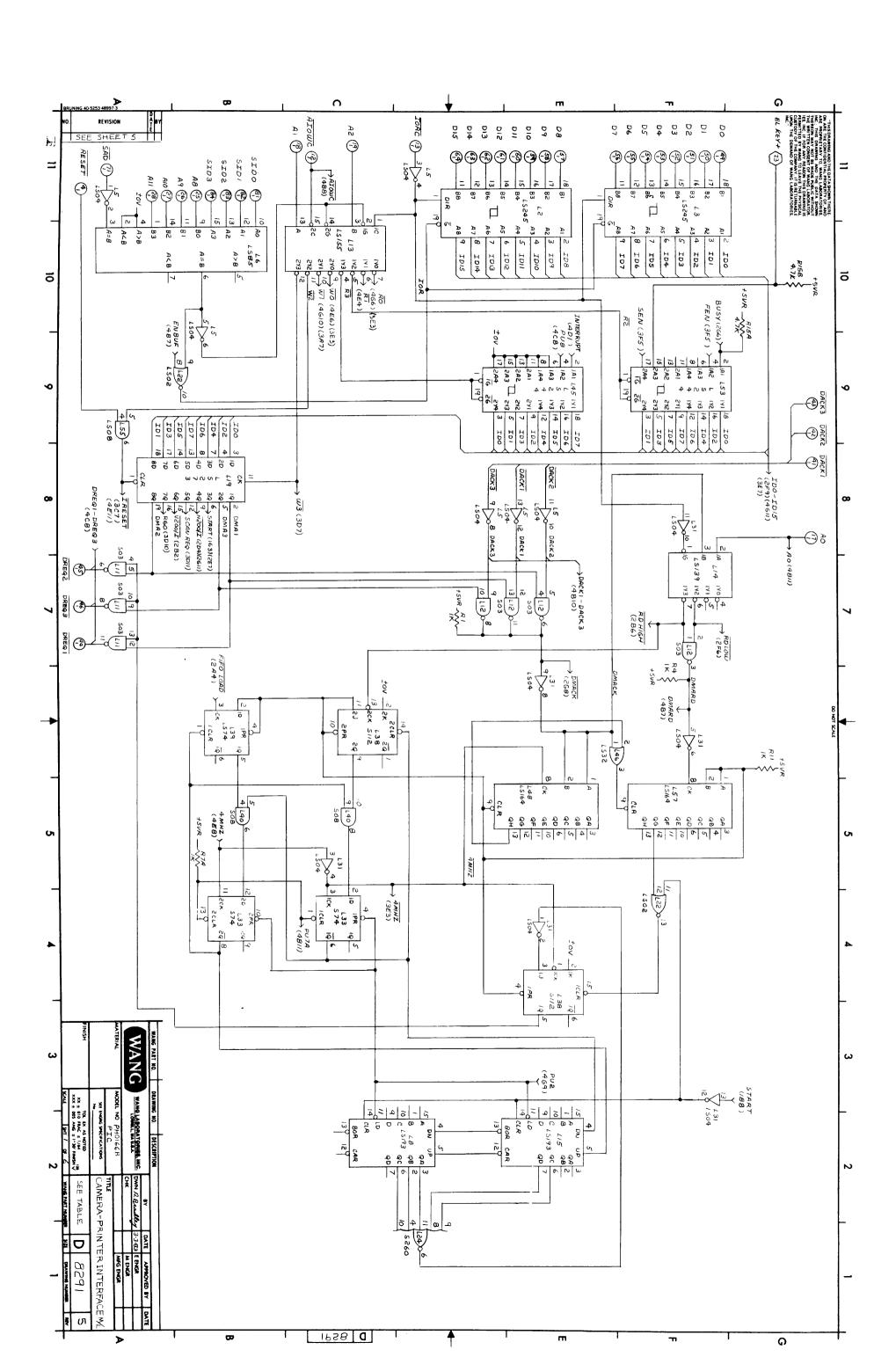

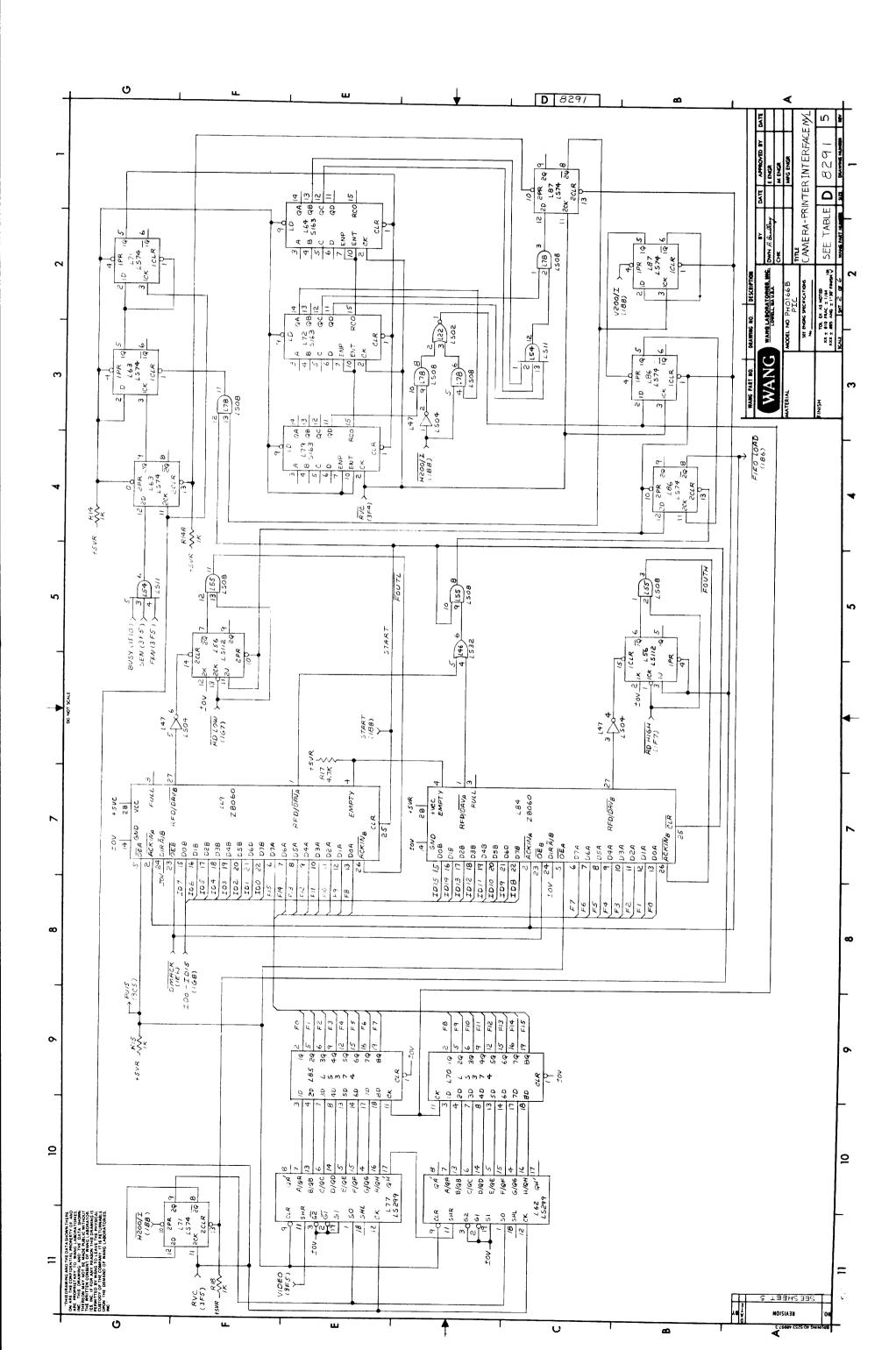

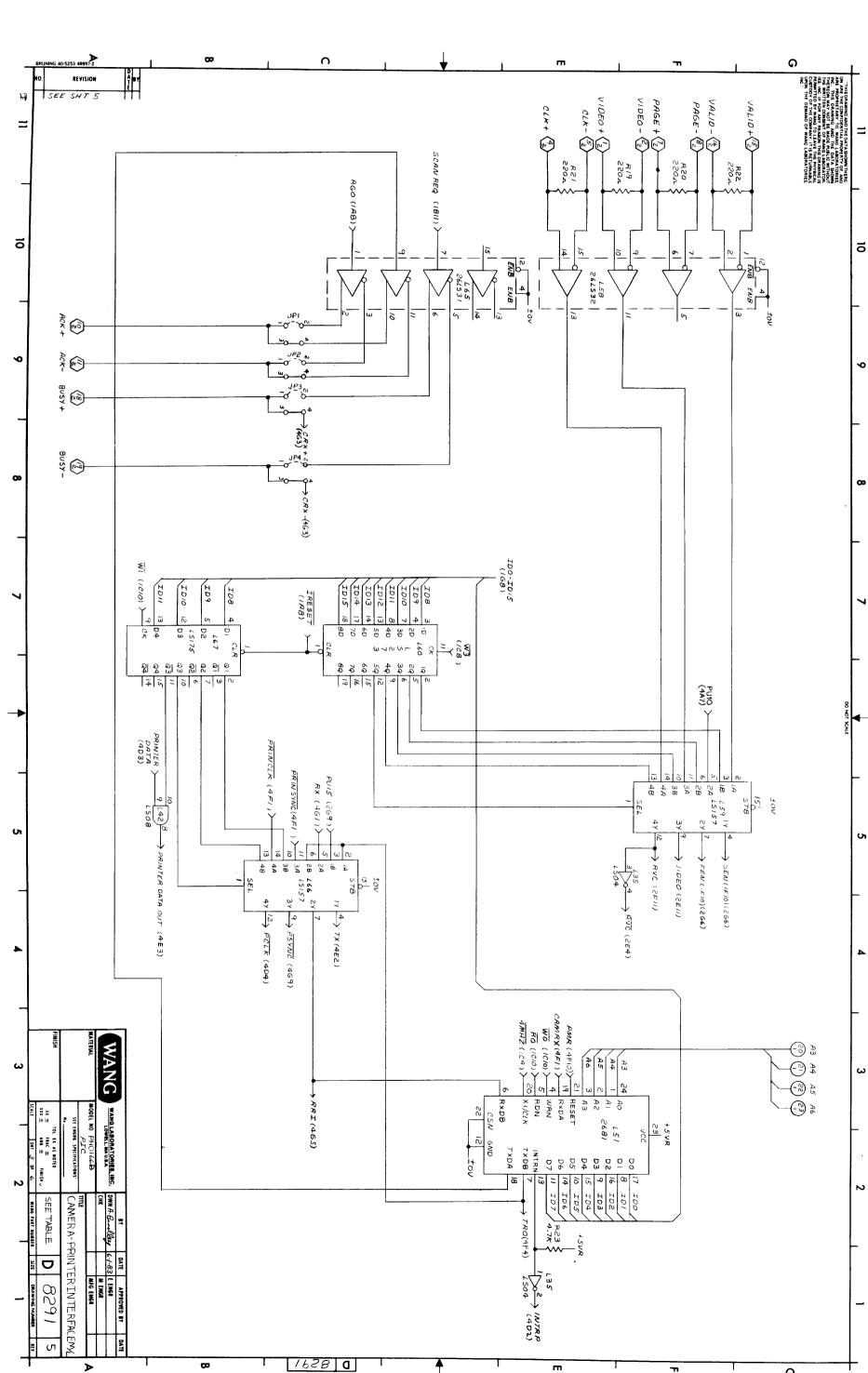

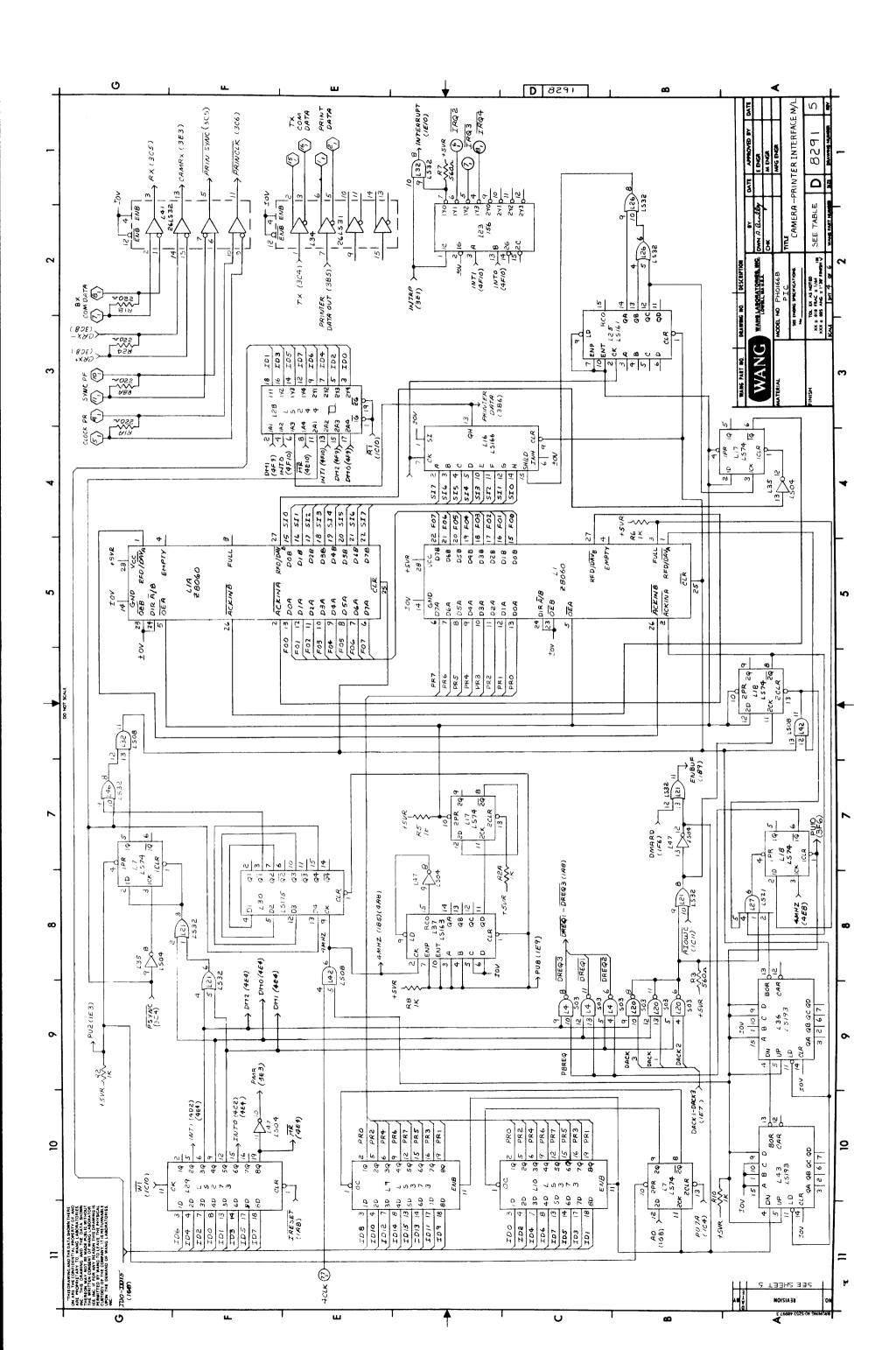

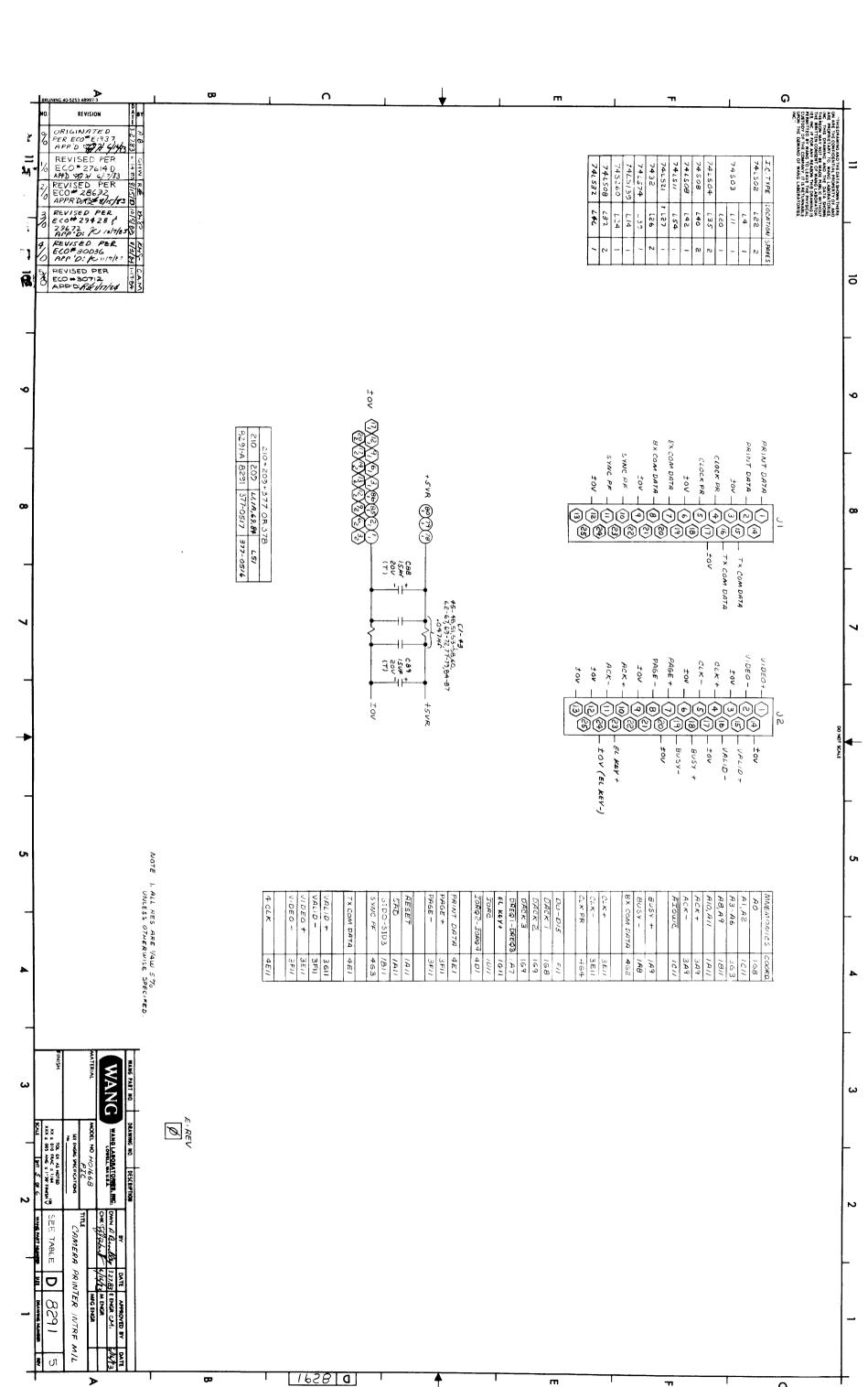

|                                                                                            | Provided                                                                                                    | in PC Schematic Manual WLI 729-1241                     |                                                              |

|                                                                                            |                                                                                                             | CHAPTER 7 ILLUSTRATED PARTS BREAKDOWN                   |                                                              |

| 7.1                                                                                        | SCOPE                                                                                                       | • • • • • • • • • • • • • • • • • • • •                 | 7-1                                                          |

|                                                                                            |                                                                                                             | CHAPTER 8 TROUBLESHOOTING                               |                                                              |

| 8.1                                                                                        | SCOPE                                                                                                       | •••••                                                   | 8-1                                                          |

|                                                                                            |                                                                                                             | APPENDICES                                              |                                                              |

| APPENDIX APPENDIX APPENDIX APPENDIX APPENDIX                                               | B<br>C<br>D                                                                                                 | Listing Of Cable Assemblies                             | B-1<br>C-1<br>D-1                                            |

# LIST OF ILLUSTRATIONS

| FIGURE       | DESCRIPTION                                               | PAGE |

|--------------|-----------------------------------------------------------|------|

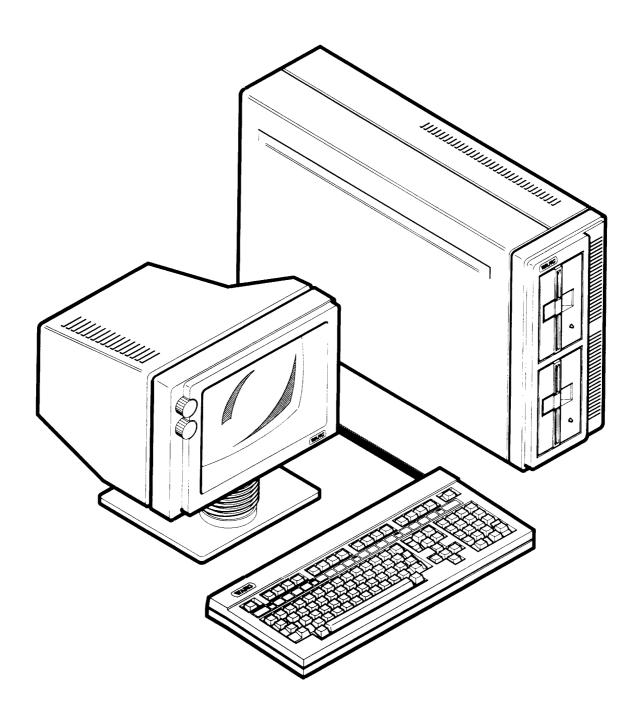

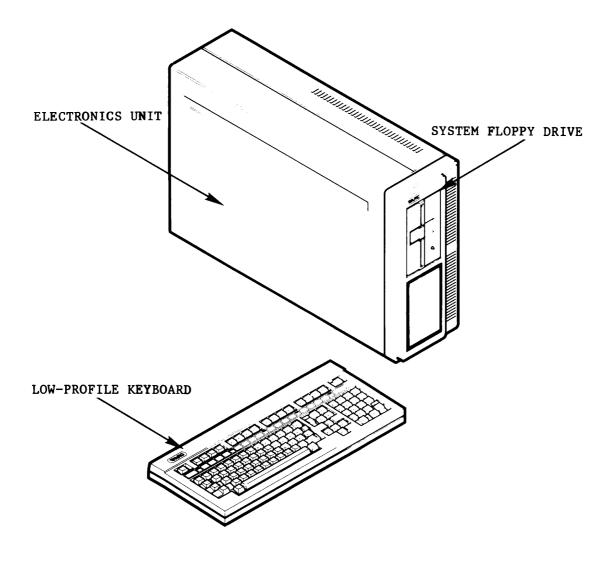

| 1-1          | PC Standard Equipment (PC-001)                            | 1-5  |

| 2-1          | PC System Block Diagram                                   | 2-2  |

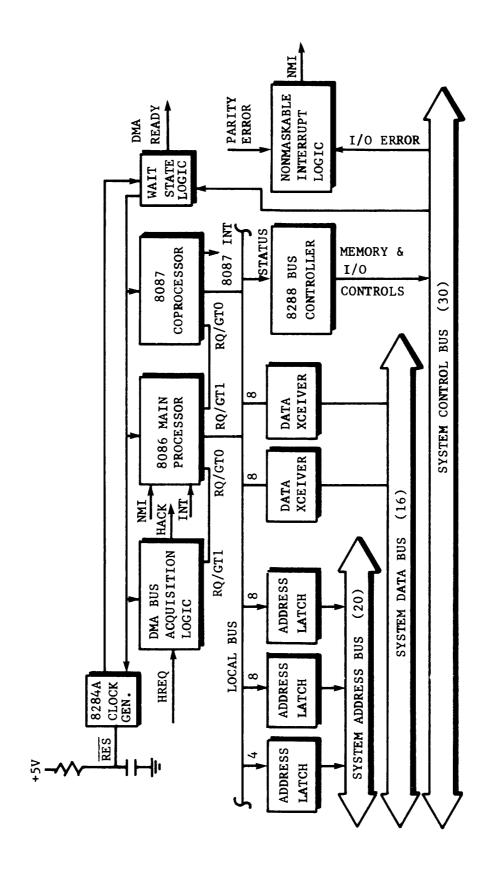

| 2-2          | CPU Processor Block Diagram                               | 2-9  |

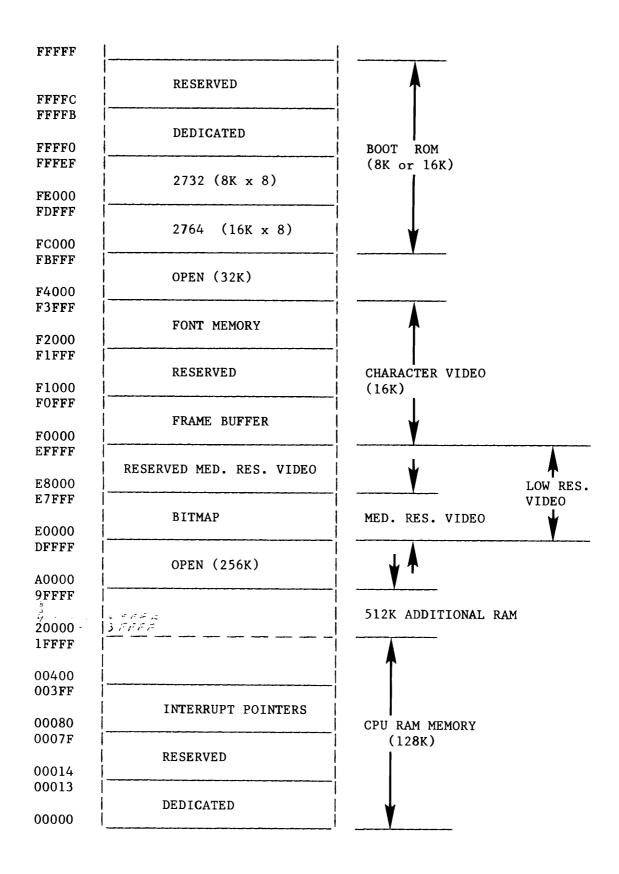

| 2-3          | 8086 Memory Mapped Addressing                             |      |

| 2-4          | 8086 I/O Mapped Addressing                                |      |

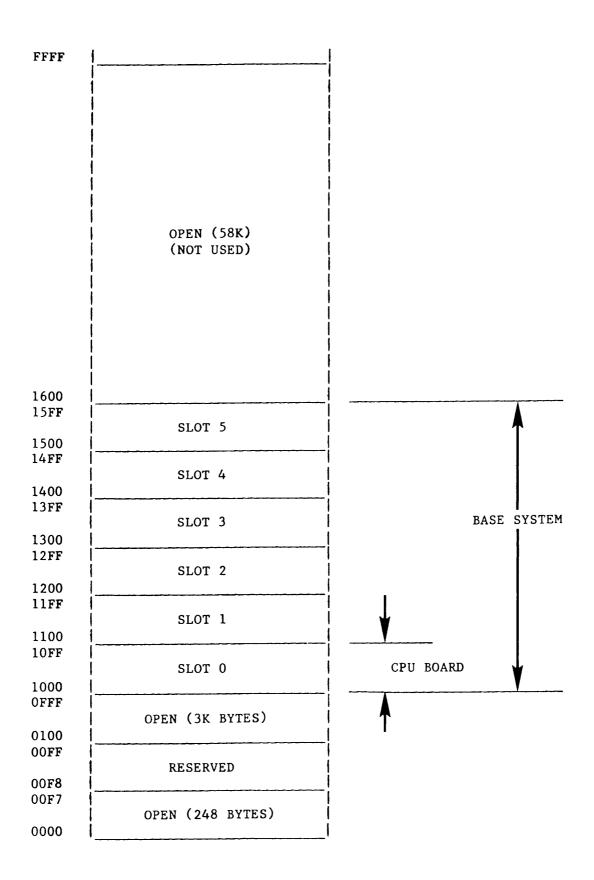

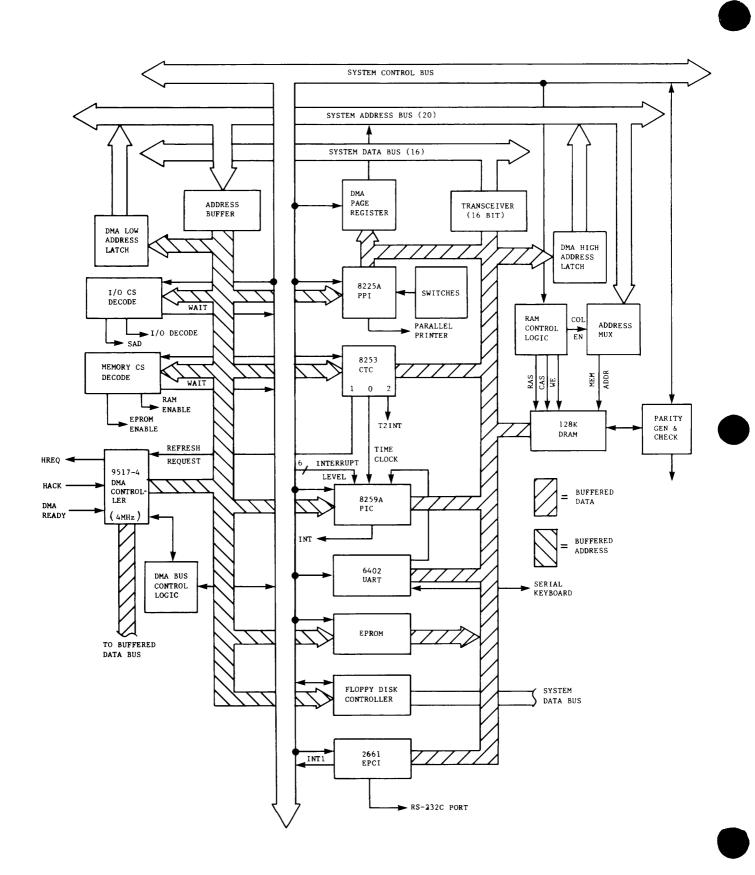

| 2-5          | System Board Block Diagram                                | 2-18 |

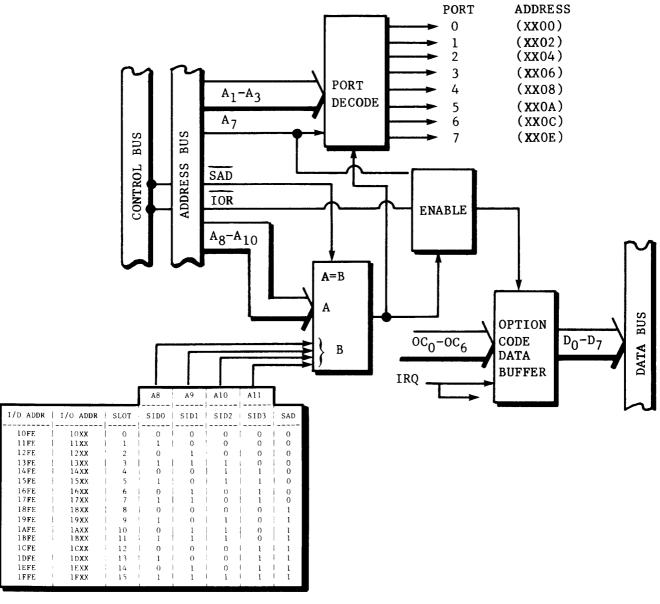

| 2-6          | Slot Decode Block Diagram                                 | 2-19 |

| 2-7          | 8243/8343 Medium Resolution Video Controller              |      |

|              | Block Diagram                                             |      |

| 2-8          | Standard Keyboard Mapping                                 | 2-37 |

| 2-9          | Expanded Keyboard Mapping                                 | 2-38 |

| 2-10         | Low-Profile Keyboard Block Diagram                        | 2-40 |

| 2-11         | Monitor Board 8244/8344 Block Diagram                     | 2-42 |

| 2-12         | Expanded Memory Board Block Diagram                       | 2-49 |

| 2-13         | Expanded Memory Board RAM Layout                          | 2-52 |

| 2-14         | Graphics Resolution Board Block Diagram                   | 2-55 |

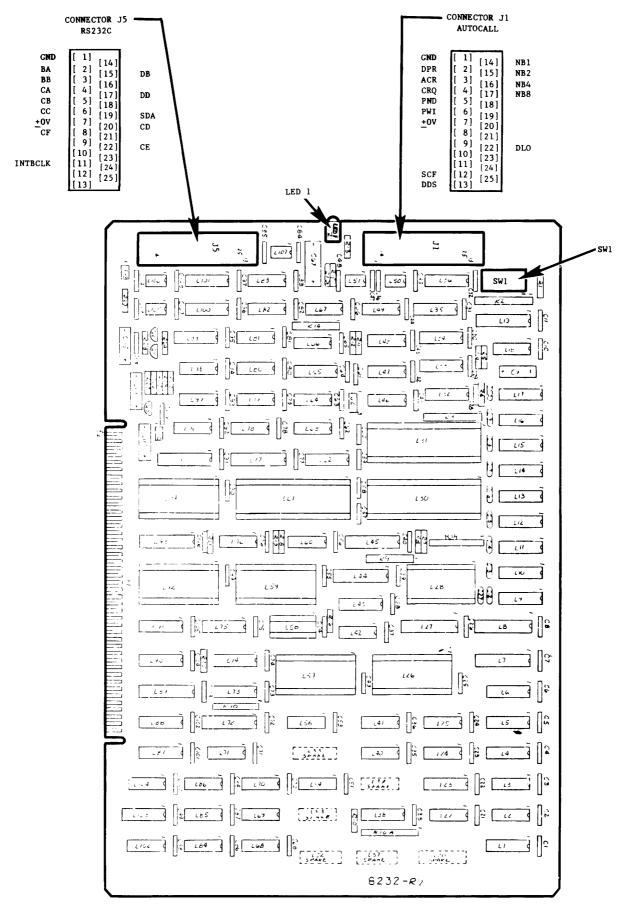

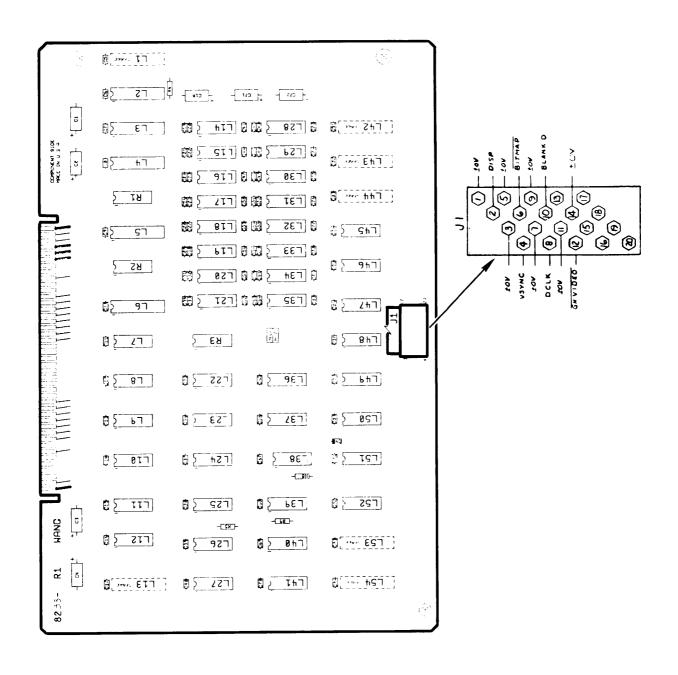

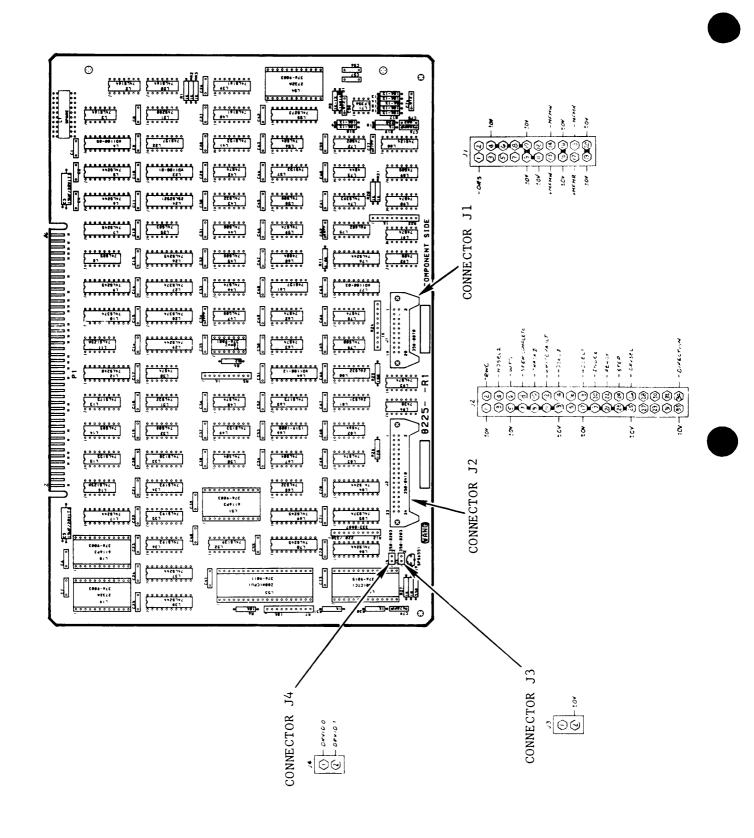

| 2-15         | RTC PCA 8232 Connector Locations                          | 2-79 |

| 2-16         | RTC Functional Block Diagram                              | 2-81 |

| 2-17         | RTC Outbound/Inbound Data Path                            | 2-83 |

| 2-18         | MCC Board 8251 Port Locations                             |      |

| 2-19         | MCC 8251 Controller Block Diagram                         |      |

| 2-20         | MCC Card Inbound/Outbound Data Paths                      |      |

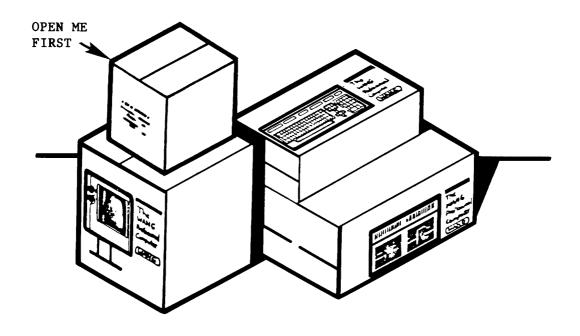

| 4-1          | The Wang Professional Computer Fully Packaged             | 4-2  |

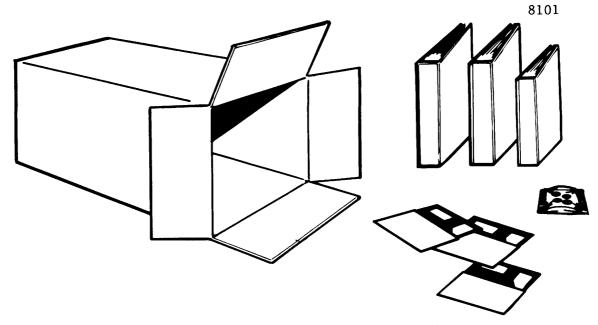

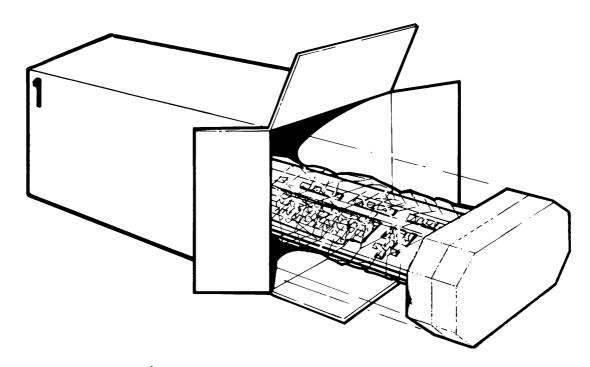

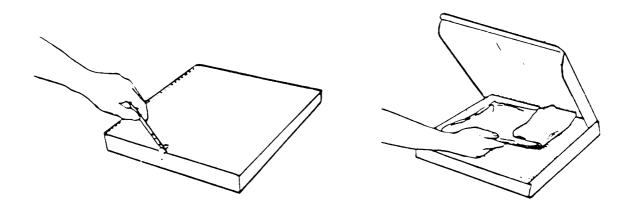

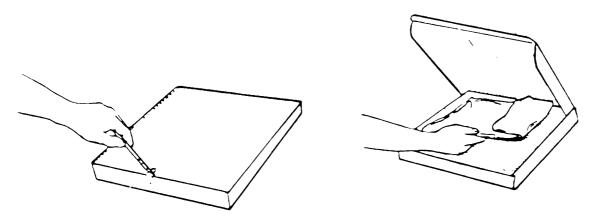

| 4-2          | Opening The Auto-Enclosed Materials Box                   | 4-3  |

| 4-3          | Unpacking The Keyboard                                    |      |

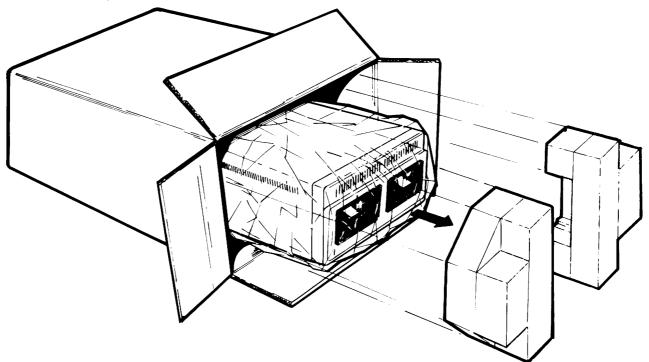

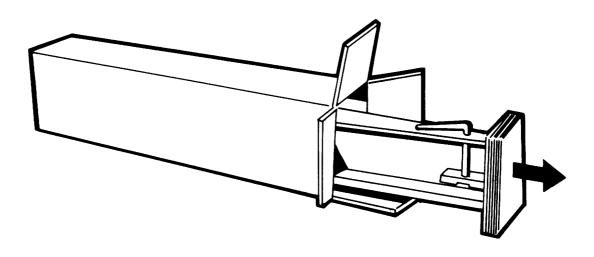

| 4-4          | Unpacking The Electronics Unit                            | 4-4  |

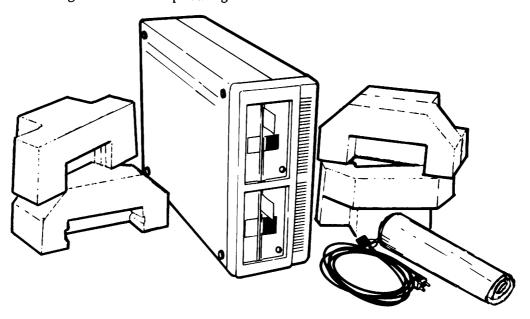

| 4-5          | Electronics Unit Components                               | 4-4  |

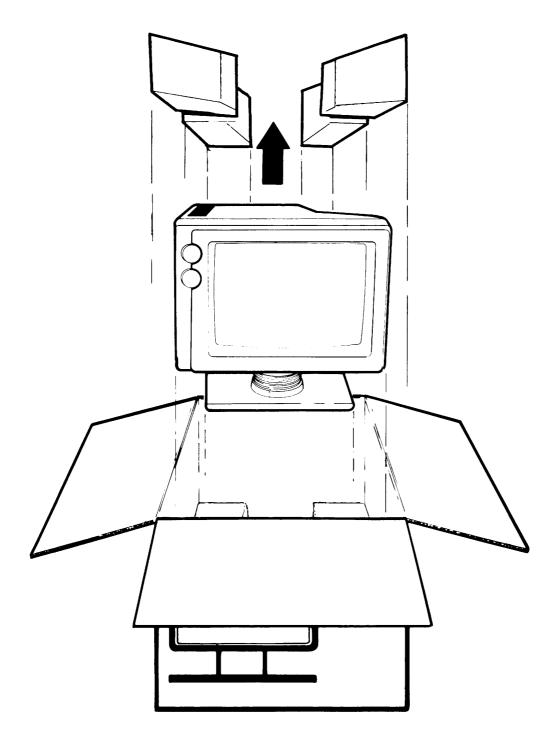

| 4-6          | Unpacking The Monitor                                     | 4-5  |

| 4-7          | Wang PC Monitor Components                                |      |

| 4-8          | Unpacking The Desk Clamp                                  |      |

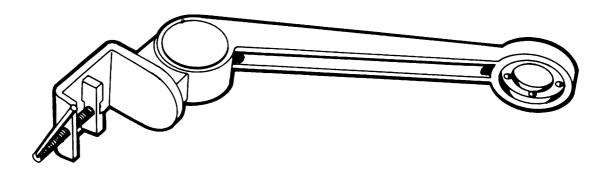

| 4-9          | Wang PC Monitor Arm                                       |      |

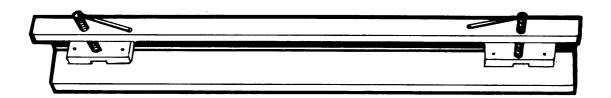

| 4-10         | Wang PC Electronics Unit Desk Clamp                       | 4-7  |

| 4-11         | Removing The Shipping Protector From The Diskette Drive . |      |

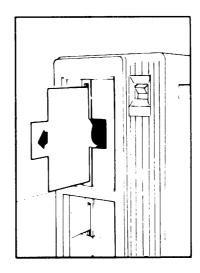

| 4-12         | Electronics Base Unit                                     |      |

| 4-13         | Base Unit Cover Removal and PCB Locations                 | 4-11 |

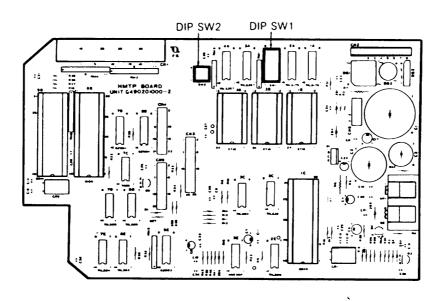

| 4-14         | CPU System Board (210-8221-A)                             | 4-12 |

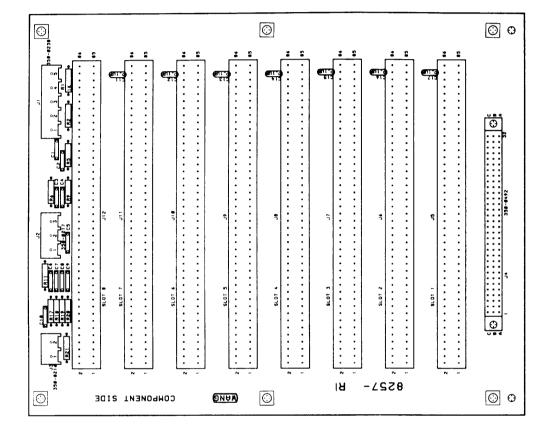

| <b>4-</b> 15 | Motherboard (210-8237)                                    |      |

| 4-16         | Low Resolution Board (210-8222)                           |      |

| 4-17         | Character Resolution Board (210-8243)                     |      |

| 4-18         | Character Resolution Board (210-8343)                     |      |

| 4-19         | Graphics Resolution Board (210-8233)                      |      |

| 4-20         | Winchester Controller Board (210-8225A)                   | 4-18 |

| 4-21         | Wang Switching Power Supply (270-0792)                    | 4-19 |

| 4-22         | Floppy Disk Drive A (Drive B Optional) (278-4026)         | 4-20 |

| 4-23         | Winchester Drive (Drive C Optional) (278-4030)            |      |

|              | •                                                         |      |

# LIST OF ILLUSTRATIONS (Cont'd)

| FIGURE | DESCRIPTION                                         | PAGE |

|--------|-----------------------------------------------------|------|

| 4-24   | Low-Profile Serial Keyboard (279-2042)              | 4-21 |

| 4-25   | TTL Monitor Assembly (279-0541)                     | 4-22 |

| 4-26   | TTL Monitor Electronics Board (210-8244)            | 4-23 |

| 4-27   | TTL Monitor Electronics Board (210-8344)            | 4-24 |

| 4-28   | Wang Daisy DW20                                     | 4-25 |

| 4-29   | MX-80FT TYPE III Printer (725-0129)                 | 4-25 |

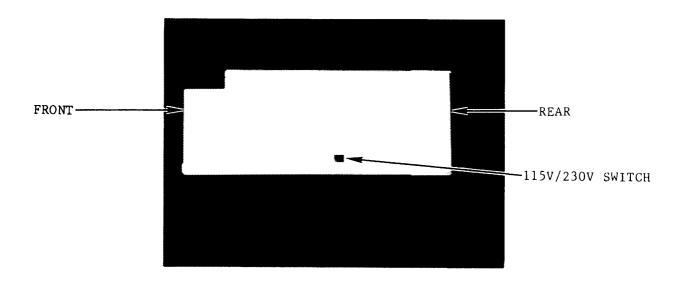

| 4-30   | 115V/230V Switch Setting                            | 4-27 |

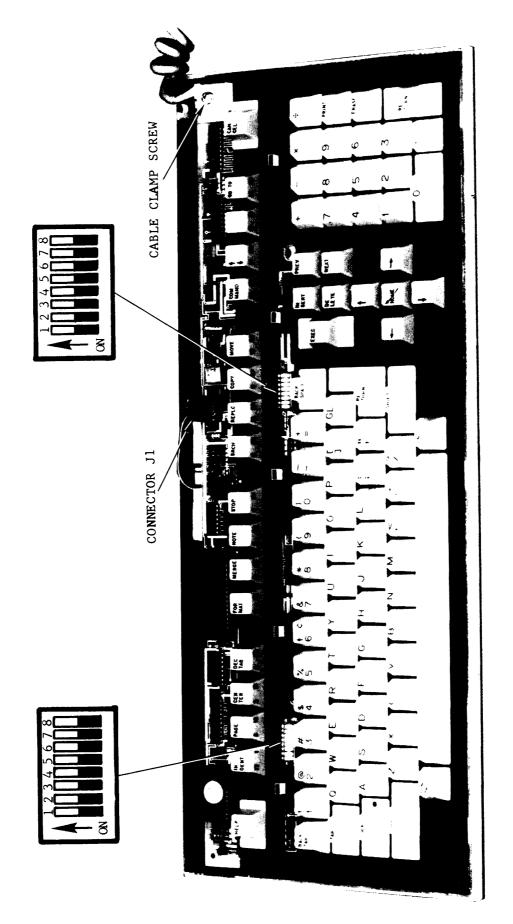

| 4-31   | Low-Profile Keyboard DIP Switch Locations           | 4-28 |

| 4-32   | MX-80FT TYPE III Printer Switch Locations           | 4-29 |

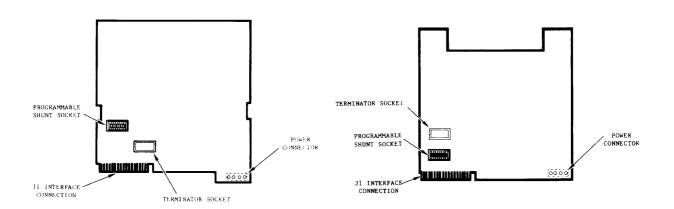

| 4-33   | Floppy Drive Programmable Shunt Location            | 4-30 |

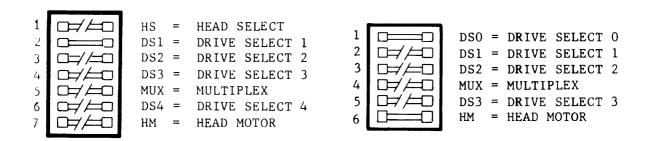

| 4-34   | Floppy Drive Shunt Identification                   | 4-31 |

| 4-35   | Printer Cable Connector                             | 4-33 |

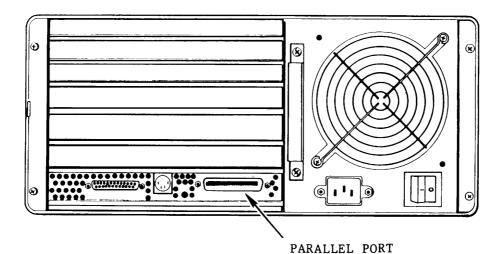

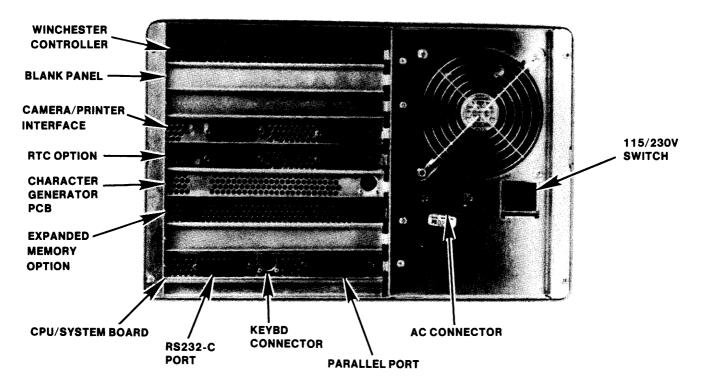

| 4-36   | Electronic Unit Rear View                           | 4-34 |

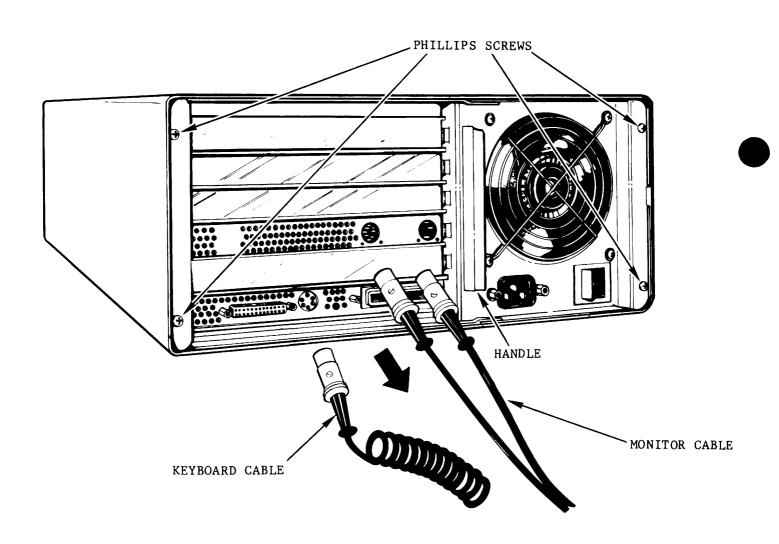

| 4-37   | Electronics Unit Vertical Position                  | 4-35 |

| 4-38   | Floppy Drive Cabling                                | 4-37 |

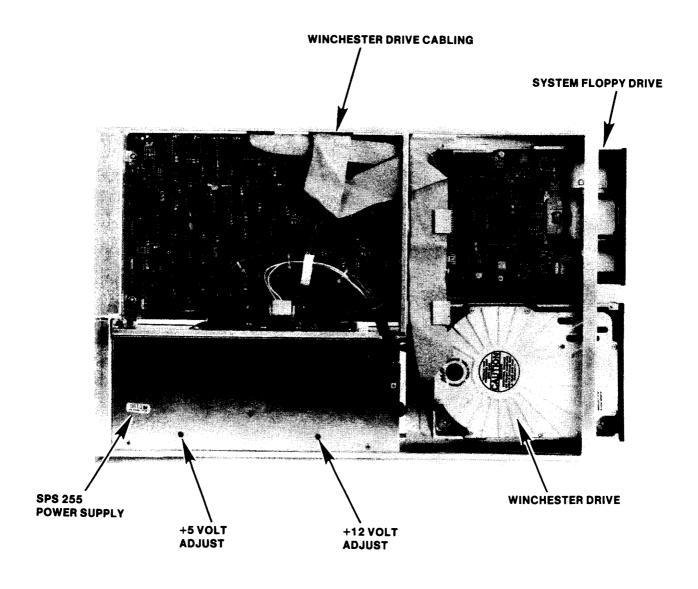

| 4-39   | Winchester Drive Cabling                            | 4-39 |

| 4-40   | The Non-Start Display                               | 4-41 |

| 4-41   | The Time and Date Screen                            | 4-42 |

| 4-42   | The Main System Menu Display                        |      |

| 4-43   | The Applications Menu                               | 4-44 |

| 4-44   | System Utilities Menu                               | 4-45 |

| 4-45   | Program Development Menu                            | 4-46 |

| 4-46   | Communications Menu                                 | 4-47 |

| 4-47   | Conversion Aids Menu                                | 4-48 |

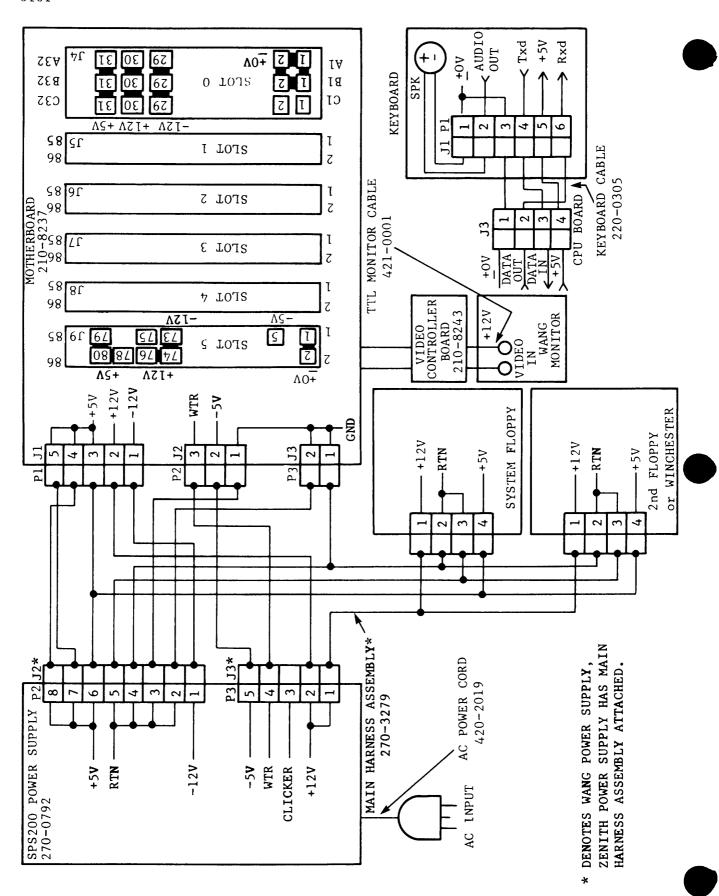

| 5-1    | Power Distribution and Interconnection Diagram      | 5-2  |

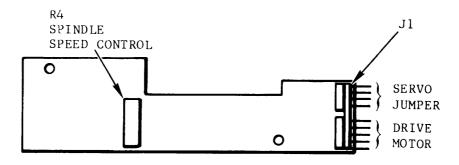

| 5-2    | Location of R4 Speed Control Pot                    | 5-5  |

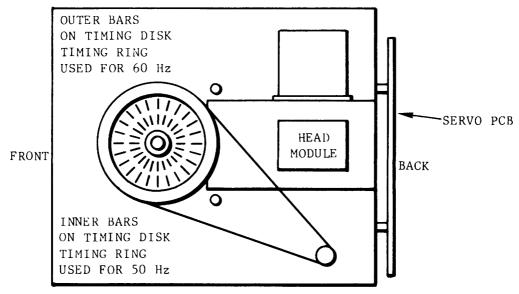

| 5-3    | Tandon Floppy Drive PCB Test Point Locations        | 5-6  |

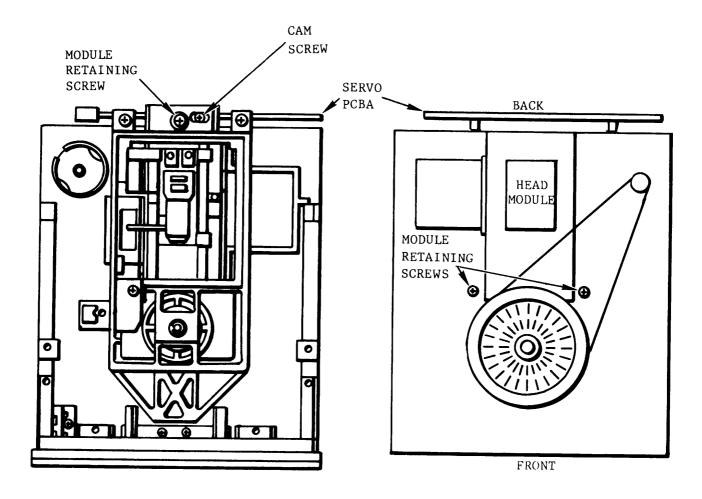

| 5-4    | Head Module Retaining Screws Location               | 5-7  |

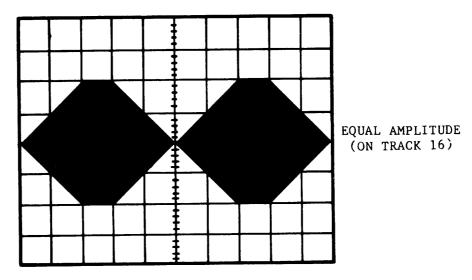

| 5-5    | Cats Eye Pattern                                    | 5-8  |

| 5-6    | Track 00 End-Stop Screw Location                    | 5-9  |

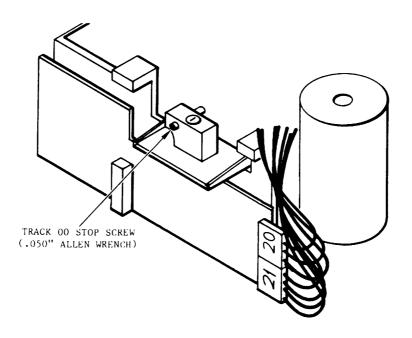

| 5-7    | Index Sensor Retaining Screw and Adjustment         | 5-10 |

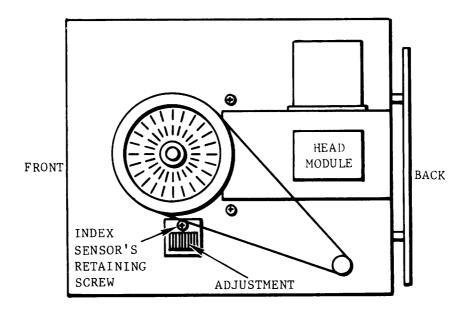

| 5-8    | Index-To-Data Alignment Pattern                     | 5-11 |

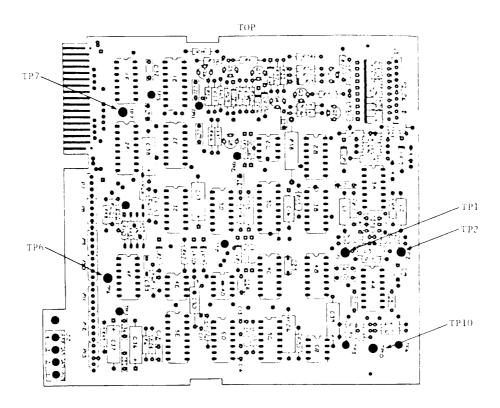

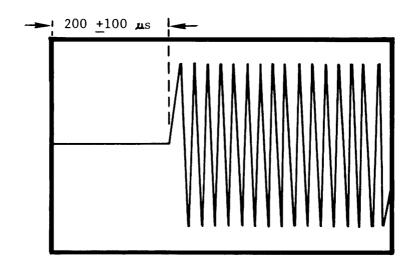

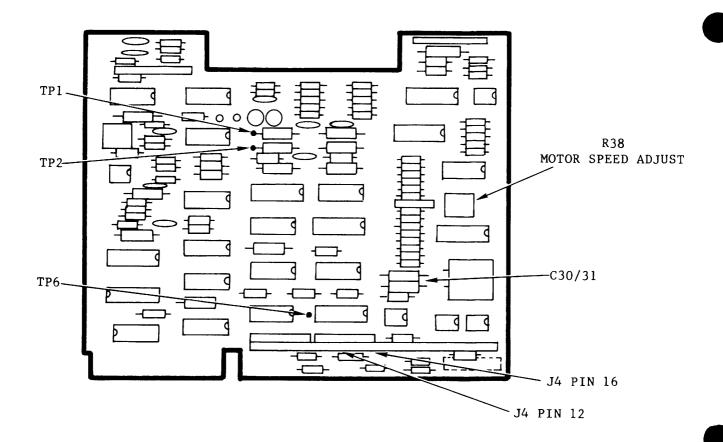

| 5-9    | MPI PCB Test Point Locations                        | 5-14 |

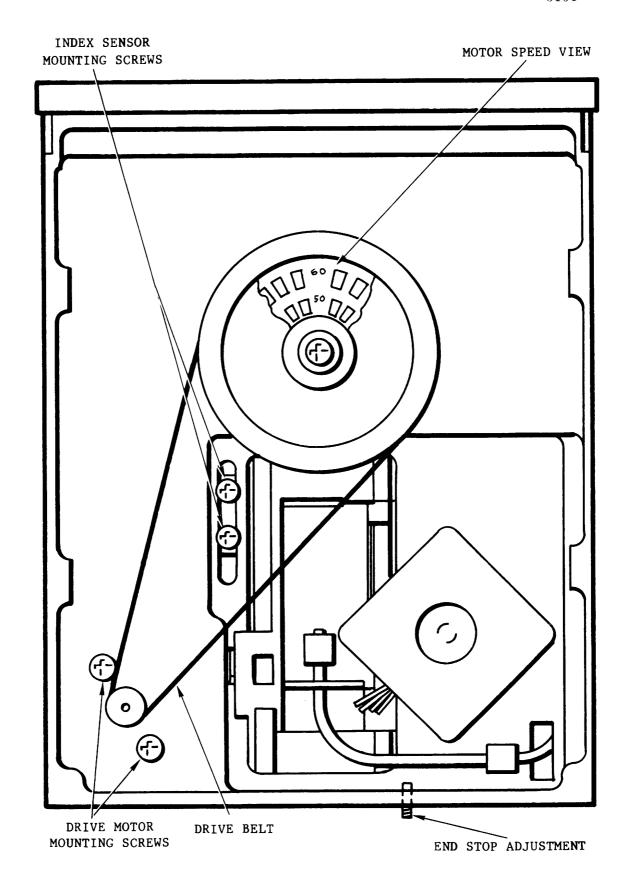

| 5-10   | MPI 52 Disk Drive Bottom View                       | 5-15 |

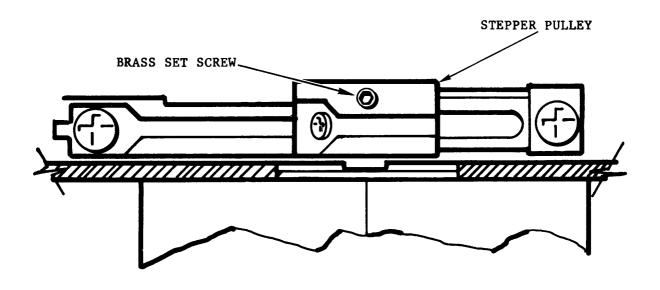

| 5-11   | Stepper Pulley/Band Assembly                        | 5-16 |

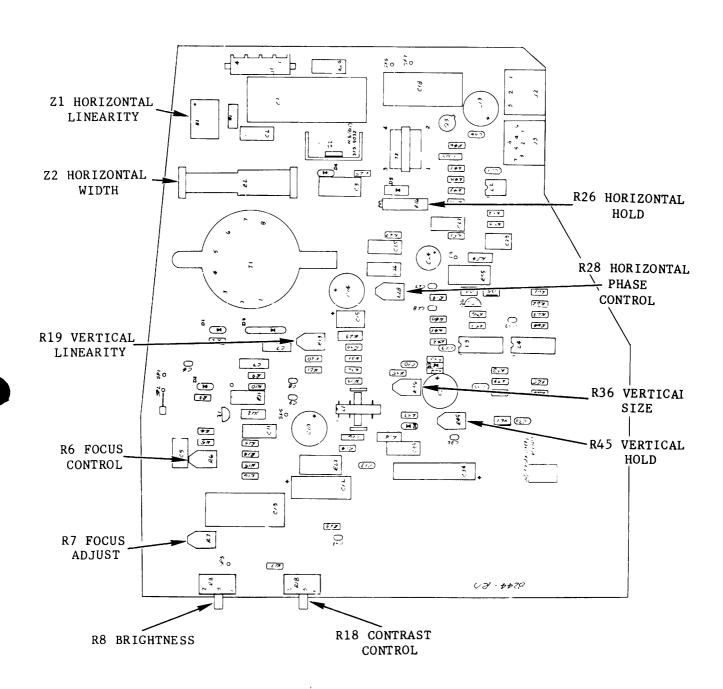

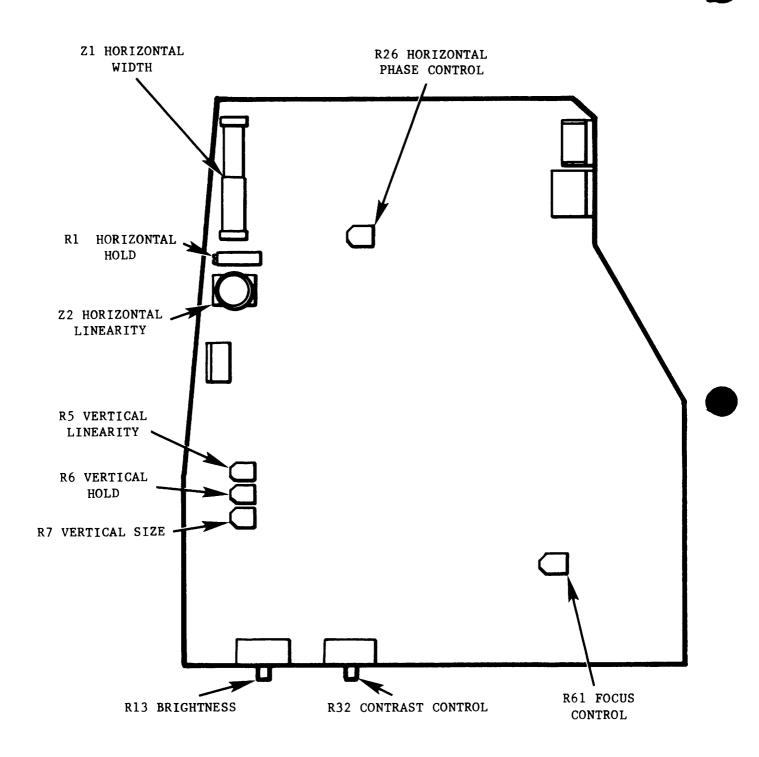

| 5-12   | Monitor Board 8244 Test Point Locations             | 5-21 |

| 5-13   | Monitor Board 8344 Test Point Locations             | 5-22 |

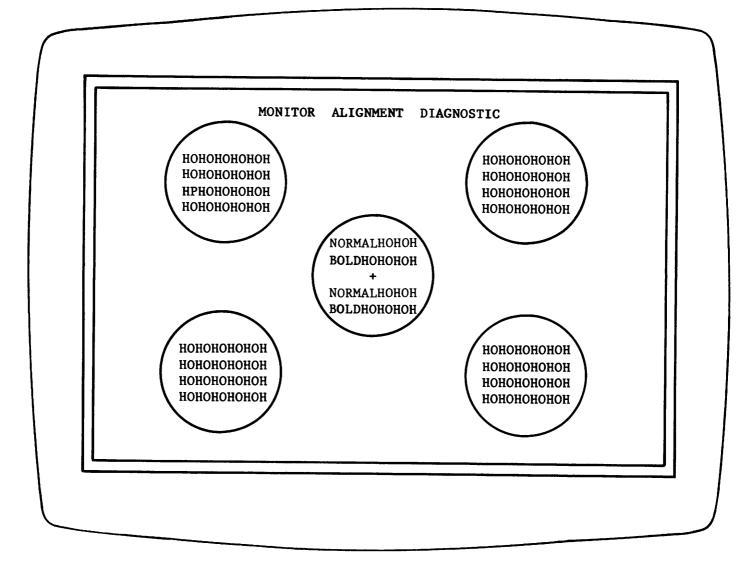

| 5-14   | Monitor Alignment Screen                            | 5-25 |

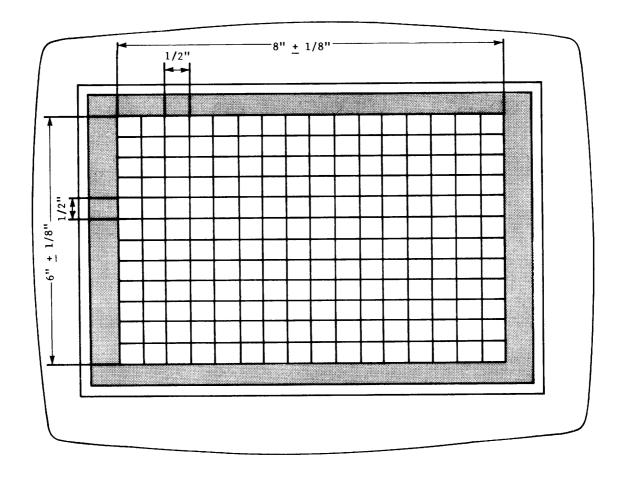

| 5-15   | Monitor Alignment Grid Pattern                      |      |

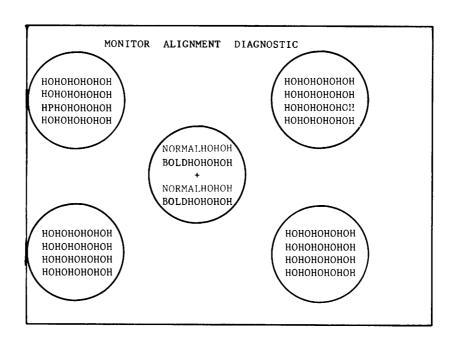

| 5-16   | Monitor Alignment Screen Horizontal Hold Adjustment | 5-27 |

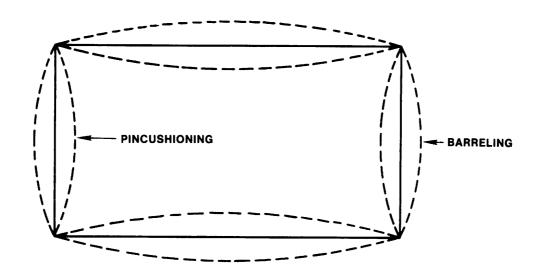

| 5-17   | Pincushioning and Barreling of CRT                  | 5-28 |

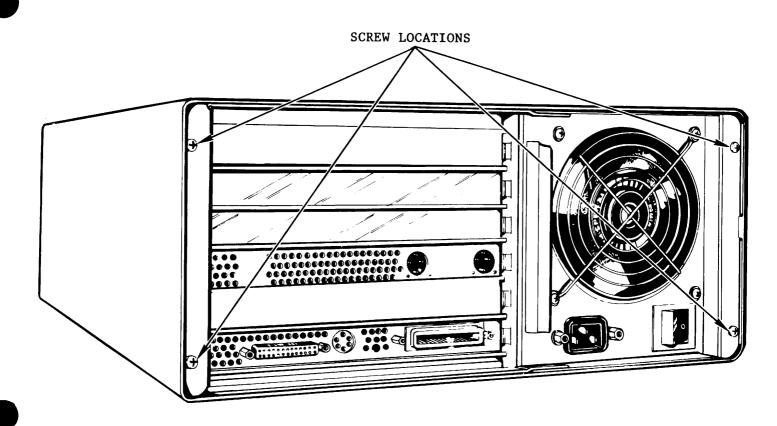

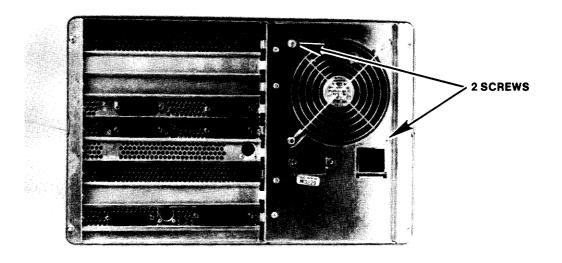

| 5-18   | System Unit Cover Removal                           | 5-29 |

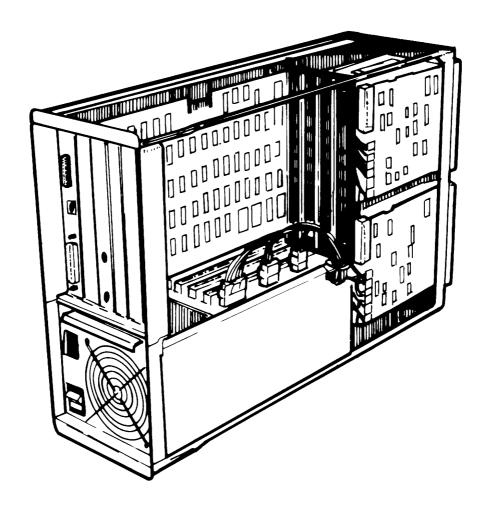

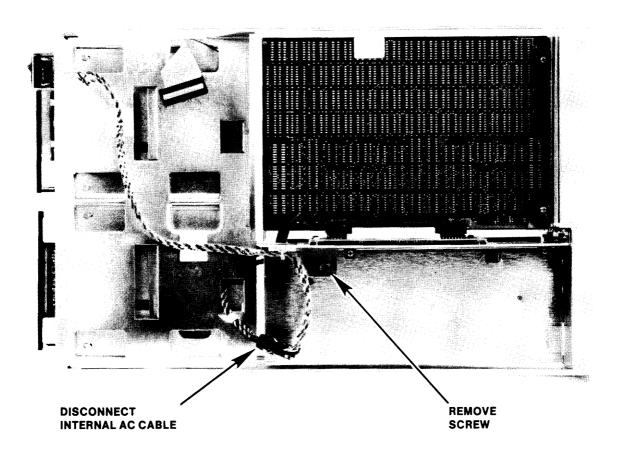

| 5-19   | Electronics Unit in Vertical Position               | 5-30 |

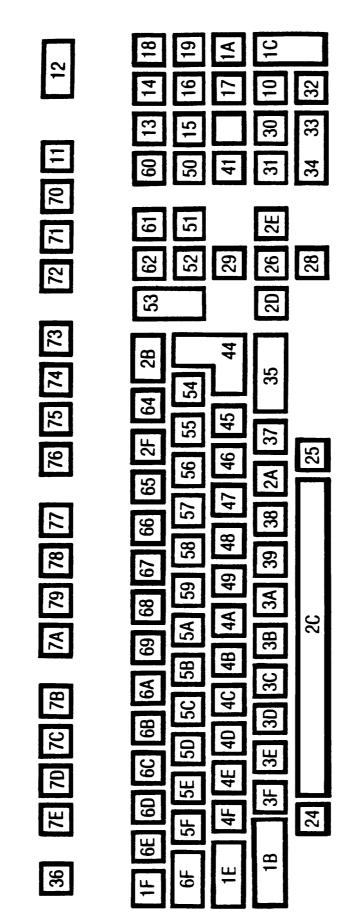

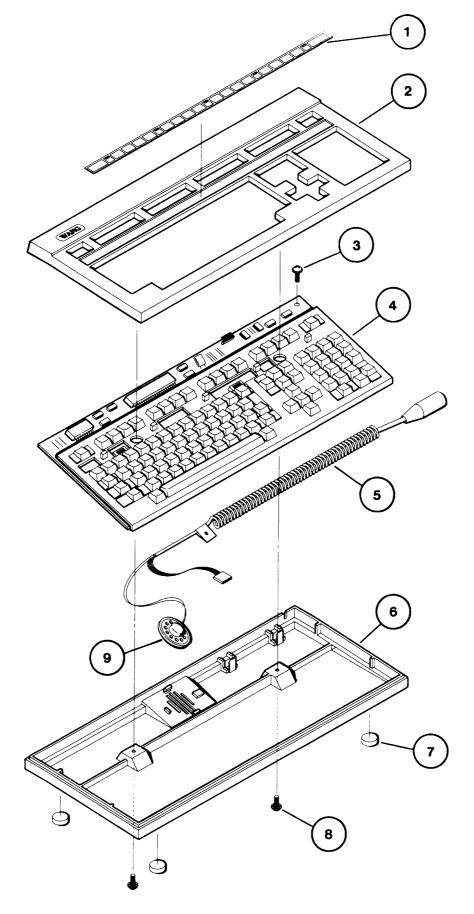

| 7-1    | Low Profile Keyboard IPB                            | 7-3  |

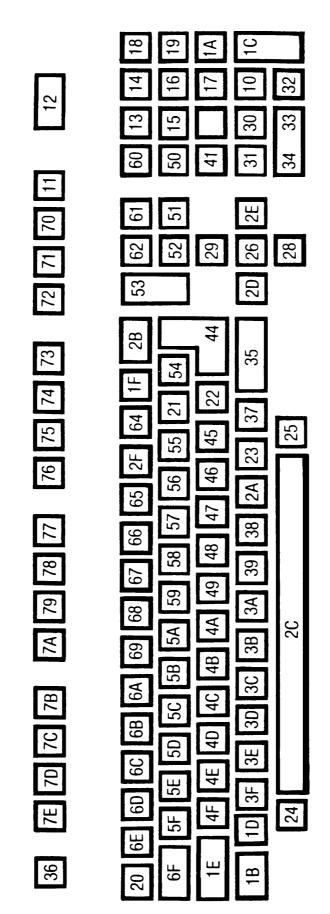

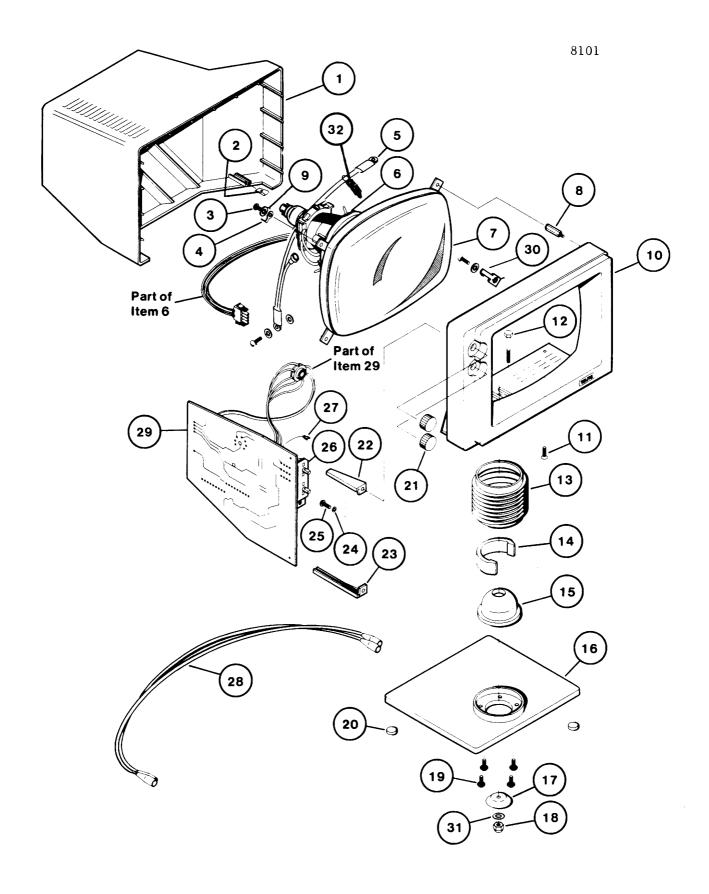

| 7-2    | TTL Monitor Assembly 279-0541 IPB                   | 7-5  |

# LIST OF ILLUSTRATIONS (Cont'd)

| FIGURE            | DESCRIPTION                                       | PAGE |

|-------------------|---------------------------------------------------|------|

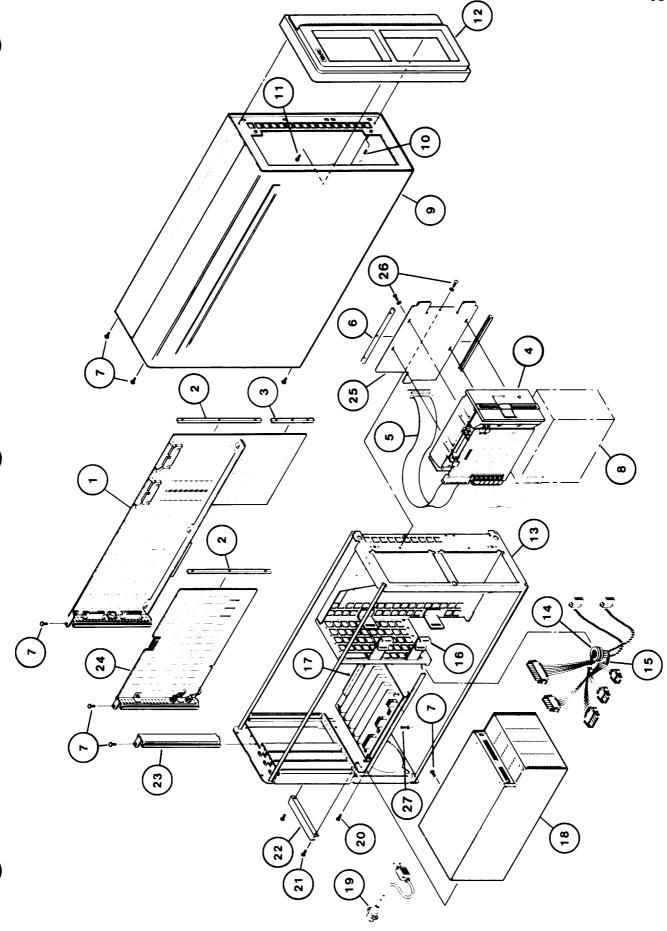

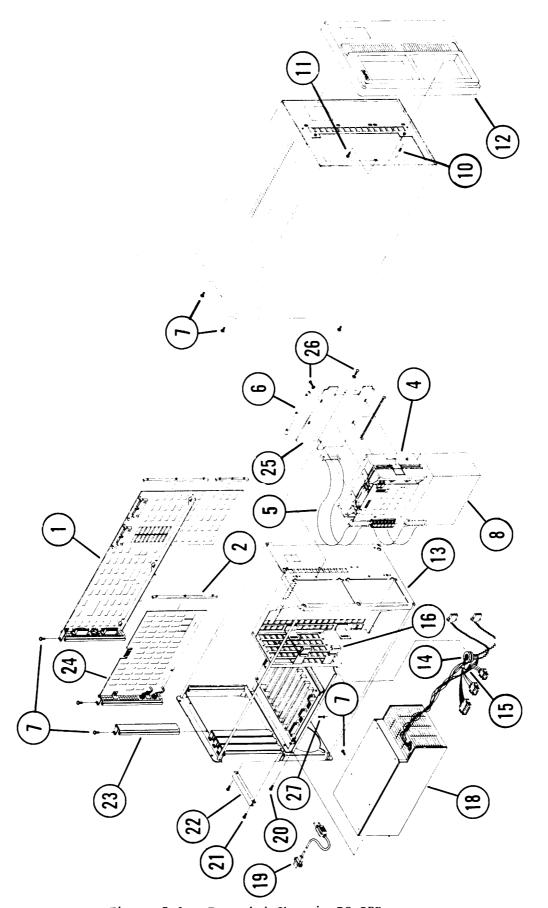

| 7-3               | CPU Electronics Enclosure IPB                     | 7-7  |

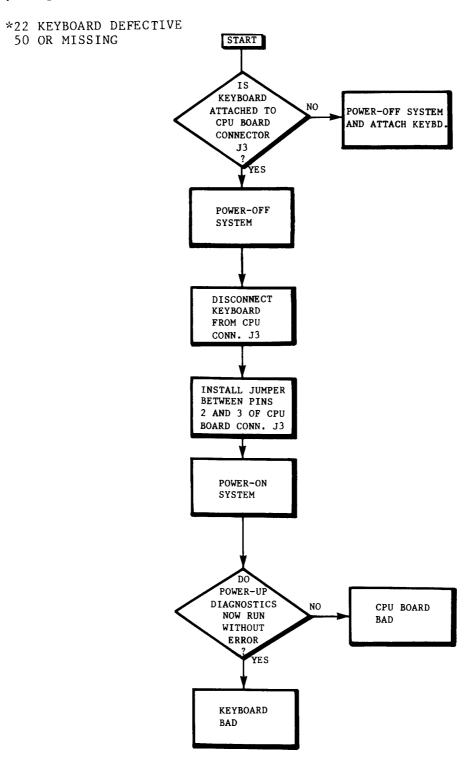

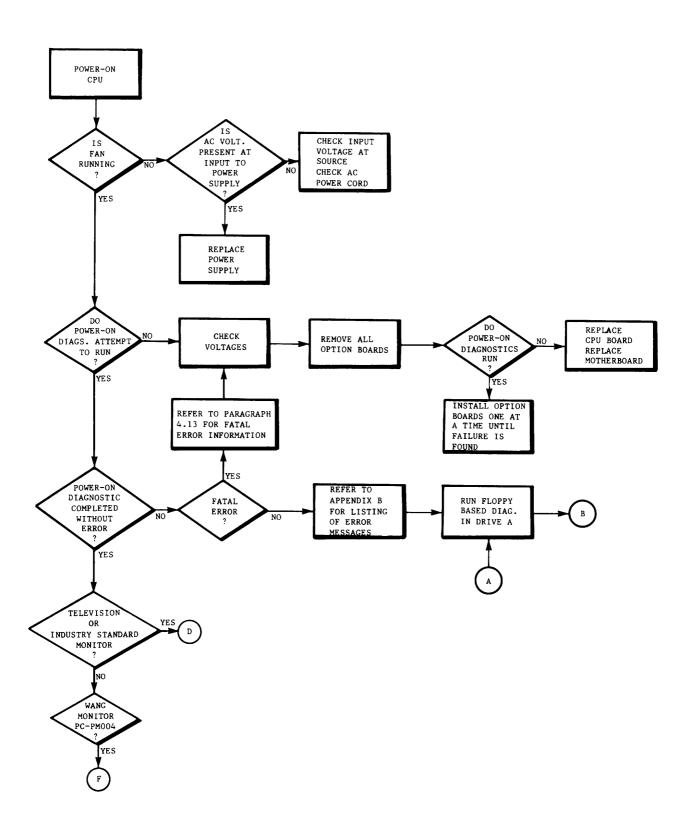

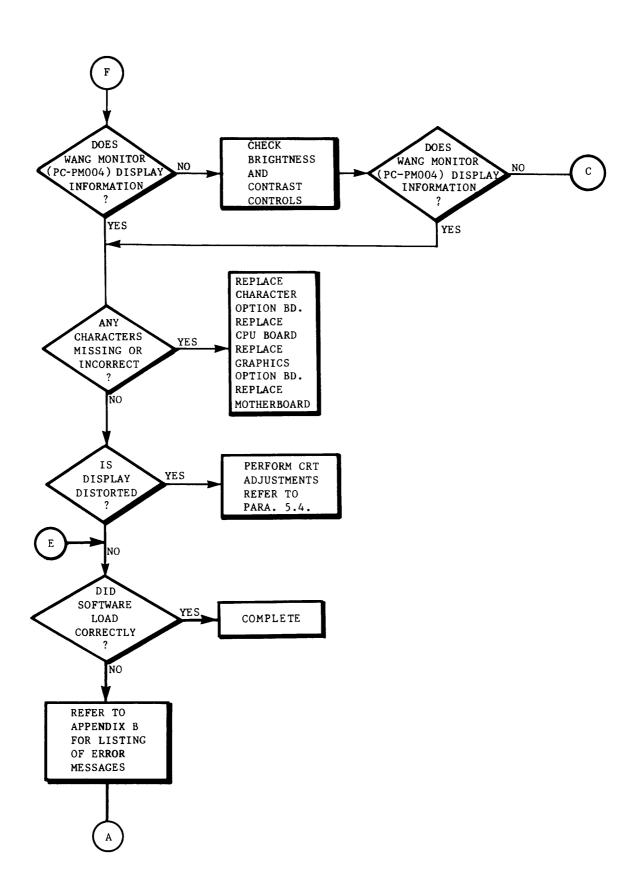

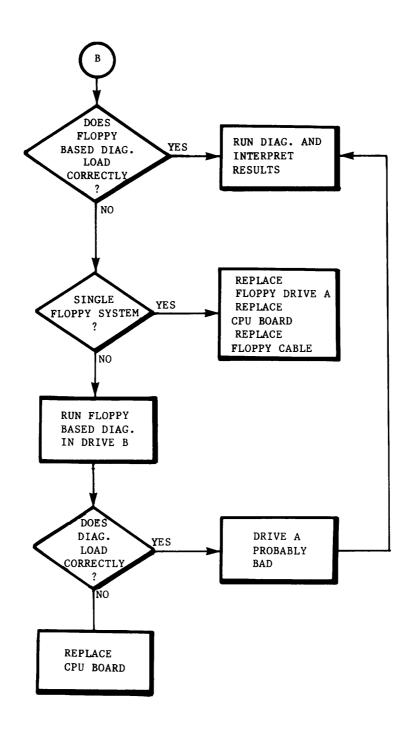

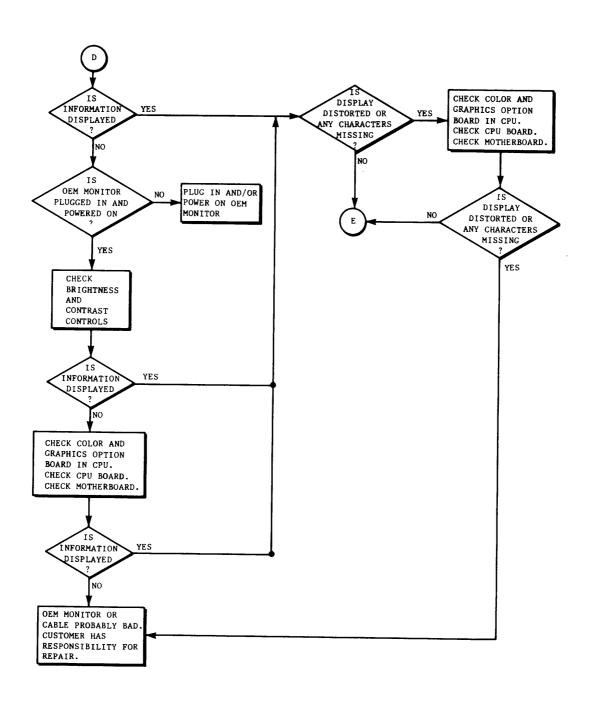

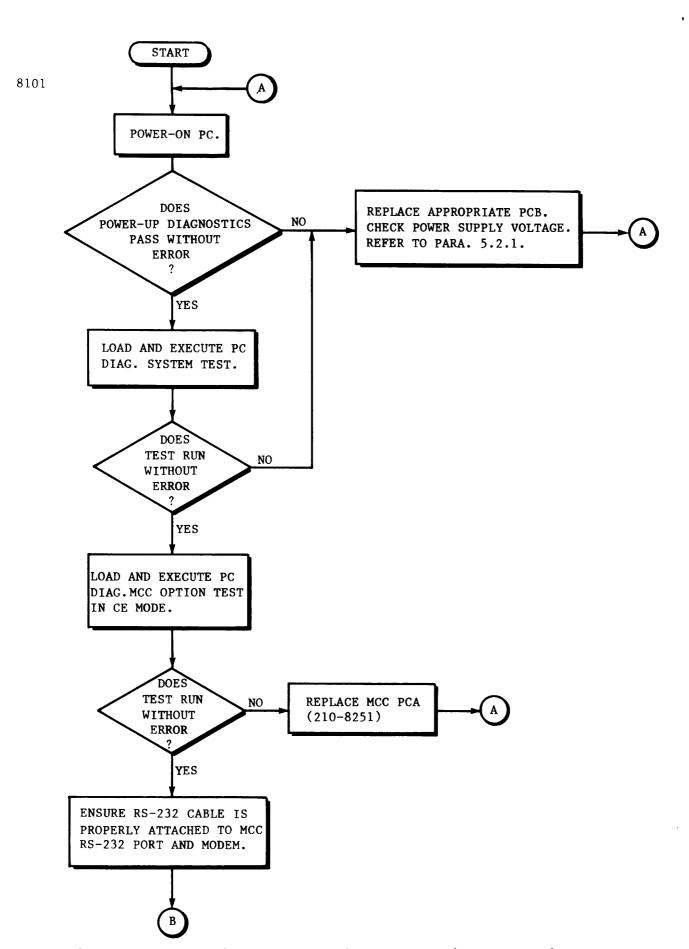

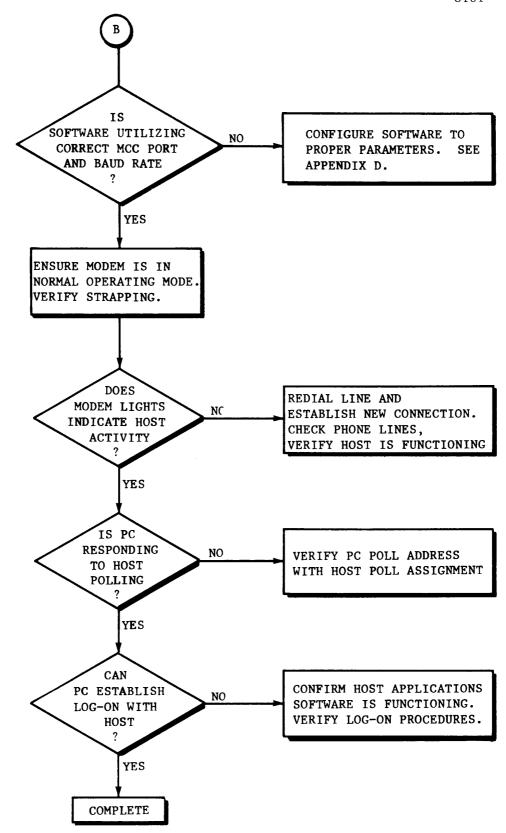

| 8-1<br>8-2<br>8-3 | Low Profile Keyboard Troubleshooting Flowchart    | 8-3  |

|                   | LIST OF TABLES                                    |      |

| TABLE             | TITLE                                             | PAGE |

| 1-1               | PC Software                                       | 1-2  |

| 1-2               | Wang User Documentation                           |      |

| 1-3               | Wang CE Maintenance Documentation                 |      |

| 1-4               | Keyboard Configurations                           |      |

| 1-5               | PC System Configurations                          | 1-10 |

| 2-1               | Status Bit Decoding                               | 2-14 |

| 2-2               | I/O Identification Codes                          |      |

| 2-3               |                                                   |      |

| 2-4               | Interrupt Request Flag Addresses                  |      |

| 2-5               | 2661 EPCI Mode Register 2                         |      |

| 2-6               | EPCI I/O Port Assignments                         |      |

| 2-7               | RS-232C Connector Pin Designation                 | 2-25 |

|                   | Floppy Disk Controller Commands                   | 2-26 |

| 2-8               | Parallel Port Pin Assignment                      | 2-27 |

| 2-9               | System Bus Pin Assignments (Expansion Slots Only) | 2-29 |

| 2-10              | Keyboard Connector Pin Assignment                 | 2-36 |

| 2-11              | Expanded Memory Board I/O Ports                   | 2-47 |

| 2-12              | Data Mode of Transfer Truth Table                 | 2-51 |

| 2-13              | Low Resolution Video Output Options               | 2-57 |

| 2-14              | Z80A I/O Ports                                    |      |

| 2-15              | 8086 I/O Ports LSB Only                           |      |

| 2-16              | Z80 Input Commands                                |      |

| 2-17              | Z80 Output Commands                               |      |

| 2-18              | 8086 Input Commands                               |      |

| 2-19              | 8086 Output Commands                              |      |

| 2-20              | RS232C Connector (J5) Pin Assignments             | 2-78 |

| 2-21              | AutoCall Connector (J1) Pin Assignments           | 2-80 |

| 2-22              | RTC 8086 I/O Ports                                | 2-84 |

| 2-23              | RTC Z80A I/O Port Addresses                       | 2-87 |

| 2-24              | RTC Vectored Z80A Interrupts in Order by Priority | 2-89 |

| 2-25              | Automatic Calling Unit Interface                  | 2-90 |

| 2-26              | Baud Rate Select Bit Pattern                      | 2-96 |

| 2-27              | 070/0 0 1                                         | 2-96 |

| 2-28              |                                                   | 2-98 |

| 2-29              | MCC Card Port 3 Pin Assignments                   | 2-99 |

| 4-1               | Baud Rate Selection Table                         | 4-26 |

| 4-2               | MX80FT TYPE III Switch Setting                    | 4-29 |

|                   | -                                                 | -    |

Wang Professional Computer

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 SCOPE

The Wang Professional Computer maintenance documentation is contained in a set of two (2) manuals; the PC Product Maintenance Manual (729-1190-B) and the PC Schematic Manual (729-1241).

The Product Maintenance Manual provides installation, theory of operation, installation and check-out procedures, corrective and preventive maintenance, removal and replacement procedures, and troubleshooting information for the Wang Professional Computer (PC) and its options. An IPB (illustrated parts breakdown) is provided to aid in locating and identifying all the PC's major components. An appendix is also included which contains a listing of cable assemblies, error messages, mnemonic codes, and System board Input/Output (I/O) address assignments.

The PC Schematic manual provides engineering schematics for the Professional Computer and its option boards.

The level of coverage in the Product Maintenance documentation is directed toward an Associate Field Engineering Technician (AFET) with a minimum of six months field experience who has received qualified PC training either directly from a Wang course instructor or indirectly via Wang video tape.

Included in this chapter are listings of applicable documentation (Software, User, and CE) related to the PC and its options. Also included is an overview of the standard PC equipment supplied and options available to further enhance and customize the PC to meet individual requirements.

A chart is included that contains five prepackaged configurations of the PC that can be ordered which include both standard and optional features.

A listing of the PC specifications is contained in paragraph 1.5. These specifications contain dimensions, net weight, power requirements, and environment conditions for the PC.

#### 1.2 APPLICABLE DOCUMENTATION

Table 1-1, 1-2, and 1-3 lists software, user documentation, and CE product maintenance documentation available for the PC respectively. Software and documentation can be ordered by writing to the address directly following the table.

Table 1-1. PC Software

| Model<br>Number | CEI<br>Number | Description                                                               |

|-----------------|---------------|---------------------------------------------------------------------------|

| PC-SS001        | 195-2326-9    | MS-DOS Operating System plus interpretive Basic                           |

| PC-SS010        | 195-2327-9    | MS Basic Compiler                                                         |

| PC-SS011        | 195-2328-9    | MS Pascal                                                                 |

| PC-SS012        | 195-2329-9    | MS FORTRAN                                                                |

| PC-SS013        | 195-2330-9    | MS COBOL                                                                  |

| PC-SS020        | 195-2331-9    | Async Communications (includes 2236DW Emulation)                          |

| PC-SS021        | 195-2332-9    | Remote Wangnet for VS (Leased line only)                                  |

| PC-SS030        | 195-2333-9    | Local Communications for VS (2246S only)                                  |

| PC-SS031        | 195-2334-9    | Local Communications for VS (2256C)                                       |

| PC-SS032        | 195-2335-9    | Local Communications for OIS (5536-4)                                     |

| PC-SS033        | 195-2336-9    | Local Communications/Alliance (5536-4)                                    |

| PC-SS060        | 195-2337-9    | 2780/3780/WPS Support For PC                                              |

| PC-SS063        |               | 3276 SNA/SDLC Software                                                    |

| PC-ASO01        | 195-2338-9    | PC Multiplan                                                              |

| PC-ASO02        | 195-2339-9    | PC Word Processing                                                        |

| PC-ASOO3        |               | PC Business Graphics                                                      |

| PC-AS004        |               | PC Data Base                                                              |

| PC-CS001        |               | Software Productivity Package (Includes PC-AS001, PC-AS002, and PC-SS020) |

|                 | 195-2459-9    | PC Diagnostics                                                            |

#### NOTE

# ADDITIONAL SOFTWARE UPDATES WILL INCUR A NOMINAL CHARGE.

All software can be ordered by writing to the following address:

WANG LABORATORIES INC. Software/Literature Control Centers Building 4-1 M/S 2428 836 North Street Tewksbury, MA 01876

Table 1-2. Wang User Documentation

| Document<br>Number | Title                                       | Information Contained                                                                                                                                                                        |

|--------------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 700-7589           | Documentation Guide                         | Directory of all user documentation.                                                                                                                                                         |

| 700-7590           | Introductory Guide                          | Basic introduction to the PC.                                                                                                                                                                |

| 700-7592           | BASIC Language Guide                        | BASIC programming for the PC.                                                                                                                                                                |

| 700-7593           | Program Development<br>Guide                | Programmer's guide to technical features of the PC.                                                                                                                                          |

| 700-7558           | Communications Guide                        | A three part manual consisting of:<br>How to use the teletypewriter emulation<br>feature, operation of the Wang 2236DW<br>Terminal emulation feature, and<br>Programmer Support subroutines. |

| 700-7588           | Word Processing<br>Manual<br>Set of 2 books | A reference guide to specific Word Processing operations.                                                                                                                                    |

|                    |                                             | A training manual designed for users not familiar with Wang Word Processing.                                                                                                                 |

| 700-7600           | PC Multiplan Manual<br>Set of 2 books       | A Multiplan Training Guide for user creation of a sample spreadsheet.                                                                                                                        |

|                    |                                             | A Multiplan Reference Guide that provides specific information on the command functions and procedures necessary to use Multiplan effectively.                                               |

| 700-7594           | Compiled Basic<br>Reference Guide           | A reference guide for Compiled Basic Programming.                                                                                                                                            |

| 700-7595           | FORTRAN Reference<br>Guide                  | A reference guide for FORTRAN programming.                                                                                                                                                   |

| 700-7596           | PASCAL Reference<br>Guide                   | A reference guide for PASCAL programming.                                                                                                                                                    |

| 700-7597           | COBOL Reference<br>Guide                    | A reference guide for COBOL programming.                                                                                                                                                     |

| 700-7598           | Assembler Reference<br>Guide                | A reference guide for Assembler language programming.                                                                                                                                        |

| 700-8319           | SNA 3276 Emulator<br>Users Guide            | A reference guide for Systems Network Architecture (SNA) communications.                                                                                                                     |

Domestic and Canadian field personnel can order User documentation by submitting a withdrawal request to the following address:

WANG LABORATORIES INC. General Services M/S 1183 51 Middlesex Street No. Chelmsford, MA 01863

International field personnel can order User documentation by submitting a withdrawal request to the following address:

WANG LABORATORIES INC.

International Documentation Coordinator

M/S 1151

1 Industrial Avenue

Lowell, MA 01851

Table 1-3. Wang CE Maintenance Documentation

| Document<br>Number | Title                                          | Information Contained                                                                                         |

|--------------------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| 729-0000-В         | Documentation Control and Processing Catalog   | Contains listings of available CE documentation.                                                              |

| 729-0976-A         | CE Reprint For Epson<br>MX80 Printer           | A technical manual that contains the electrical and mechanical operations and repair of Epson MX80 Printer.   |

| 729-1241           | PC Schematic Manual                            | Schematics pertaining to the PC.                                                                              |

| 729-1241-1         | PC Schematic Update                            | Update to Schematic manual 729-1241.                                                                          |

| 7 <b>2</b> 9-1114  | CE Reprint for Flexible<br>Disk Drive 51/52    | A technical manual that contains the electrical and mechanical operations of the 51/52 Disk Drive.            |

| <b>72</b> 9–1167   | CE Reprint For Tandon<br>TM-100-1/2 Disk Drive | A technical manual that contains the electrical and mechanical operations and repair of Tandon 100-1/2 Drive. |

| 729-1054           | Daisy Printer DW20                             | A Wang PMM Manual on the repair and maintenance for DW20 Printer.                                             |

All CE Maintenance documentation can be ordered by writing to the following address:

WANG LABORATORIES INC. c/o (Your Area Representative) 437 So. Union Street Lawrence, MA 01843

#### 1.3 SYSTEM DESCRIPTION

The low-cost Wang PC is a high performance, highly modular computer system which features both data and word processing capabilities. It can operate in a stand-alone mode, through coaxial cable to other Wang products, through telephone lines to Wang and non-Wang products, and through Wangnet.

The PC comes with many standard features and a host of optional features. This section describes each of these features and identifies the related product code (PC) for that feature.

# 1.3.1 Standard Equipment Supplied

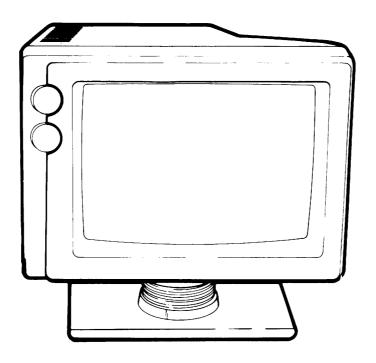

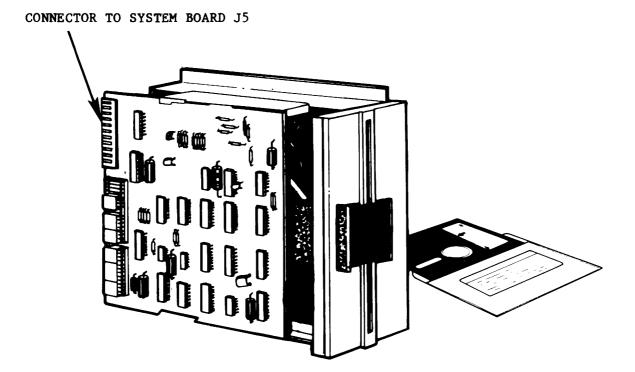

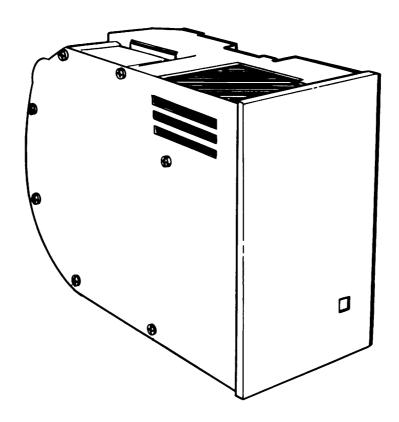

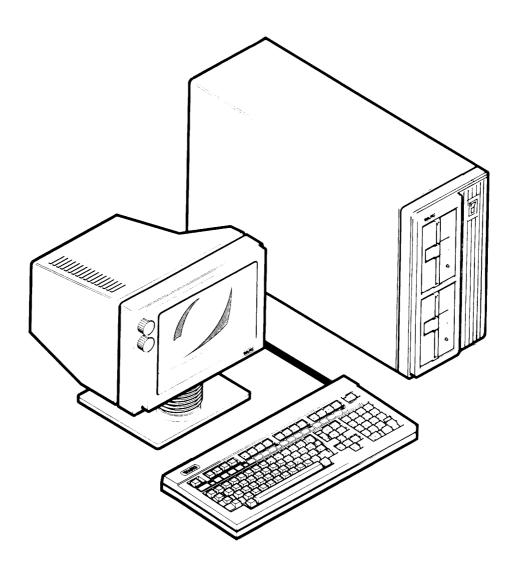

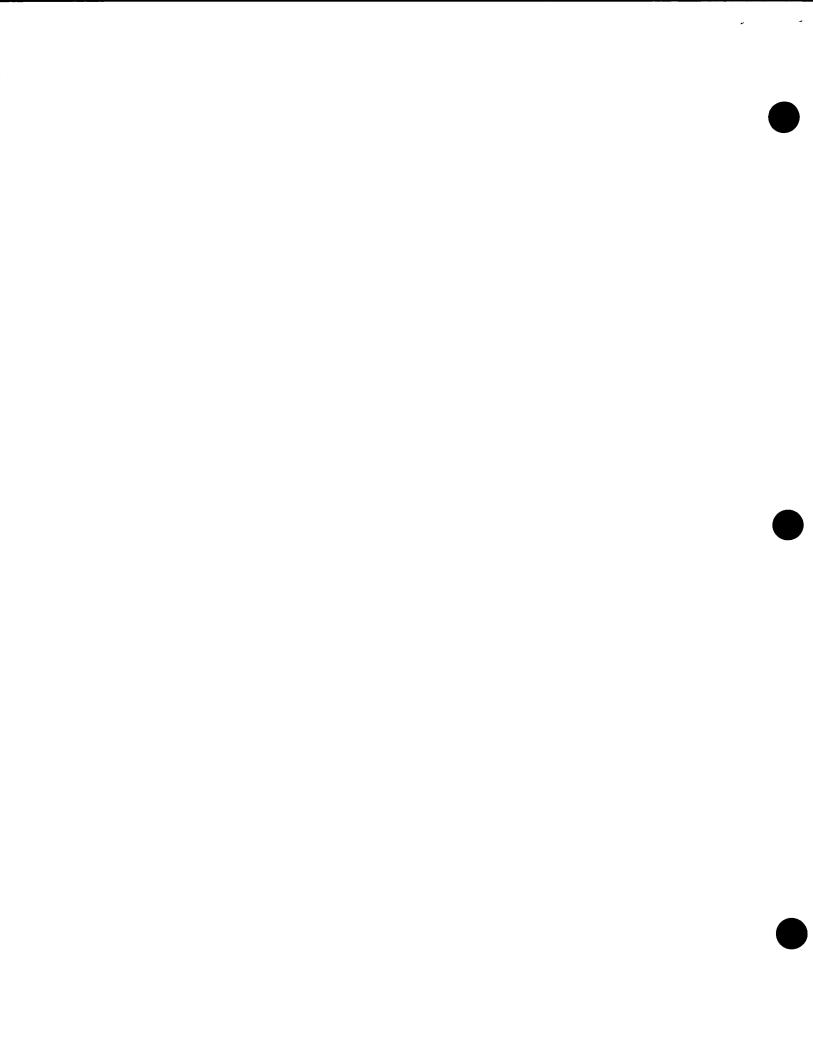

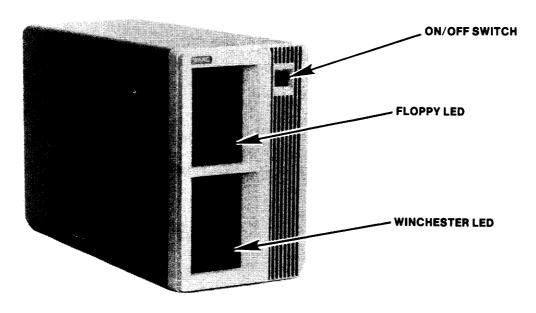

The standard base unit PC (PC-001) is equipped with an Electronics unit, a Low-Profile Universal Keyboard, and a 5-1/4" Floppy Diskette Drive. See Figure 1-1.

Figure 1-1. PC Standard Equipment (PC-001)

## 1.3.1.1 Electronics Enclosure (PC-001)

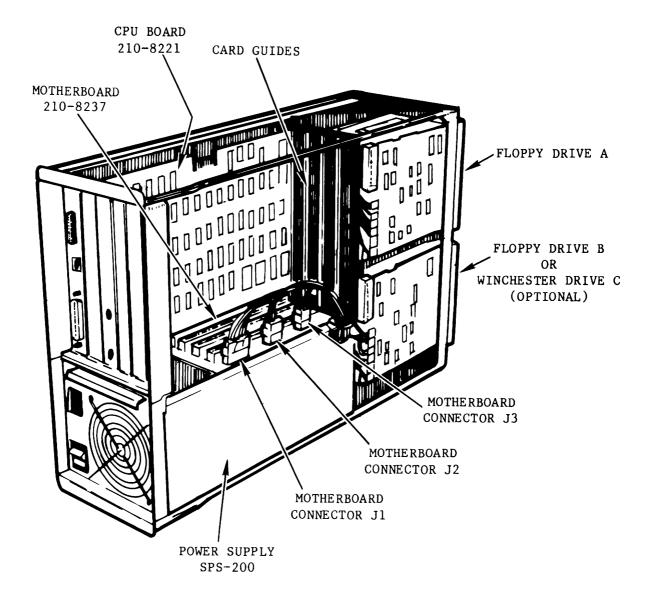

The Electronics Enclosure is compact, lightweight, and can control a variety of I/O devices. The Electronic Enclosure houses the 210-8221 CPU board, the 210-8237 Motherboard, the System Floppy Drive, an optional Floppy Drive or Winchester Disk Drive, the SPS-200 Switching Power supply, and up to five option boards. The Electronics Enclosure (PC-001) comes equipped with the following:

- o A standard 128KB of Parity-Checked memory for user programs.

- o Three channel direct memory access (DMA) capability.

- o A program-addressable internal clock.

- o An RS-232C asynchronous interface that supports serial devices and communications.

- o A Centronics-compatible parallel printer interface.

- o A standard 360KB Floppy Diskette Drive.

- A keyboard interface.

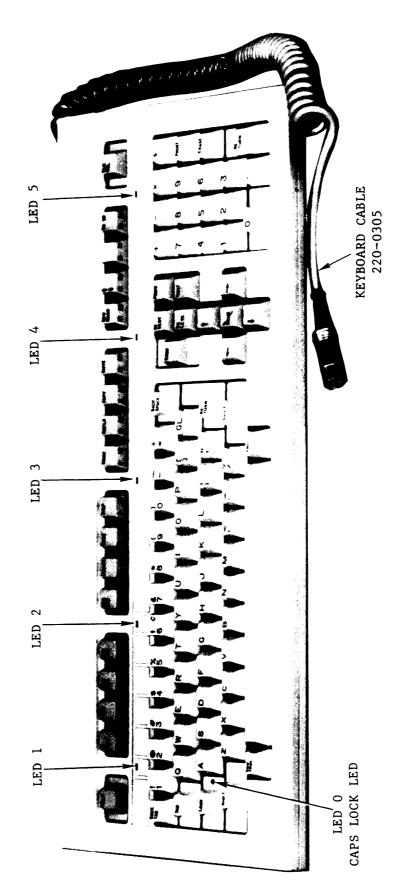

#### 1.3.1.2 Low-Profile Universal Keyboard (UNI/KBD-xx)

At present, five keyboard configurations are available for the PC. Refer to the following table:

Table 1-4. Keyboard Configurations

| WLI No.                                                                 | MODEL No.                              | DESCRIPTION                                                                                                                                                                                             |

|-------------------------------------------------------------------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 279-2042-US<br>279-2042-UK<br>279-2042-SL<br>279-2042-AZ<br>279-2044-GE | UNI/KBD-UK<br>UNI/KBD-SL<br>UNI/KBD-AZ | KYBD UNIV KTC LOW PROF (UNITED STATES) KYBD UNIV KTC LOW PROF (UNITED KINGDOM) KYBD UNIV KTC LOW PROF (SPANISH-LATIN AMERICAN) KYBD UNIV KTC LOW PROF (AZERTY) KYBD UNIV EXP LOW PROF (GERMAN EXPANDED) |

The Low-Profile Keyboard is a separate, detachable keyboard that contains 101 keys and a programmable speaker that can produce three simultaneous tones. The keyboard offers 16 programmable function keys, a HELP key, four cursor control keys (North Arrow, South Arrow, East Arrow, and West Arrow), as well as a calculator style key pad. Standard word processing Edit keys are also supported (eg. Insert, Delete, Move, Copy). A wide range of international character sets are supported and access to the complete 234 character set is provided.

#### 1.3.1.3 Floppy Diskette Drive

One 5 1/4 inch Floppy Diskette Drive capable of 360K Bytes (the diskette controller is located on the CPU Board) is included with the base system. A second Floppy Diskette Drive (optional) can be installed in the base unit to provide an additional 360KB of storage. The optional Floppy Drive is controlled by the same diskette controller located on the CPU board.

#### 1.3.2 OPTIONS

Many system options can be attached to further enhance the PC Base unit. Restrictions apply to some options. These restrictions will be discussed in respect to those particular options.

#### 1.3.2.1 Monochrome Display (PC-PM004)

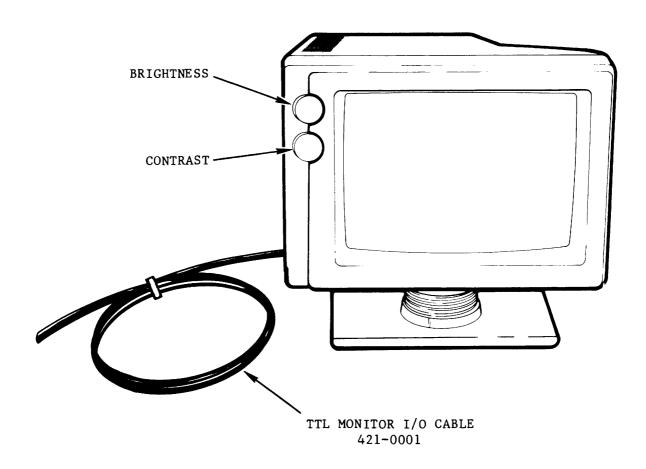

The Wang monochrome display is mounted on a pedestal base. This allows the user to rotate the device for ease in viewing. The display can be either placed on a flat surface (ie. desk top or on the top of the Electronics Enclosure when its position horizontally) or can be mounted on the optional pivot arm.

The pivot arm can be clamped to the side of a desk which allows the user to move it up to 14 inches off the desk at any angle or position.

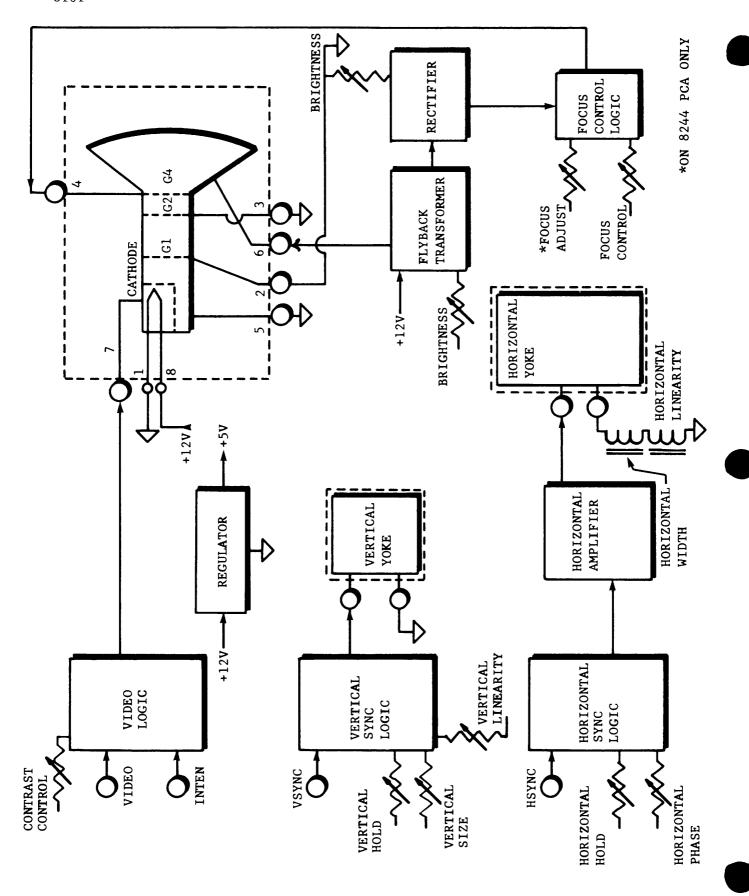

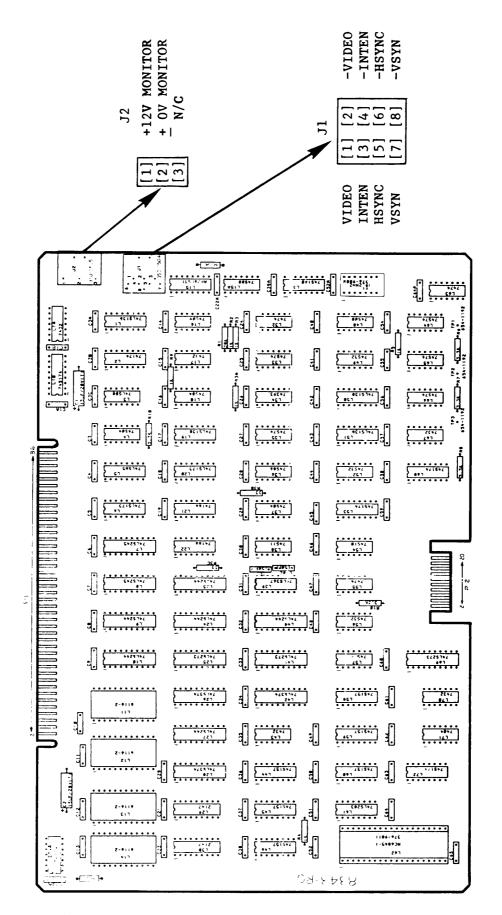

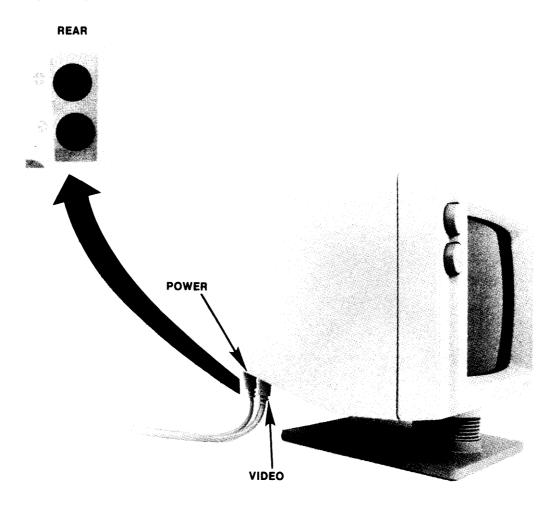

The monitor's CRT is a 12 inch green-on-black diagonal screen that has a display area of 80 columns by 25 rows. The monitor must be used with either the Character Display Adapter (210-8243/8343) or the Character Display Adapter in conjunction with the Graphics Display Adapter (210-8233). Both adapters are further described below.

The monitor houses the CRT, the CRT monitor board, and a flyback transformer. The monitor's power is supplied through the monitor cable from the SPS-200 Power Supply.

# 1.3.2.2 Character Display Adapter (PC-PM001)

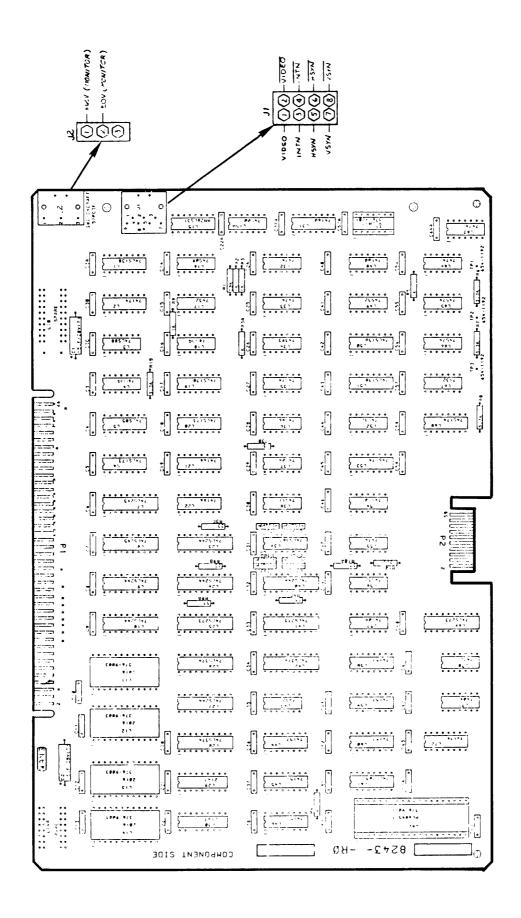

The Character Display Adapter is necessary to drive the Wang Monochrome display to generate the characters. The character resolution is 80 columns by 25 rows. This adapter is plugged into one of the five option slots within the Electronics Enclosure and is connected to the monitor via a dual cable. The monitor cable supplies the monitor with the operating voltages via one cable of the dual cable and the TTL Video via the other cable.

#### 1.3.2.3 Graphics Display Adapter (PC-PM002)

The Graphics Display Adapter is necessary to drive the Wang Monochrome display to generate graphics. This adapter MUST be used in conjunction with the Character Display Adapter. When the Graphics Display Adapter is used with the Character Display Adapter, graphics with a resolution of 800 X 300 pixels as well as characters can be displayed. This adapter is plugged into one of the five option slots within the Electronics Enclosure and is cable-connected to the Character Display Adapter. Due to the cable length, the Graphics Resolution PCB must be installed adjacent to the Character Display PCB.

# 1.3.2.4 Color and Graphics Display Adapter (PC-PM003)

The Color and Graphics Display Adapter is necessary to control a Customer purchased output display device. The following four types of output devices can be driven by this adapter:

- o U.S. standard NTSC B&W Television with attached RF modulator.

- o U.S. standard NTSC Color Television with attached RF modulator.

- o B&W Video Monitor.

- o RGB Color Video Monitor.

Industry standard frequencies are supported. The display resolution, display area, and character size will vary depending on the attached output display device. This adapter is plugged into one of the five option slots within the Electronics Enclosure and is cable-connected to the output display device.

#### 1.3.2.5 Memory Expansion Cards

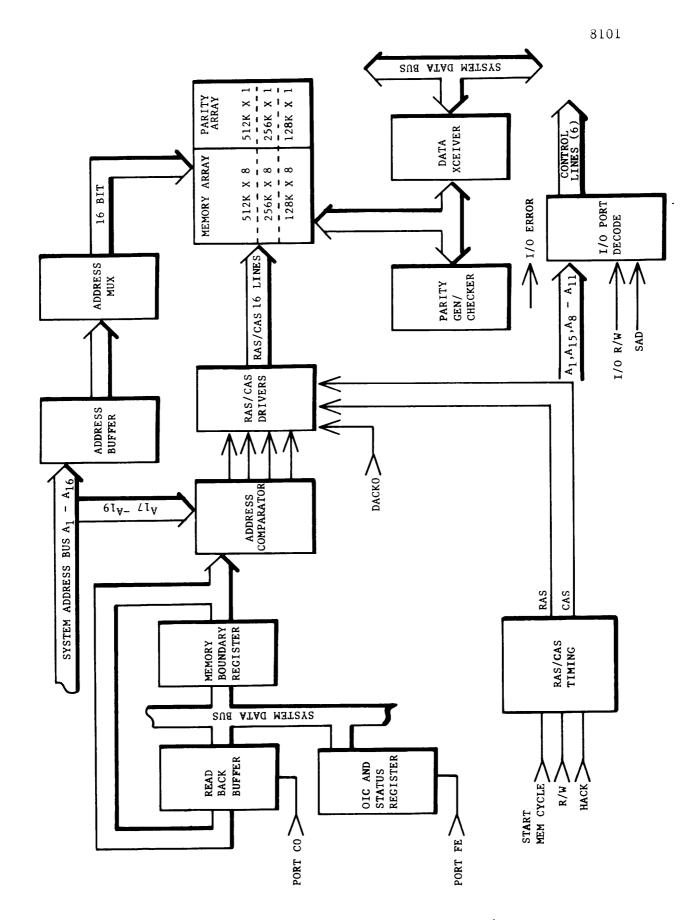

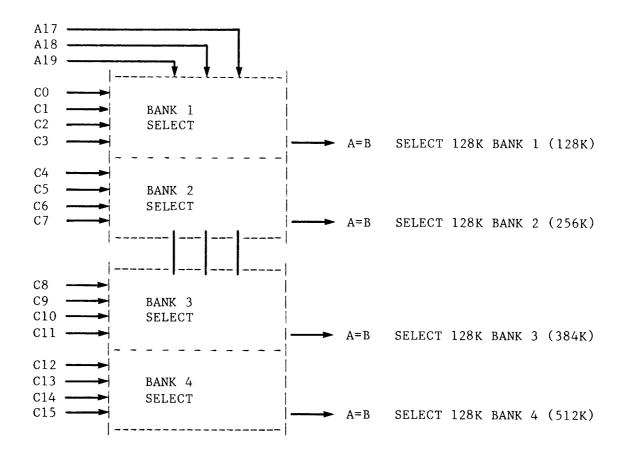

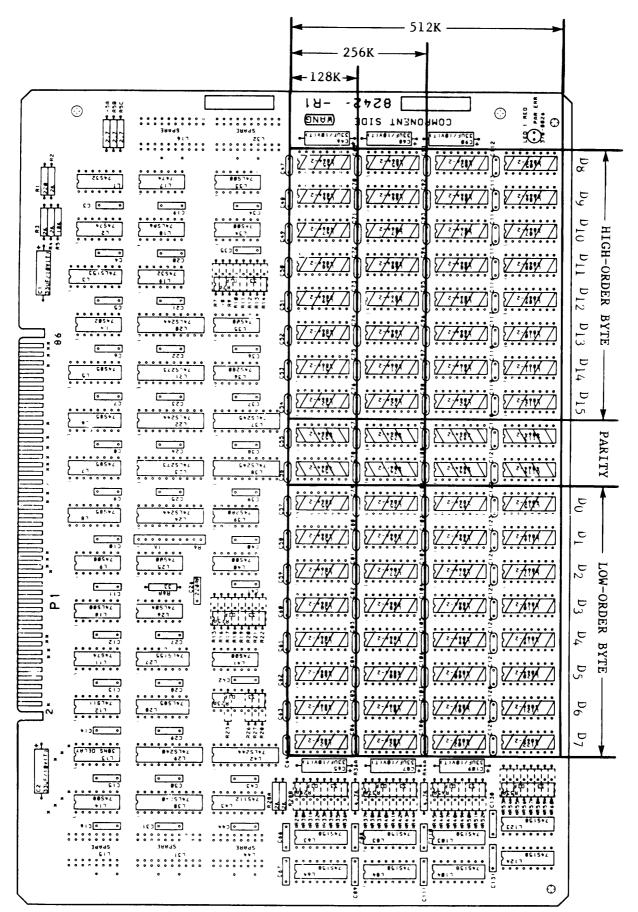

The base system PC contains 128K of dynamic RAM memory within eighteen 64K RAM devices located on the 210-8221 PCB. To increase the program and data storage capabilities of the PC, a Memory Expansion card with additional dynamic RAM chips can be installed into one of the five option slots in the Electronics Enclosure unit. This option provides an additional 128K (PC-PM030), 256K (PC-PM031), or 512K (PC-PM032) of dynamic RAM to increase total memory capacity to either 256K, 384K, or 640K respectively.

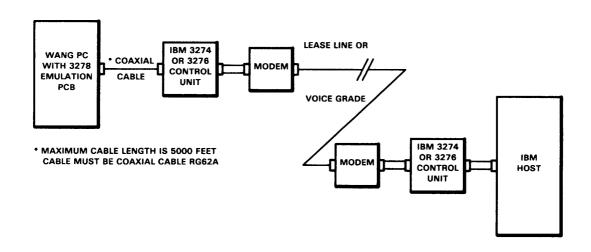

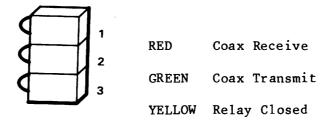

#### 1.3.2.6 Remote Communications (PC-PM040)

The Remote Communications option provides synchronous communications capabilities. This permits the PC to communicate through Wangnet to any Wangnet system or through a modem with auto-call feature to most any CPU system.

#### 1.3.2.7 Local Communications (PC-PM041)

The Local Communications option provides 928-type workstation emulation for utilization by the PC. This option consist of two PCB boards interconnected through a ribbon cable. One board operates as a Datalink/Memory board operated directly from the PC's 8086 CPU, the other contains the circuitry necessary to allow operation of programs written for VS and OIS applications. These boards should occupy adjacent bus slots due to the interconnect cable length.

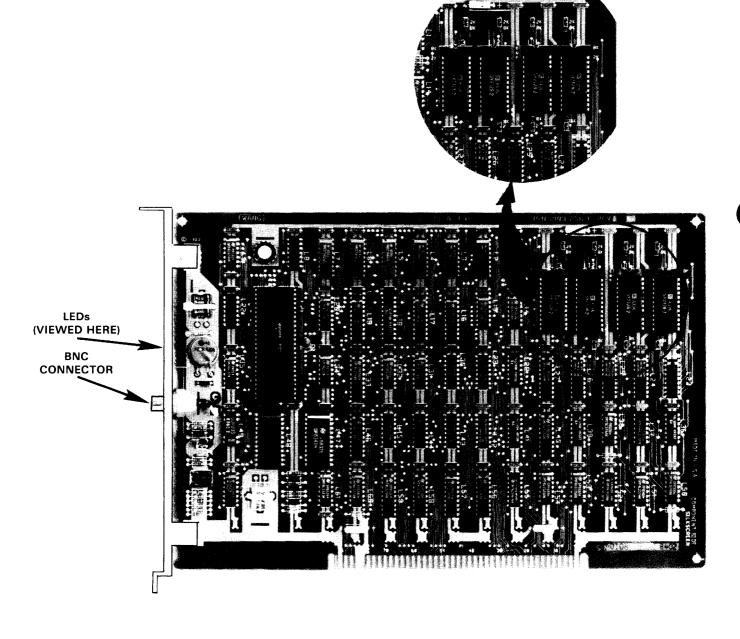

#### 1.3.2.8 CP/M-80 Emulation Board (PC-PM050)

The CP/M-80 Emulation board allows the Wang PC to emulate the CP/M-80 operating system. This board can be installed into any of the five option slots in the Electronics Enclosure unit.

# 1.3.2.9 10MB Winchester Disk Drive and Adapter Board (PC-PM021)

A 5 1/4 inch Winchester Disk Drive can be installed in the base unit. The drive is housed in the same location in the base unit that is reserved for a second Floppy Drive. Either the second Floppy Drive or the Winchester can be installed, but not both. The Winchester Controller board must be installed in <u>SLOT 5 ONLY</u> (J9) of the Electronics Unit. This restriction is due to cabling required for the Winchester Drive. The Winchester Drive (when installed) is designated as Drive C.

## 1.3.2.10 20-CPS Daisy Printer (PC-PM011)

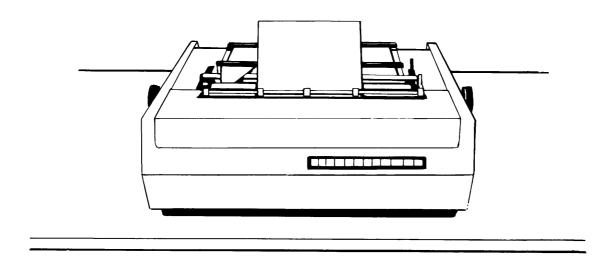

The DW20 Daisy printer is a bidirectional printer that operates at 20 cps (characters per second). This printer can print up to a 132 character line at 10 pitch and a 158 character line at 12 pitch.

The printer's character set contains 96 characters including uppercase and lowercase letters, numbers and special characters and symbols. The DW20 printer connects via a cable to the Base system's parallel port. Refer to the Daisy Printer DW20 manual (WLI P/N 729-1054) for printer specifications.

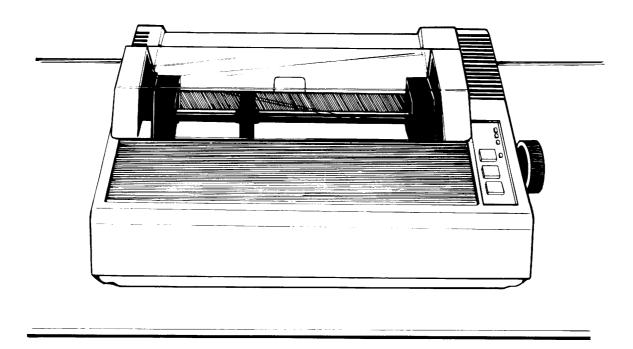

# 1.3.2.11 80-CPS Matrix Printer (PC-PM010)

The MX-80FT TYPE III Printer is a compact, bidirectional matrix printer that operates at 80 cps. The matrix printer is best suited for producing low volume draft quality output and graphics. Each pin on the printhead's font can be controlled as the print head moves across the paper. This enables the printer to print pictures, plot graphs, or create special character sets. The MX-80FT TYPE III printer connects via a cable to the Base System's parallel port. Refer to the CE Reprint For The Epson MX80 Printer (WLI P/N 729-0976) for printer specifications.

#### 1.3.2.12 Monitor Clamp and Arm (PC-AC001)

This optional accessory is available to provide free movement and best placement for operator use of the Monitor. The arm can elevate the monitor 14 inches (35.56 cm) above the desk and pivot 25 to 30 degrees around its base. The clamp can be fastened to either side of a desk or table that has a 1 inch (minimum) to 2 inch (maximum) lip.

# 1.3.2.13 System Unit Clamp (PC-AC002)

This optional accessory is available to provide attachment of the Electronic Enclosure unit to a desk or a table. The clamp can be used for right or left side mounting on a desk or a table that has a 1 inch (minimum) to 2 inch (maximum) lip.

## 1.3.2.14 Additional Floppy Diskette Drive (PC-PM020)

A second Floppy Diskette Drive (optional) can be installed in the base unit to provide an additional 360KB of storage. This second Floppy Drive is controlled by the same diskette controller as fore mentioned in paragraph 1.3.1.3 Floppy Diskette Drive. This Drive is designated as Drive B.

#### 1.4 SYSTEM CONFIGURATIONS

The PC is available in a number of configurations that can be tailored to meet specific customer requirements. At present, five prepackaged configurations made up of both standard and optional features can be ordered. These are delivered preassembled so that the customer does not have to install the adapter boards thereby minimizing the requirements of ordering, configuring, and setting up the delivered system. When ordering a particular PC configuration, the number of option slots must be considered since there are only five option slots available on the base unit. Customers may order more than five options, however; only five may be installed at any one time. Some option boards have particular restraints that will be discussed in detail in Chapter 2. Table 1-5 lists the five available PC configurations.

Table 1-5. PC System Configurations

| 1                                                   |           |            | PC-         |             |             |

|-----------------------------------------------------|-----------|------------|-------------|-------------|-------------|

| HARDWARE/SOFTWARE                                   | 001       | <u>002</u> | <u>003B</u> | <u>004A</u> | <u>005A</u> |

| Base System Unit with 128k Memory                   | x         | x          | X           | X           | x           |

| 360K Floppy Disk Drive                              | !<br>  X  | X          | X           | X           | Х           |

| Low Profile Keyboard                                | X         | X          | X           | X           | Х           |

| MS/DOS Operating System (Plus<br>Interpreter Basic) | X<br>  X  | X          | X           | X           | X           |

| MS/Compiled Basic                                   | X         | x          | x           | x           | X           |

| PC-PM001 Character Display Adapter                  |           | X          | X           | X           | x i         |

| PC-PM004 Monochrome Display                         | <br>      | X          | X           | X           | х           |

| PC-PM020 Second 360K Floppy Drive                   |           |            | X           | X           | <br>        |

| PC-PM002 Graphics Display Adapter                   |           |            |             | X           | х           |

| PC-PM030 Additional 128K RAM                        |           |            |             |             | х           |

| PC-PM021 Winchester 10MB Disk Drive (with Adapter)  | <br> <br> |            |             |             | X           |

# 1.5 SYSTEM SPECIFICATIONS

# Dimensions

#### Electronics Enclosure

| Width  | 14.9 | inches | (37.8 | cm) |

|--------|------|--------|-------|-----|

| Length | 23.1 | inches | (58.7 | cm) |

| Height | 6.5  | inches | (16.5 | cm) |

#### Monitor Assembly

| Height | 11.8 inches | (30.0  cm) |

|--------|-------------|------------|

| Width  | 13.0 inches | (33.0 cm)  |

| Depth  | 10.8 inches | (27.4 cm)  |

#### Keyboard Assembly

| Height | 1.7  | inches | (4.3  | cm) |

|--------|------|--------|-------|-----|

| Width  | 18.3 | inches | (46.5 | cm) |

| Depth  | 7.8  | inches | (19.8 | cm) |

# Net-Weight

| Electronics Enclosure | 27.8 lb | (12.6  kg) |

|-----------------------|---------|------------|

| Monitor Assembly      | 14.0 lb | (6.4  kg)  |

| Keyboard Assembly     | 4.5 lb  | (2.0  kg)  |

#### Power Requirements

| Minimum     | Nominal | Maximum | Frequency   |

|-------------|---------|---------|-------------|

| 90 <b>v</b> | 115v    | 132v    | 47 - 63  Hz |

| 180v        | 230v    | 264v    | 47 - 63 Hz  |

#### Wattage

330 watts at 115 volts 330 watts at 230 volts

#### Amperage

3.0 Amps at 115 volts1.5 Amps at 230 volts

#### Operating Environment

Ambient Temperature 60 deg. F to 90 deg. F (16 deg. C to 32 deg. C)

## Heat Dissipation

870 BTU per Hour

# Non-operating Environment

Temperature 50 deg. F to 104 deg. F (10 deg. C to 40 deg. C) Relative Humidity -- 20% to 80% (noncondensing)

# Cabling

DW20 Printer Cable not to exceed 25 feet (7.6 meters) MX80 Printer Cable not to exceed 25 feet (7.6 meters)

#### CHAPTER 2

#### THEORY

#### 2.1 INTRODUCTION

This chapter contains the theory of operation of the PC system structure as well as individual PCBs operation and interface. The PCB theory consists of the PCBs required for PC configuration PC-002. Option PCBs theory is discussed in the latter part of this chapter.

The following discussion of the WANG Professional Computer is sectionalized into its main block functions. Block diagrams are used in conjunction with the text for references within the discussion. Reference will also be made to the schematics pertaining to the PCB being discussed. Mnemonic codes are defined during the discussion and an Alphanumeric listing of mnemonic codes is contained in Appendix C.

#### 2.2 SYSTEM FUNCTIONAL DESCRIPTION

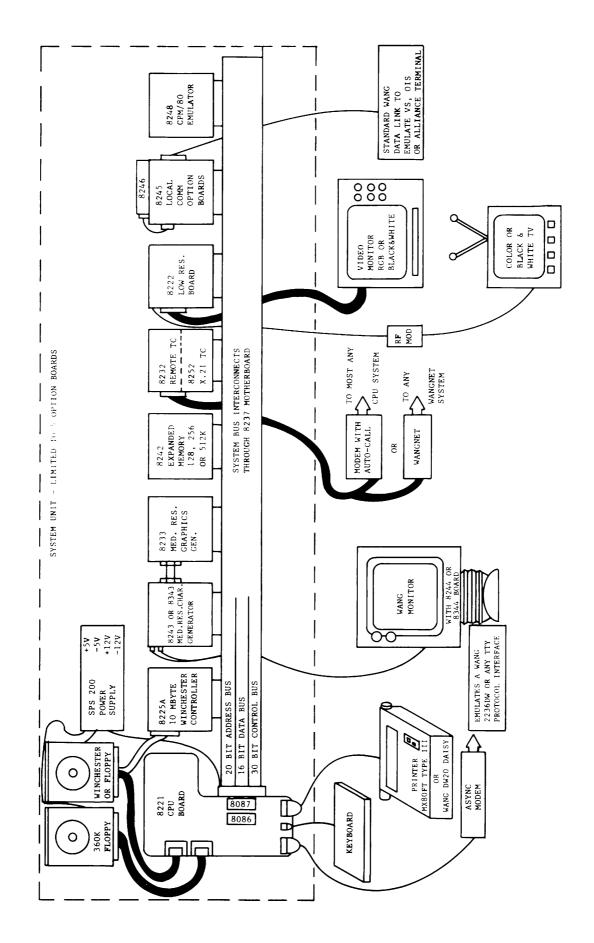

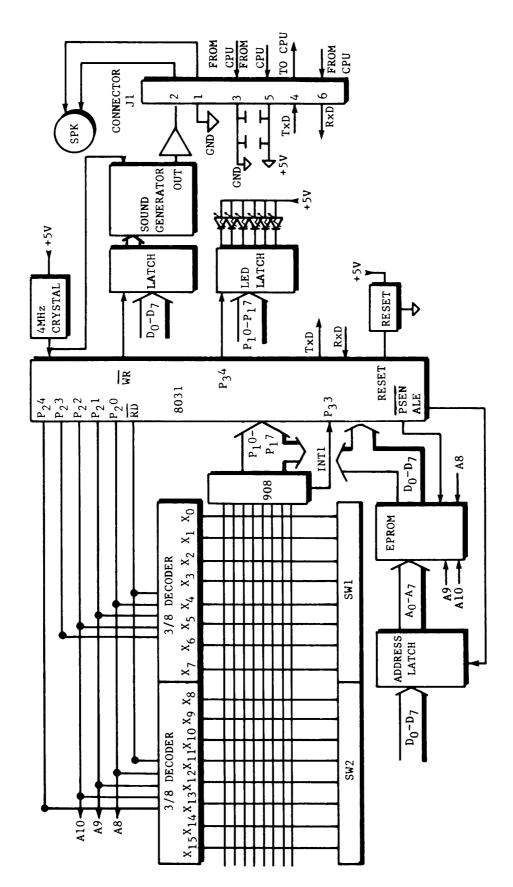

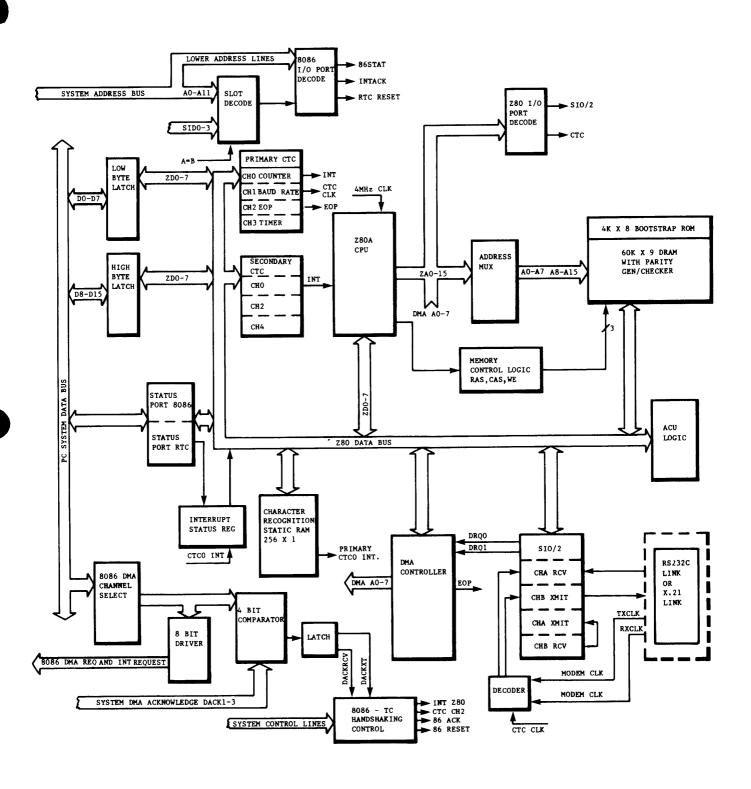

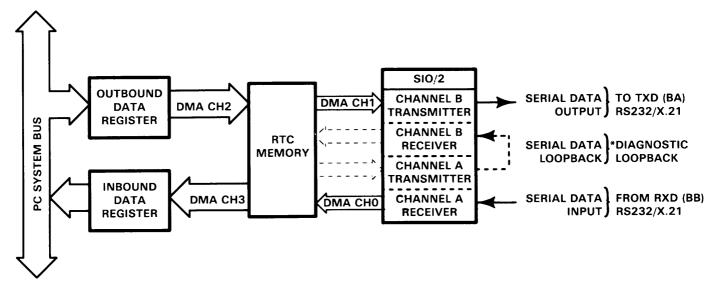

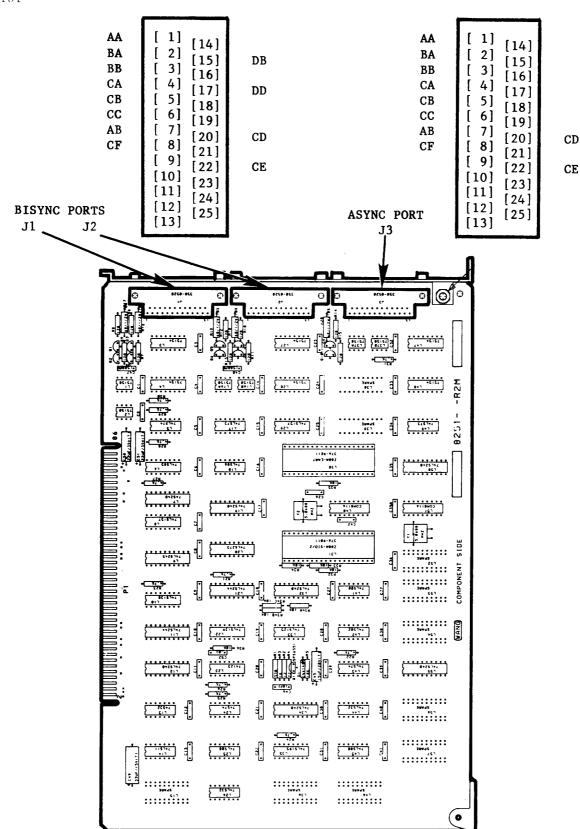

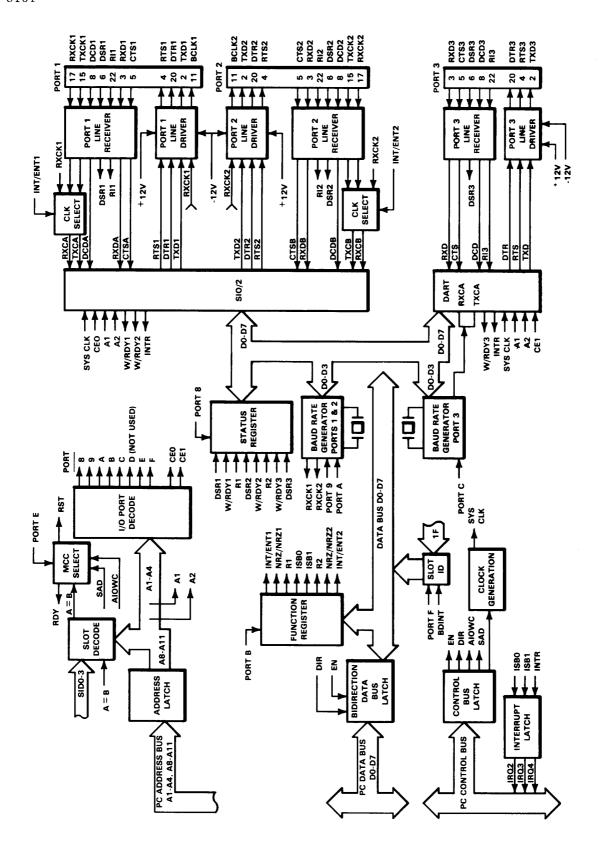

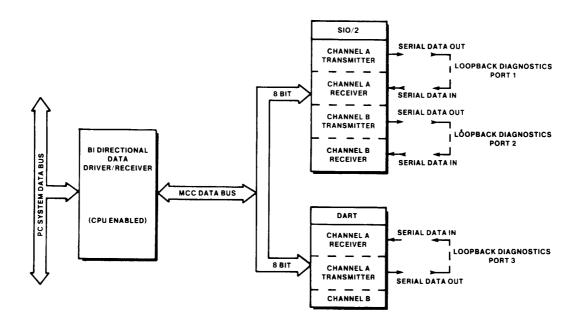

For the following discussion refer to the System Block Diagram, Figure 2-1. Each of the blocks will be discussed separately.

The System Unit consists of the following components:

- o CPU Board (210-8221)

- o SPS200 Power Supply

- o Motherboard (210-8237)

- o 360K Floppy Drive

- o Medium Resolution Character Generator (210-8243/8343)

- o Low-Profile Serial Keyboard

- o Wang Monitor

- o Option Boards

- o External Options

#### 2.2.1 8221 CPU Board

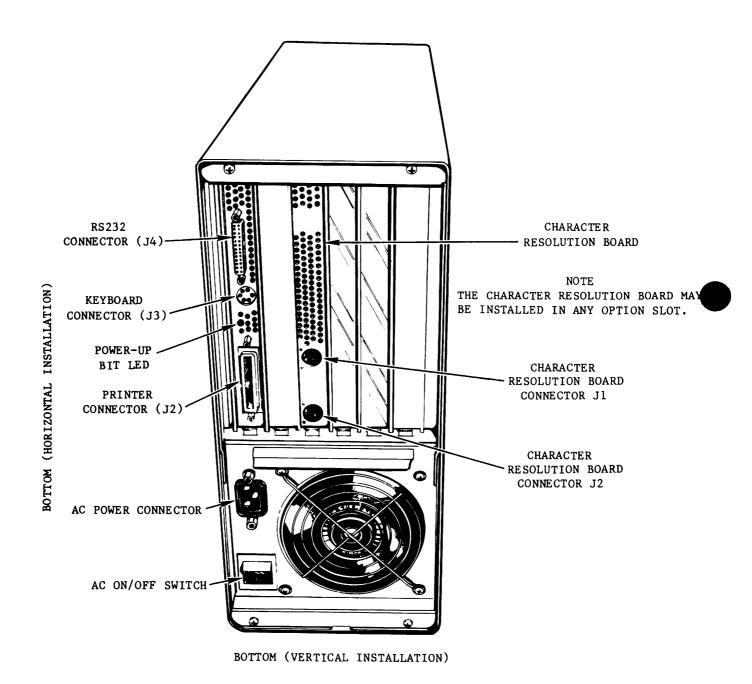

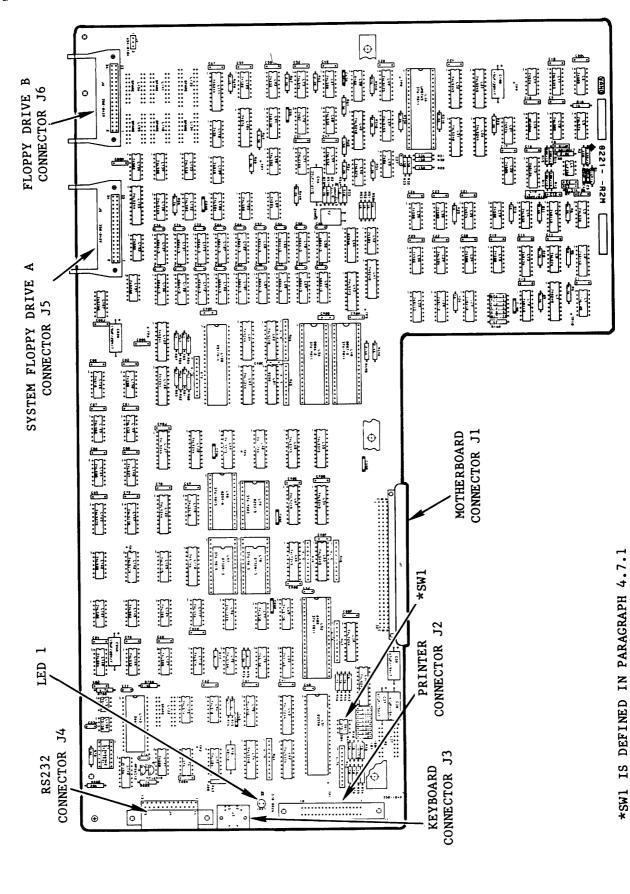

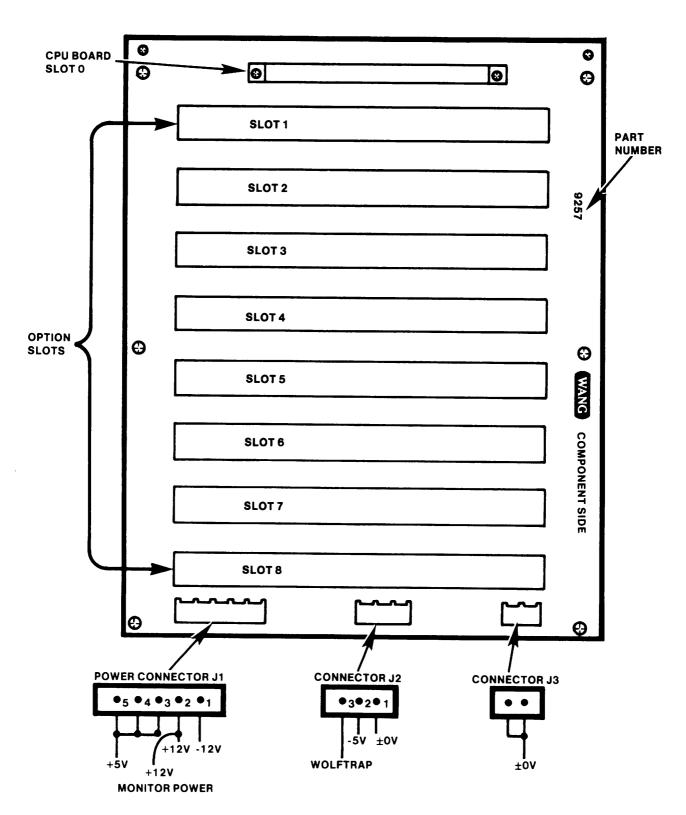

The 8221 CPU board contains the logic devices required for PC operations as well as the handshaking capabilities between option devices that can be installed to enhance the PC operating ability. The CPU board is installed in busboard slot 0 (J4) and can only be installed in that slot. The CPU board interfaces directly to the Low-Profile keyboard via connector J3, an optional parallel printer via connector J2, and a RS232 connector via J4.

The 8221 CPU board contains the 16-bit master CPU device 8086 and an optional co-processor 8087 operating at 8 MHz. The 8086 CPU provides a 16-bit bidirectional data bus and a 20-bit address bus.

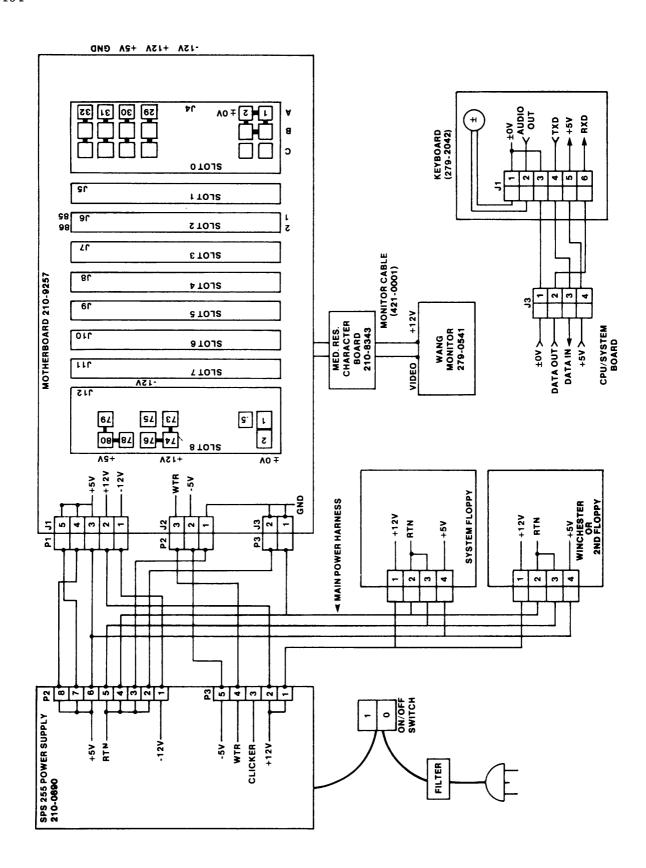

Figure 2-1. PC System Block Diagram

The 8086 CPU controls the bus except for the DMA transfers, which are controlled by the DMA logic (also located on the CPU board). The 8086 has direct addressing capability of one million bytes (1 Mbyte) of memory (location 0000H to FFFFH).

Also contained on the CPU board is 128K of parity-checked Dynamic Ram memory that can store system programs, application programs, or data. In addition to the dynamic RAM, two PROM devices contain the B.I.T. diagnostics and the bootstrap loader.

A 6402 UART is employed on the board to receive and transmit data to and from the keyboard. The CPU also contains the logic required to operate either one or two Floppy Disk drives.

The 8221 CPU board is discussed in detail in paragraph 2.3.

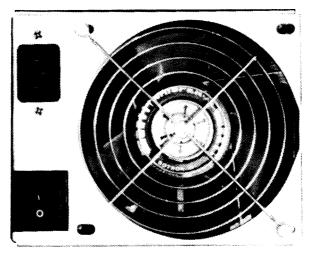

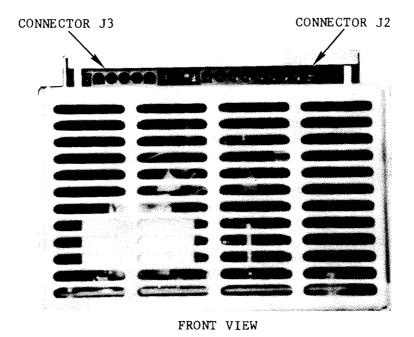

#### 2.2.2 SPS200 Power Supply

The SPS200 Power Supply is a switching power supply that is switch selectable for either 115 vac or 230 vac input voltage. This power supply provides four regulated voltages (+5, -5, +12, -12) required by the PC operating system. These voltages are supplied through the common bus to all option boards as well as cable-connected to the floppy drives (Winchester). Power required by the Wang Monitor and the Low-profile Keyboard are also supplied by this source.

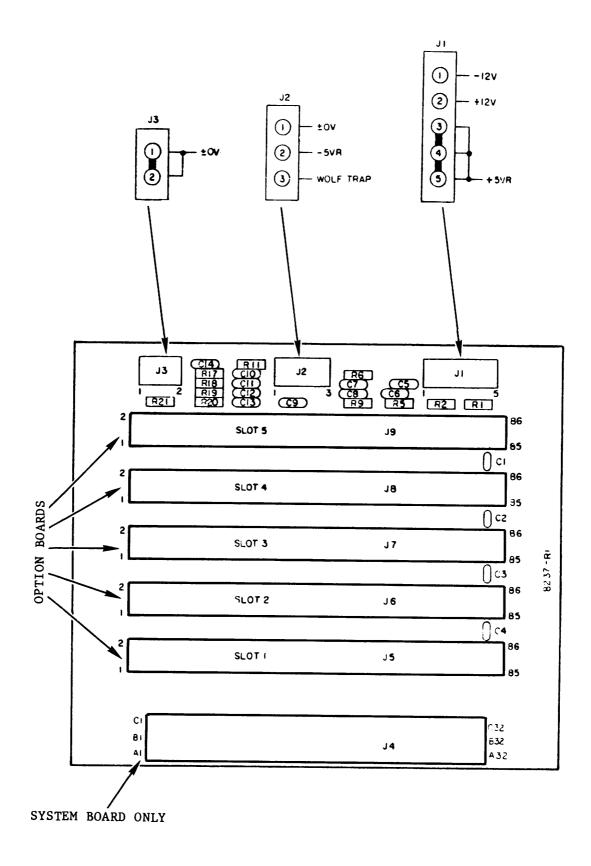

#### 2.2.3 8237 Motherboard

The Motherboard provides a common bus that extends the 20-bit Address bus, the 16-bit Data bus, and the 30-bit Control bus to the other five option slots. These option slots are prioritized with Slot 5 having the Highest priorty and Slot 1 having the lowest priorty. Also common bussed are the voltage levels required by the system.

A feature unique to the PC is the slot decoding scheme which is hard-wired on the Motherboard's option slots and read by a software routine to determine whether an option board is installed in each slot and if installed what the option is. This scheme is discussed in detail later in this chapter.

#### 2.2.4 360K Floppy Drive

The 360K Byte Floppy Drive presently used are Tandon and MPI drives operating MFM at 250 BPS (Bits per Second). The diskettes are 5 1/4 inch. Each diskette contains 40 tracks per side, double sided, with nine sectors per track. Each sector containing 512 bytes of data for a total of 368,640 bytes (360KB) of data per diskette.

The disk operating speed is 300 RPM  $\pm$  1.5% (300 RPM  $\pm$  45 RPM). The power requirements for the drive is +5 and  $\pm$  12 volts dc which is supplied by the PC's SPS-200 Switching Power Supply through the main harness assembly. See Figure 5-1 Power Distribution and Interconnection Diagram.

The system inputs and outputs data to the floppy drive. The floppy drive is a self-contained unit and is controlled by the CPU. Communications between the floppy drive and the CPU are via the Floppy Disk Controller chip which is located on the 8221 CPU board. Theory of operation of the floppy drive is not discussed in this manual. Refer to CE Reprint Manuals WLI No. 729-1167 for the Tandon Drive and WLI No. 729-1114 for the MPI Drive.

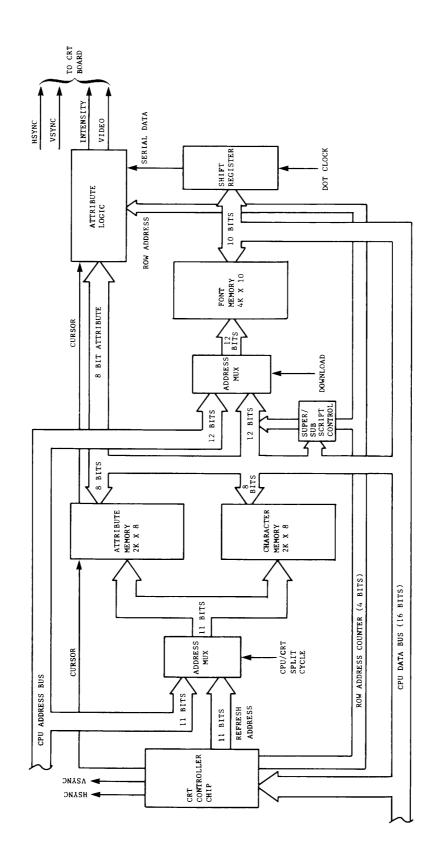

# 2.2.5 Medium Resolution Character Generator (210-8243/8343)

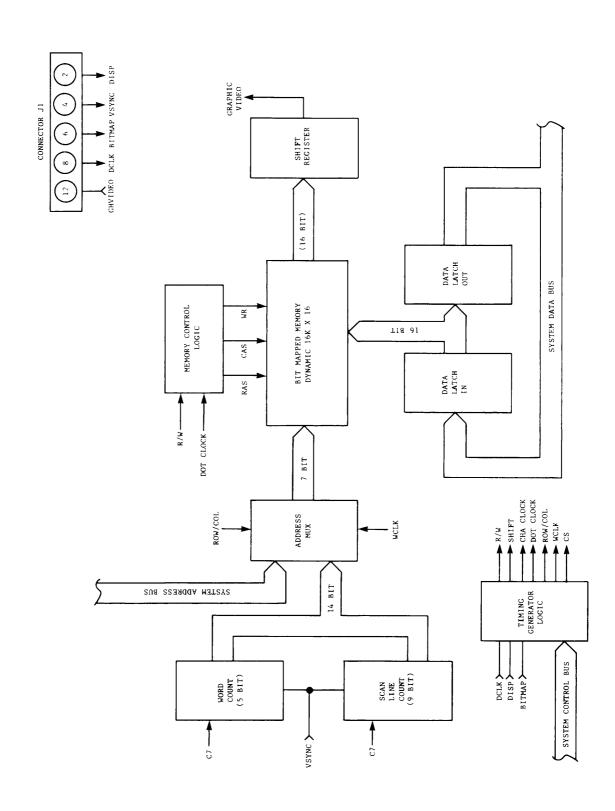

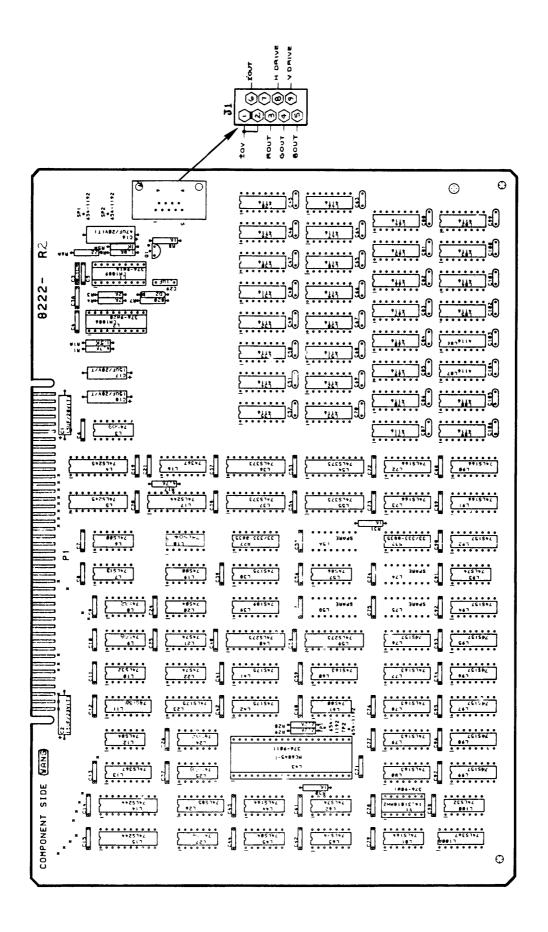

The medium resolution video controller produces TTL output to drive a Wang monochrome video monitor. Running at 18.824 KHz horizontally and 60 Hz vertically, the controller has 800 pixel by 300 pixel resolution when displaying either text characters or bit mapped dot graphics. The medium resolution video controller is under the control of the 8086 CPU device and is synchronized by the systems 8 MHz clock. An optional bit mapped graphics board, which must be paired with a character board via a ribbon cable, can be installed to produce bit mapped graphics. This board is discussed later in this chapter under Options (paragraph 2.2.8.2).

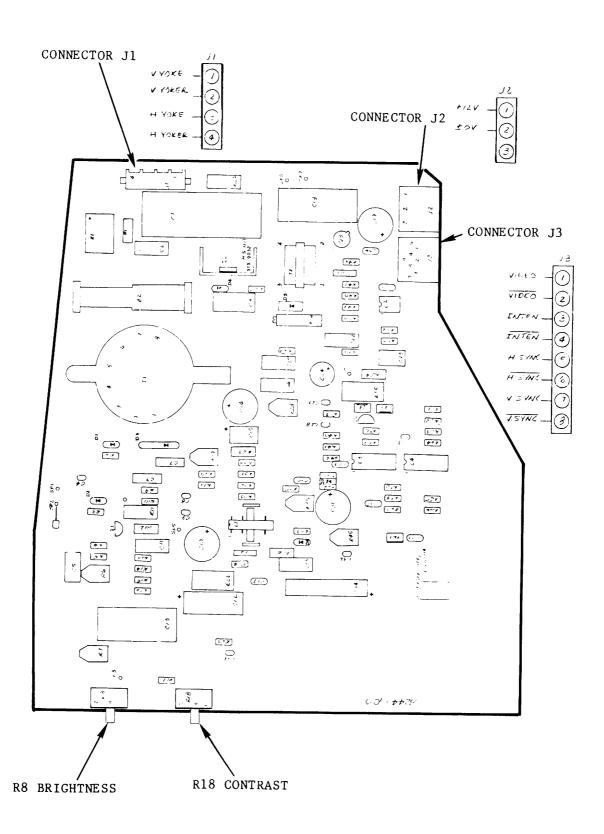

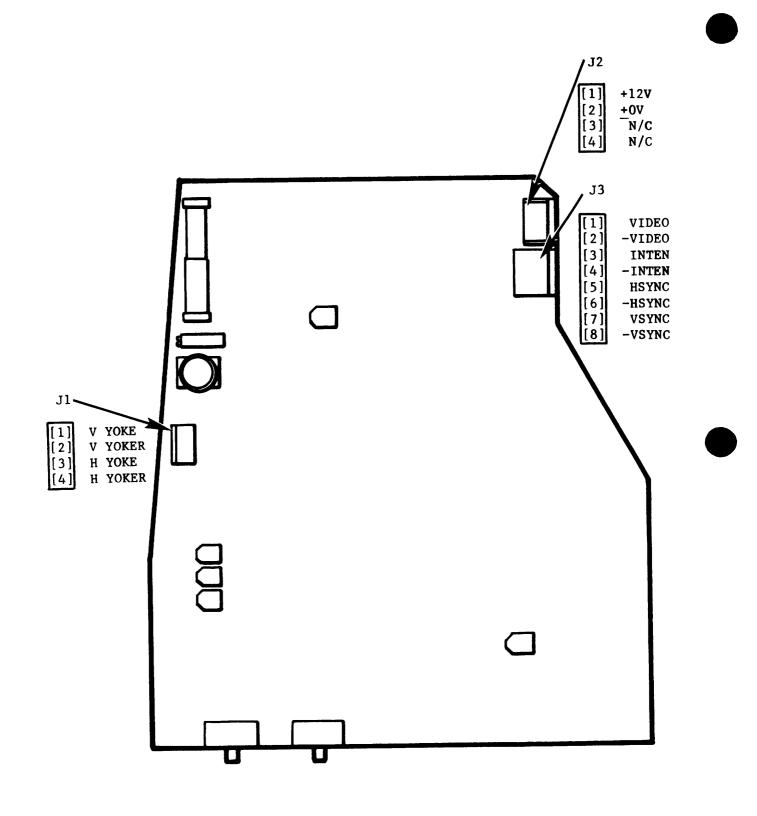

The 8243/8343 PCB is installed in any of the five busboard slots and is cable-connected to the Wang Video monitor via two cables. One cable (TTL Video) is an eight-pin barrel plug that provides the video signals to the Video Monitor. These signals include video, horizontal sync, vertical sync, and the intensity signals. The other cable (power) is a barrel plug that provides the power required by the Video monitor.

#### 2.2.6 Low-Profile Serial Keyboard

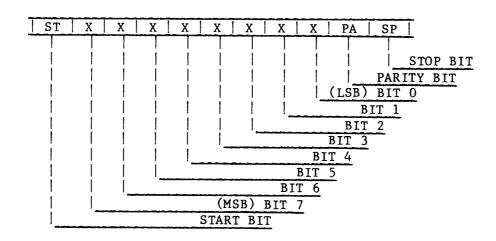

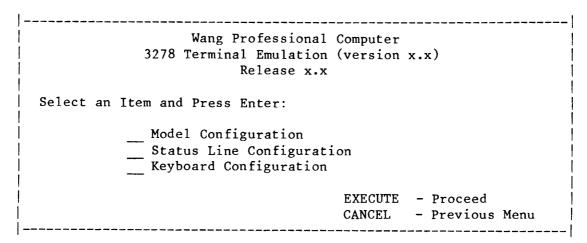

The Low-profile Serial Keyboard connects directly to the 8221 CPU board via the four-wire keyboard cable connected at the CPU connector J3. The keyboard cable supplies the +5 volts and ground as well as being the median for the transferring of the serial transmit data and serial receive data.